-

08-SDRAM:汇总

前言

推荐阅读:孤独的单刀 - SDRAM汇总篇

正文

一、SDRAM概念

1.1 含义

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器

同步:

动态:不断刷新保证数据的可靠性(电容存储电荷)

随机:1.2 版本

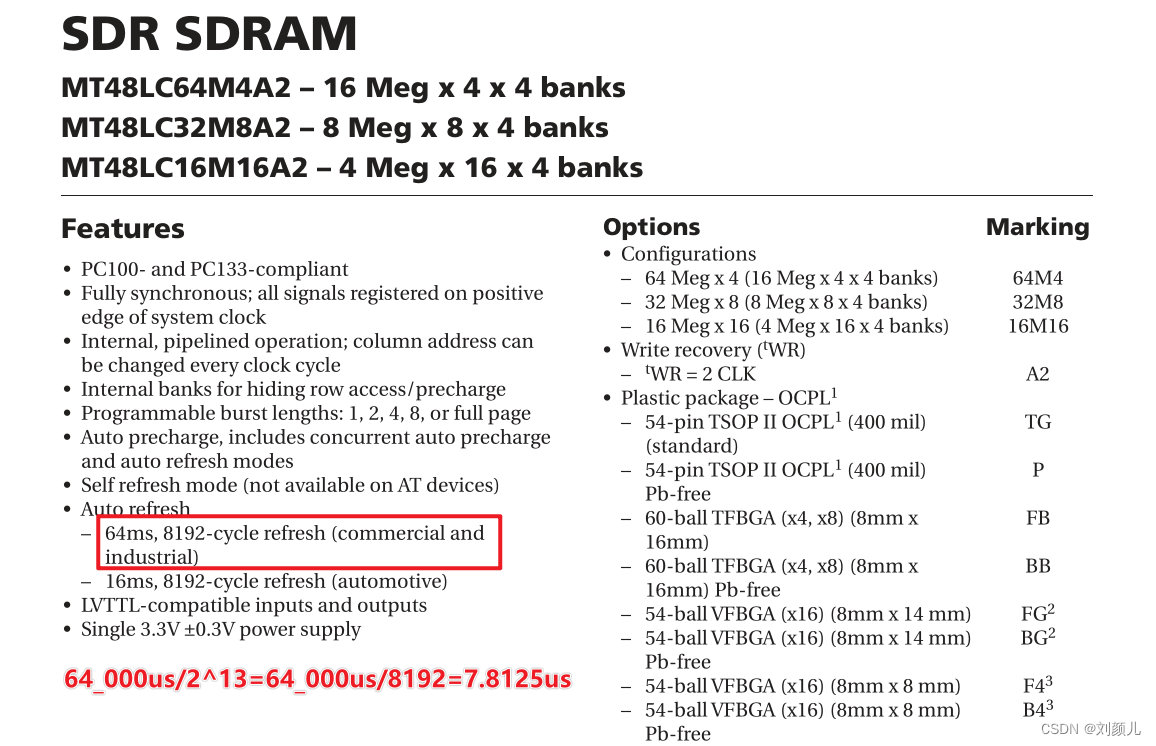

- SDR SDRAM:即常说的SDRAM,采用

单端时钟信号,在时钟上升沿采样 - DDR SDRAM

- DDR2 SDRAM

- DDR3 SDRAM

- DDR4 SDRAM

时钟信号:差分信号(抗干扰)

采样模式:时钟上升沿和下降沿都要采样

1.3 存储阵列

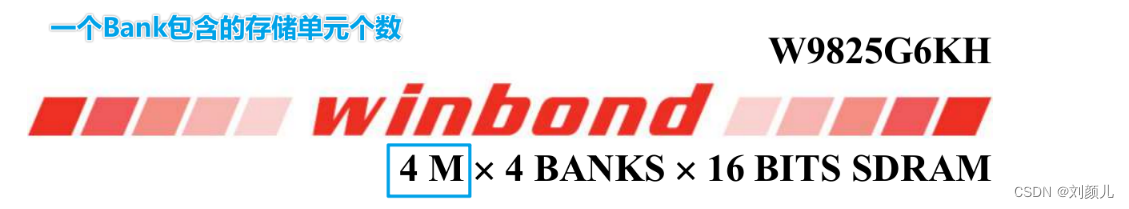

SDRAM中4个区域用存储,即4个Bank

SDRAM存储容量计算:

- 找到芯片手册中对应的行地址、列地址的位宽,下面图中Bank的行数=13,列数=9

- 假设每个存储单元可以存16bit的数据

- 计算公式:

(2^13) * (2^9) * 16 bit * 4 Bank = 256Mbit (单位是bit)

1.4 芯片引脚

CLK:时钟

CKE:时钟使能,高电平时,CLK才起作用RAS#:低电平有效,行选通信号

CAS#:低电平有效,列选通信号

这2个引脚共同使用A0-A12这13个引脚,分时复用WE#:使能写操作、预充电

CS#:片选信号,屏蔽或使能所有的输入输出端口SDRAM操作命令:CS#——CAS#——RAS#——WE#

BA[1:0]:Bank地址

A[12:0]:存储地址

DQ[15:0]:双向数据端口

1.5 操作命令

1.6 学习难点

主要体现在对控制时序要求很严格

1.6.1 由动态造成的难点

1.6.2 由随机造成的难点

行地址、列地址公用一个端口,分时复用

二、实验

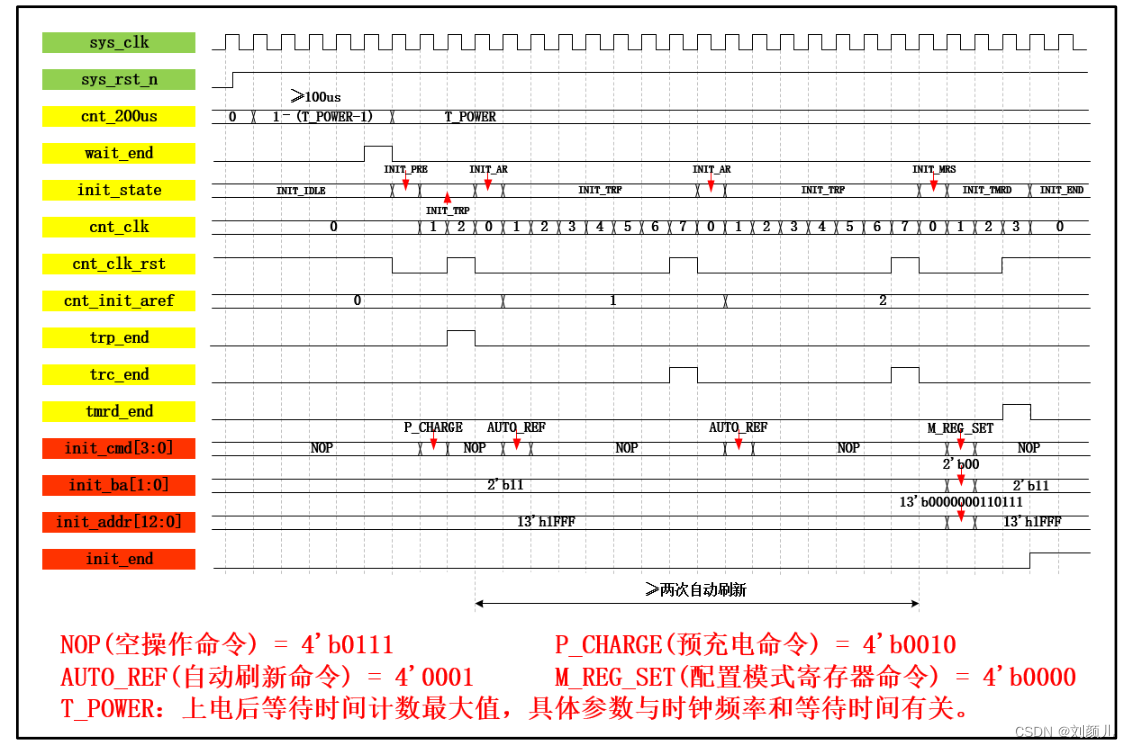

2.1 初始化

时序图来自镁光数据手册

波形图来自野火视频

2.1.1指令:

指令的写入只占用一个时钟周期

SDRAM初始化需要用到下面这4个指令共同完成

parameter P_CHARGE = 4'b0010 , //预充电指令 AUTO_REF = 4'b0001 , //自动刷新指令 NOP = 4'b0111 , //空操作指令 M_REG_SET = 4'b0000 ; //模式寄存器设置指令- 1

- 2

- 3

- 4

2.1.2 地址

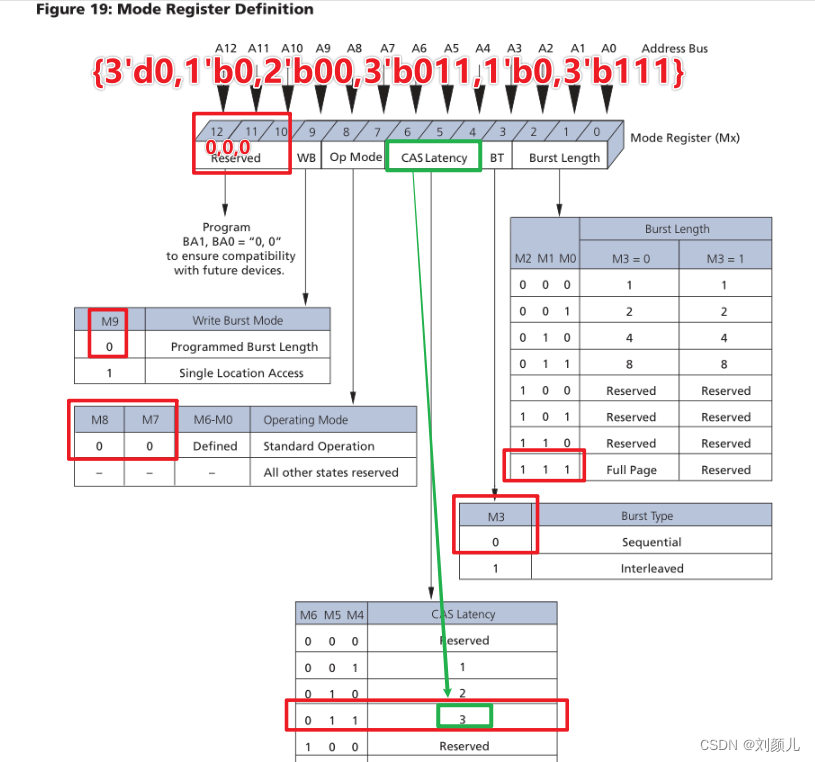

init_addr = {3'd0,1'b0,2'b00,3'b011,1'b0,3'b111};- 1

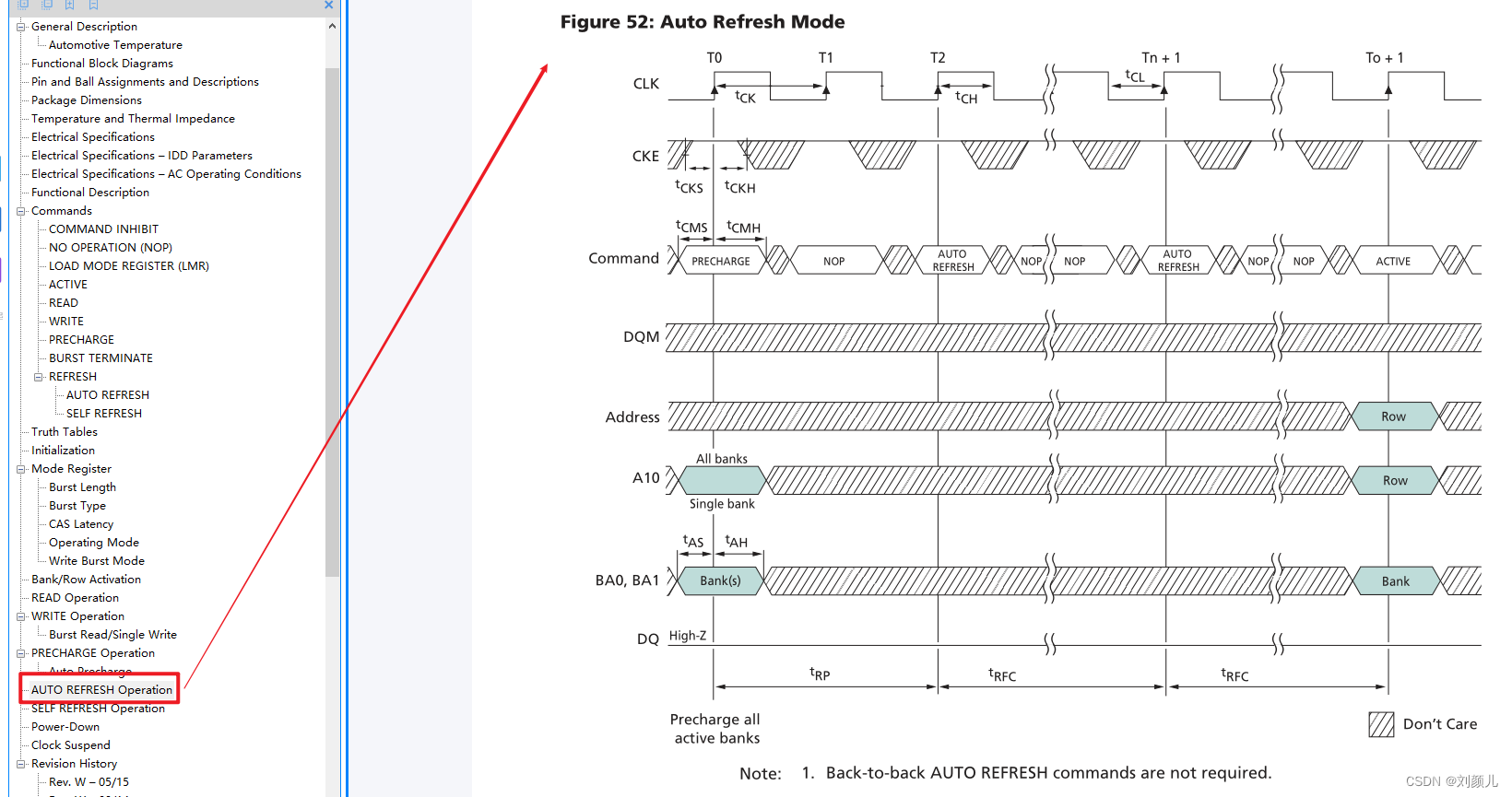

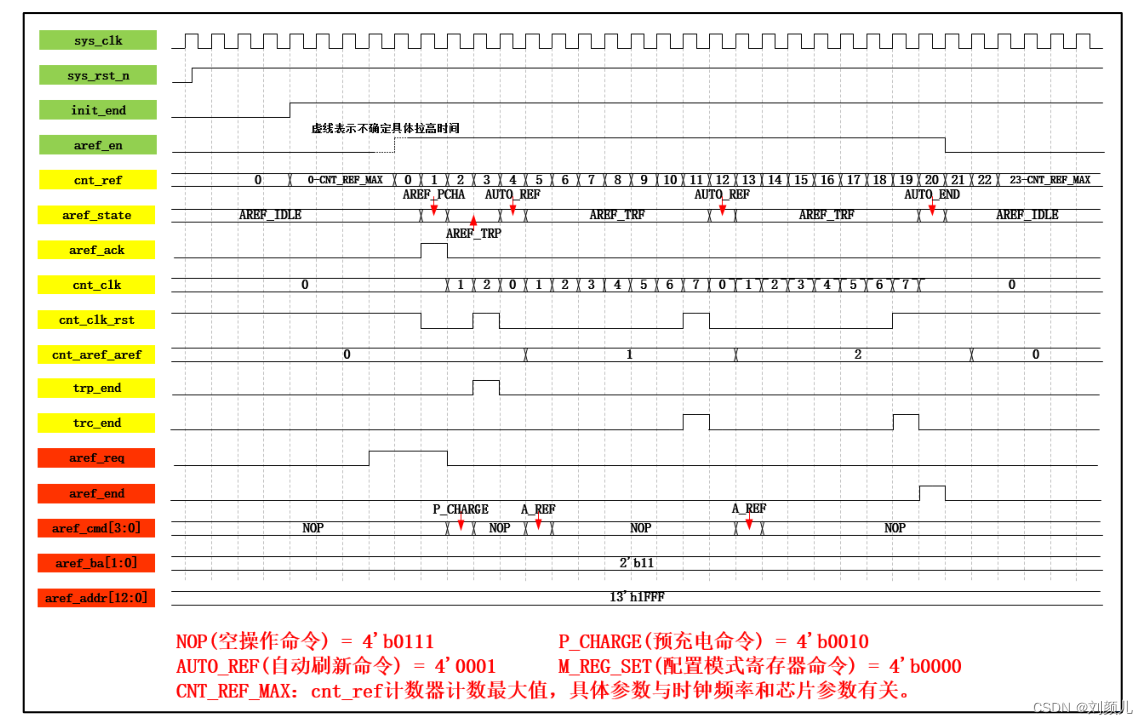

2.2 自动刷新(保证数据不丢失)

2.3 写操作(页突发)

突发模式:不带自动充电的页突发模式页突发的长度: 一行包含的存储单元的个数

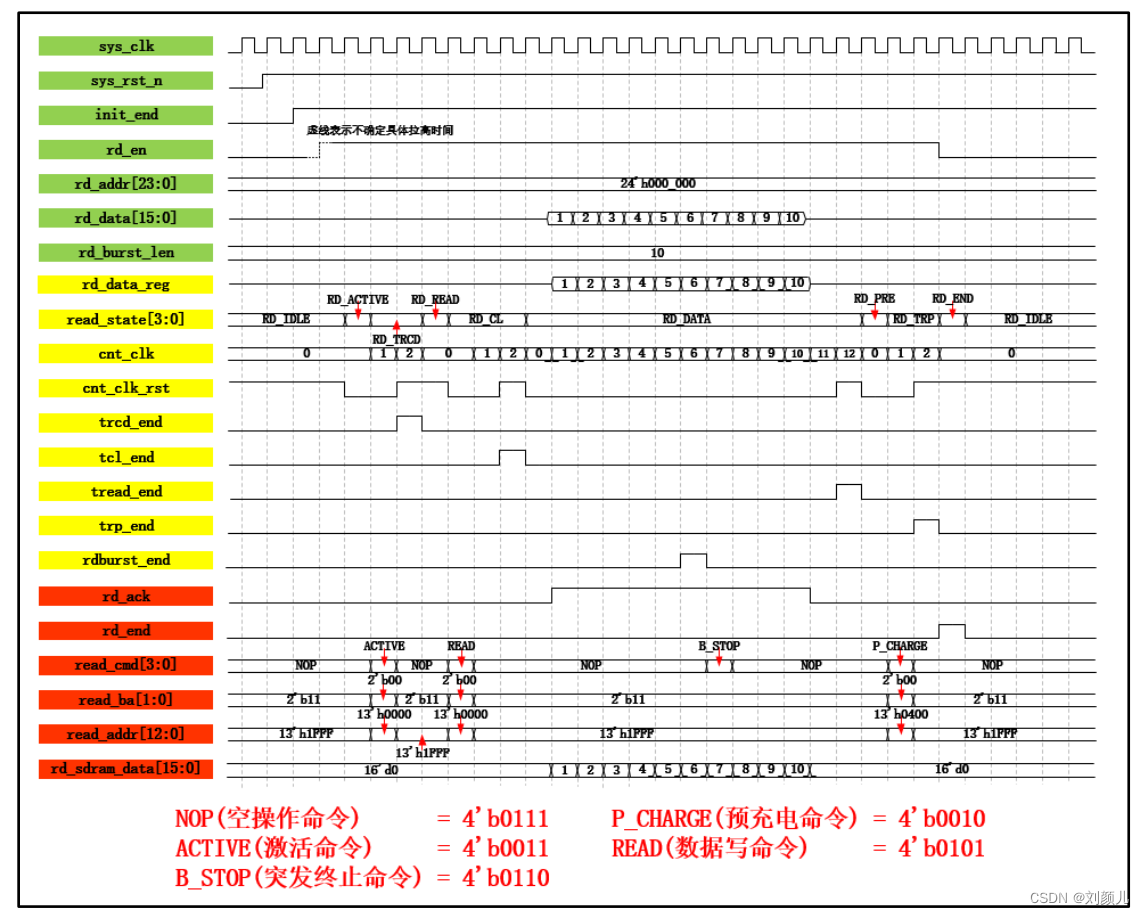

2.4 读操作(页突发)

突发模式:不带自动充电的页突发模式设置

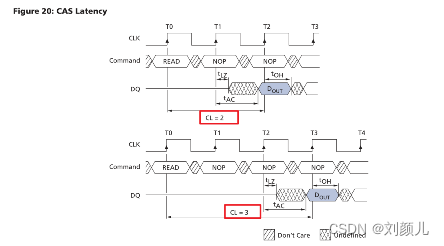

潜伏期

在初始化模块部分设置的3个潜伏期

于是在读数据部分,就需要用

突发长度+3来表示读数据的使用的周期

从SDRAM中读取的数据需要进行打拍,因为SDRAM的工作时钟和当前模块的系统时钟频率相同、相位不同2.5 仲裁模块

优先级:

自动刷新>写操作>读操作

2.6 SDRAM控制模块

2.7 FIFO控制模块

需要配置读写FIFO的IP核:FIFOIP核配置步骤

- SDR SDRAM:即常说的SDRAM,采用

-

相关阅读:

多尺度聚合GAN的未标定光度立体视觉

介绍事件“捕获”和“冒泡”执行顺序和事件的执行次数

Zookeeper 一、Zookeeper简介

说说Flink双流join

使用 Echarts 插件完成中国地图

《MySQL学习笔记》数据库增删查改(进阶)

kafka的安装和基本操作

BookxNote Pro 宝藏 PDF 笔记软件

学生HTML个人网页作业作品 使用HTML+CSS+JavaScript个人介绍博客网站 web前端课程设计 web前端课程设计代码 web课程设计

使用 VirtualBox+Vagrant 创建 CentOS7 虚拟机

- 原文地址:https://blog.csdn.net/m0_46830519/article/details/125873848