-

操作系统 -- cpu

cpu是什么?

CPU 是计算机的大脑,它主要和内存进行交互,从内存中提取指令并执行它

程序实际上就是一条条指令,程序的运行过程就是指令一步步的执行起来,cpu本质上就是执行指令;

cpu的组成

- 控制器 – 把内存中的指令, 数据等读入到寄存器中

- 寄存器 – 用来暂存指令数据等处理对象

- 运算器 – 负责运算从内存读入到寄存器的数据

- 时钟 – 负责发出cpu开始即使的始终信号

控制器

用于控制整个cpu的工作, 主要包含 指令寄存器(IR), 程序计数器(PC), 地址寄存器(AR), 指令编译器(ID)

指令寄存器(IR)

当cpu执行一条指令时, 先把他从内存储器到缓冲寄存器中, 在送入IR暂存, 指令编译器根据IR的内容产生各种微操作指令, 控制其他的组成部件工作, 完成所需的功能

程序计数器(PC)

pc具有寄存信息和计算两种功能, 又称为指令计数器, 程序执行分为两种情况 , 一是顺序执行, 二是转移执行, 当程序开始执行前, 将程序的起始地址送入pc, 该地址在程序加载的内容是确定的, 因此pc的内容即是程序第一条指令的地址, 执行指令时cpu自动修改pc的内容, 以便使其保持的总是将要执行的下一条指令的地址

地址寄存器(AR)

AR保存当前cpu所访问的内存单元的地址, 由于内存和cpu存在着操作速度上的差异, 所以需要使用AR保持地址信息, 直到内存的读写操作完成为止

运算器

算术逻辑单元(ALU)

ALU是运算器的重要组成部件, 负责处理出局, 实现对数据的算术运算和逻辑运算

数据缓冲寄存器(DR)

在对内部存储器进行读写操作时, 用DR暂时存放由内存储器读写的一条指令或一个数据, 将不同时间段内读写的数据隔离开来, DR作为cpu和内存, 外部设备之间的数据传送中转站

cpu处理指令的流程

- cpu先读取 “程序计数器” 的值, 即指令的内存地址, cpu的控制单元会操作地址总线指定需要访问的内存地址, 通知内存准备数据, 数据准备好后通过数据总线将指令数据传给cpu, cpu收到传来的数据, 将指令数据存入到指令寄存器

- cpu分析指令寄存器中的指令, 确定指令的类型和参数, 如果是计算类型的指令, 就把指令交给"逻辑运算单元"运算, 如果是存储类型的指令, 则由"控制单元"执行

- cpu执行完指令后, 程序计数器的值自增, 表示指向下一条指令

我们知道, cpu处理的指令是从缓存中获取的, cpu处理指令的速度非常快, 但是将指令从缓存中加载到寄存器中的速度相对来说是比较慢的, 那么怎么处理这个问题呢? 接下来就要引出缓存的概念了

寄存器/缓存/内存的关系

寄存器

寄存器是cpu的组成部分, 是一种直接整合到cpu中的, 有限的告诉访问速度的存储器, 他是有一些与非门组合成的, 分为通用寄存器和特殊寄存器, cpu访问寄存器的速度是最快的, 但是寄存器的容量非常小

缓存

缓存时cpu的一部分, 位于cpu中

在没有缓存之前, cpu一直都是在内存中读取数据的, 但由于两者速度差异, cpu每次都要等内存的’回信’, 缓存的设计是用来解决cpu与内存速度差异问题

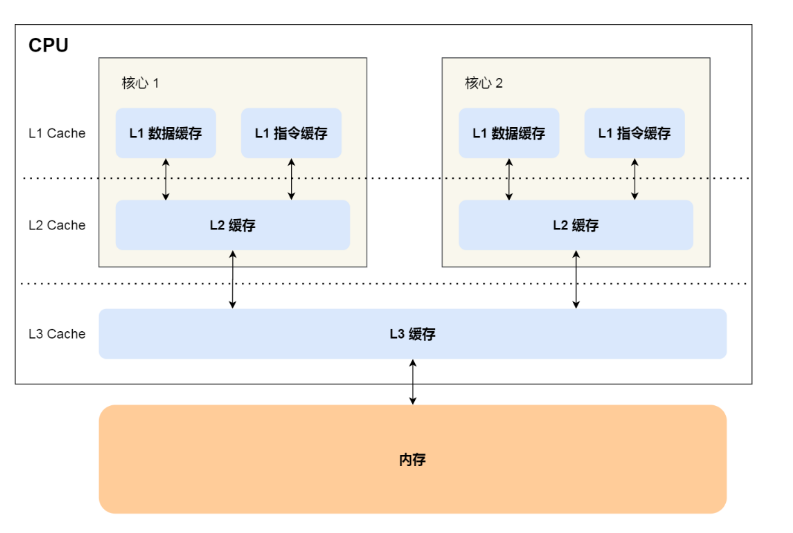

假设一个8核的cpu, 每个核都有自己独立的L1 Cache和L2 Cache, 而L3 Cache是8核共享的

缓存大小 : 离核心越近, 等级越高越小, 速度越快, L1 Cache缓存最小, 速度最快内存的数据会笑加载到共享的L3 Cache中, 在加载到每个核心独有的L2 Cache, 最后进入到最快的L1 Cache

内存

略

cpu从寄存器读取最快, 接下来是缓存 , 接下来是内存

工作状态

内核态

运行的程序的是操作系统,可以操作计算机硬件

在内核态运行的指令被称为特权指令, 能访问所有的内存空间和对象, 且所占用的处理机是不允许被抢占的

用户态

运行的程序是应用程序,不能操作计算机硬件

在用户态执行的指令叫非特权指令, 能访问的内存空间和对象收到限制, 处理机会被抢占

工作状态的切换

应用程序可以通过操作系统提供的一些api, 库函数来操作硬件, 实现由用户态转到内核态

比如发生缺页异常, 也会由用户态转化为内核态

为什么从用户态转化为内存态比较耗时呢 ?

因为涉及到了上下文切换

下一篇文章具体讲解cpu的上下文切换

-

相关阅读:

基于 NNCF 和 Optimum 面向 Intel CPU 对 Stable Diffusion 优化

Java集合框架

SOLIDWORKS --流体仿真篇

每天五分钟机器学习:支持向量机通过核函数解决线性不可分的问题

树状数组&线段树 的奇妙用法

1472:【例题2】The XOR Largest Pair——Trie树

Feign远程调用

算法刷题——二叉树部分操作(翻转二叉树,平衡二叉树,最大深度)

数分面试题2-牛客

JUC系列(九) CAS 与锁的理解

- 原文地址:https://blog.csdn.net/hc1428090104/article/details/126021360