-

带隙基准中运放相位裕度与增益裕度

参考:基准 stb

带隙基准包括两回路:正反馈回路和负反馈回路。电路要稳定就需要负反馈增益大于正反馈增益,STB仿真需要验证的就是这点,所以你需要做的是断开两个回路的公共节点进行环路稳定性仿真。

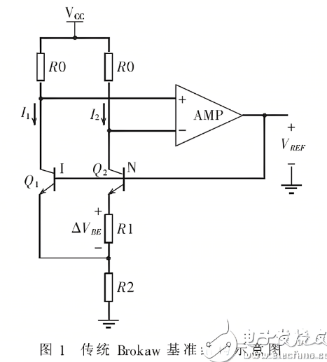

brokaw带隙基准

参考:请问带隙基准的STB仿真-brokaw带隙基准

Brokaw 带隙基准电压源电路可以看成是运算 放大器和以带隙基准核心电路为反馈的电路两部分 组成.这两部分电路不互为负载或者它们的输入阻 抗都很高的时候,可以独立分析.运算放大器具 有很高的输入阻抗,所以作为负载,它对带隙基准核 心电路的影响较小,同样,带隙基准核心电路的输入 电阻也足够高,使它对运算放大器的影响比较小,因 此,对这两部分电路可以进行独立分析.实际上,它 们之间会产生一些影响,下面针对运算放大器对基 准电路产生的影响进行一些分析.

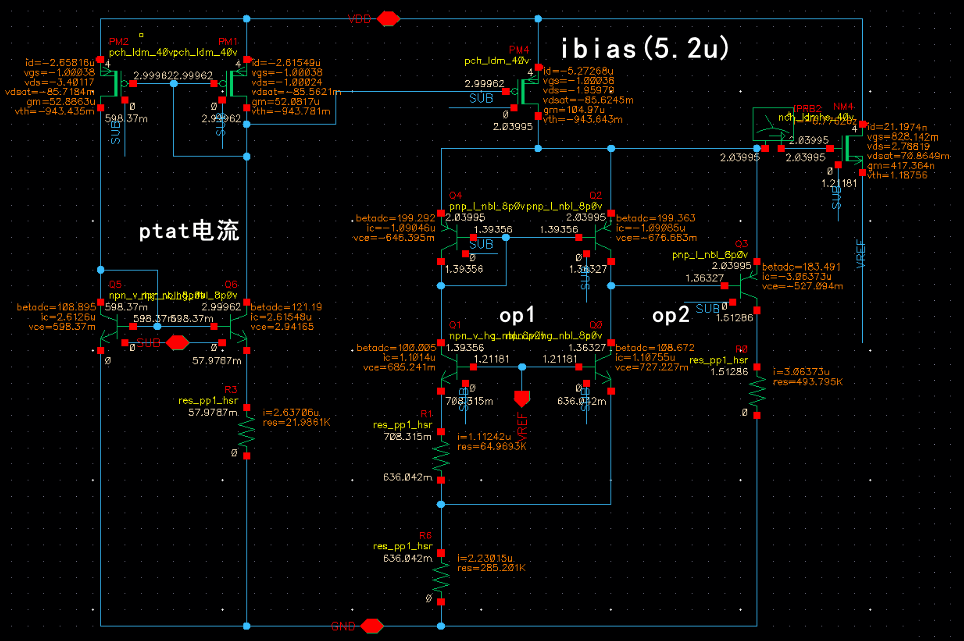

nA级别电流的那个管子是用来构成反馈回路的,因为电流小,所以工作在亚阈区。还有请问暂时没有启动回路会影响环路增益仿真嘛?

左边ptat电流,是不是接成正反馈了,应该没搭错吧,是负反馈。

ptat电流是负反馈没错,是因为射随器和vref处都为高阻抗节点,所以电路不稳定,在射随器加一个大电容就可以解决了。请问一下高阻抗节点什么意思,为什么高阻抗就不稳定了,试过AC仿真会出现同样的问题吗:

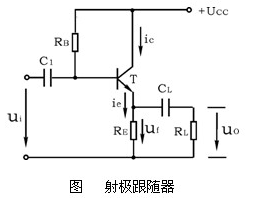

因为那个节点是主极点,在主极点处加一个大电容可以把主极点推向低频。比如你通过把主极点推向低频后,GBW的频率刚好在第二极点的位置,那么这个电路的相位裕度就是45度,这样你的环路就是一个稳定的状态。参考:射极跟随器

射极跟随器(又称射极输出器,简称射随器或跟随器)是一种共集接法的电路,它从基极输入信号,从射极输出信号。具有高输入阻抗、低输出阻抗、输入信号与输出信号相位相同的特点。射极跟随器(又称射极输出器,简称射随器或跟随器)是一种共集接法的电路,它从基极输入信号,从射极输出信号。具有高输入阻抗、低输出阻抗、输入信号与输出信号相位相同的特点。

这个电路以前是BCD工艺用的比较多吧,很老的结构了,需要电源电压很高;

bandgap的运放+红圈nmos+上边的PMOS组成两级米勒运放,输出给自己自偏置参考:带隙基准电路

测试电压源放在loop中的高阻节点.

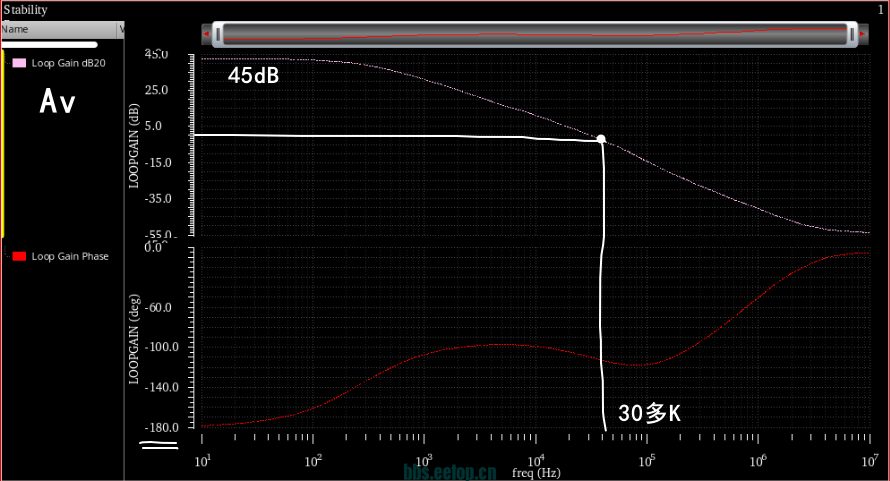

二级运放

参考:stb仿真求助

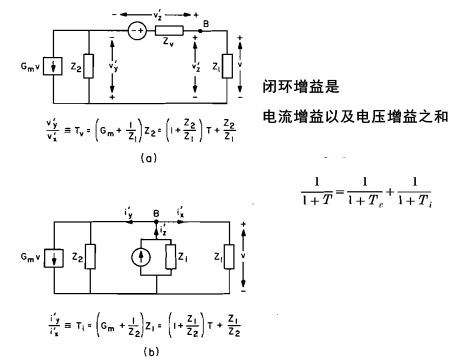

这样做的好处是交流断路,直流短路。另外LG的计算其中加入了电流增益的计算,比普通单仿电压gain的更可靠。你的电流增益我还是不太明白,有相关的资料吗? 或者就这个电路说说电流增益, 谢谢!

是的,Vds不一样,ro就不一样,增益就不一样,所以闭环往往仿出的增益更高。stb仿真本身基于一种理论,这种理论是以前一个国外模拟牛人发的一篇文章,我会去找找吧,你关注一下这个帖子,有进展了我发给你并把文章还有公式附上。也就是说:闭环仿真的时候,由于OP2的Vds会被拉高,id增加,则ro增加,所以仿真出来的环路增益相对较高。

提出这个方法的是Middlebrook先生

这篇文章的P499-500有这个公式的详细推导,有兴趣可以研究一下,呵呵。

参考:下载链接

楼主开环仿真,84dB,是不是你的AC信号幅度是3.5V呢? 84dB+20*log3.5=95dB, 考虑到图形的测量误差和94dB的结果很近了。这两种方法得到的结果应高是一致的,因为你的输出电压没有让输出级处于线性区,所以增益不会有什么差别。我也不懂,stb,不过好像就像先前某楼的同学说的,我对比过ac仿真结果跟stb仿真结果,低频段几乎一样,在高频段才出现偏差。不过貌似也不是太大。

STb仿真

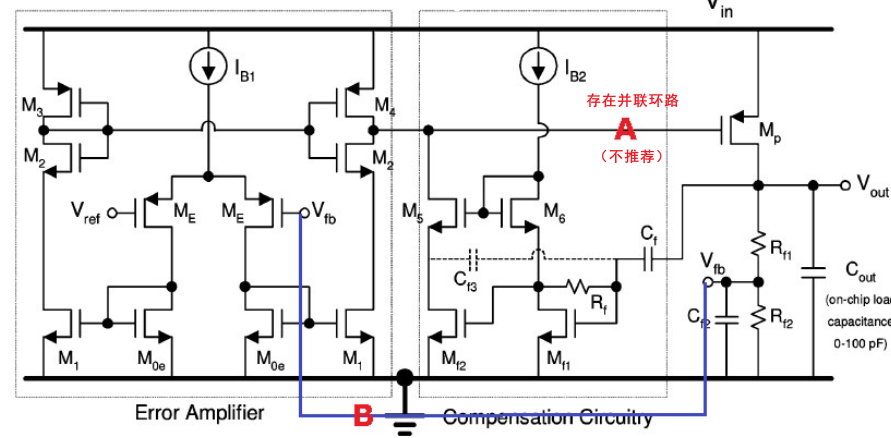

stb分析环路稳定性时一直把iprobe加在图上B的位置,但是看有人仿真ldo的稳定性时把iprobe加在pmos的gate也就是A的位置,现在有点迷惑,两个位置仿真结果差别很大,请教大家应该在哪里加iprobe?

应该是B而不是A,确切说A是错误的,因为从A断开时,仍然有其他的并联的反馈路径存在于环路中(也就是断开B也没有断开它),因此probe得到的反馈不能反映系统全部。至于其他反馈路径lz可以自己找找哦。

而从B断开,不管有多少并联路径,最后都从B点统一被cut掉了。

应该放在B点更合适些,如果放在A点,极点A的阻抗与电容被分割开了

从你的仿真结果来看,B点应该是更合理的。因为A点是主极点所在位置(ro),你的下图仿真结果显示主极点要比上图的要低。具体原因,或许如楼上所说!

也就是说在B点引入后,会使得输出主极点降低。

个人觉得是B,A点断开就破坏了电容的补偿效应上周在仿真共模环路时遇到同样的问题,我的电路是:普通电阻去共模,然后放到一误差放大器内,随后经误差放大器反馈回主运放的尾管。

在STB时现象和楼主类似,在B点(等价位置)曲线比较合理,然而在A点(等价位置)曲线比较难看(感觉不对)。

个人感觉楼上从阻抗的变化上看 ,有道理,LZ怎么看?也就是闭环的仿真会增加电流增益的变话。更接近。(ro这增加,高增益,低频主极点。)B点正确,是所有的反馈环路在B点被cut了。

加在B点,这添加位置应该是高输入阻抗点(因为高输入和别的并联后,忽略不计,所以对该极点影响忽略),并且是大电容点(同样的道理,输入端的电容相比该节点的大电容可忽略不计)

【第一张图,我可以肯定的说,断开A点是对的,断开B点是错的。

是否对错,可以拿AC分析和tran进行对比, 也可以流片验证两种方式。。。。

某些参数下,你可以发现断开B点的AC仿真,PM足够,但断开A点,PM是负的,用tran仿真,就看到震荡!

我坚信和tran能够对应的才是对的,实测也是如此。】

lz给了两个图。对于运放,B对。对于LDO来说A对。区别在于前一个电容是双向的,后一个可以认为cf是单向的。

我觉得你说的有道理,所有反馈通路都应该经过iprobe,而B点确实只有其中一条反馈通路经过。这样来看,A点是放置iprobe正确的位置。

如果认为第二个电路中包含Cf的反馈通路是单向导通的,其原因应该是从A点看反馈通路的阻抗很大;同样,第一个电路中从A点看包含米勒电容的反馈通路阻抗也很大,所以个人认为第一个电路中包含米勒电容的反馈通路也可以认为是单向导通的,不知道我的想法是否正确。最近的想法又变了。如果真要严格一些,即使最简单的miller op都是多环路,我们平时断环位置也不能反映真正的环路特性。换句话说,在哪里断,其实目前是个工程问题。

为什么这么多人说断在A点是错呢。。。。 实在不能理解,一般断在A点更方便design

【第二种图,我认为断开A或者B都是错误的】从信号流图角度分析:

开环仿真

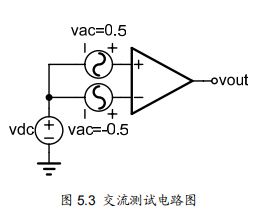

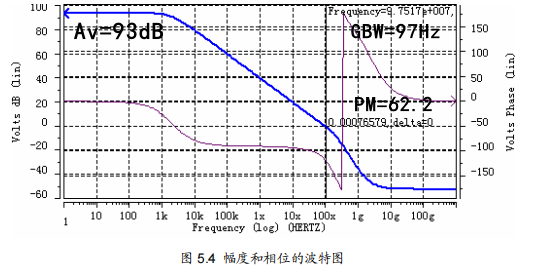

交流测试的 testbench 如图 5.3 所示。这是一种差分测试的 testbench,还有一种方法是把 ac 信号全部放在一个输入端(或正端或负端),使用 Hspice 的 pz 分析可以观察出,这三种方法得到的零极点不完全一致甚至有不小差别。最终采取图 5.3 的方法进行测试。

可以看到LDO的类型用B类的stb可以,但是B类的AC显然。好像,不太行。 -

相关阅读:

刘强东卸任京东集团 CEO,徐雷接任;苹果新专利可为多个设备无线充电;Rust公布2024年路线图|极客头条

网络PXE启动WinPE,支持UEFI和LEGACY引导

文未有福利 | 接口自动化你不懂?听HttpRunner的作者怎么说

不想花大价钱?这10款替代Axure的平替软件更划算!

C# xml序列化以及遇到的坑

R语言dplyr包select函数筛选dataframe指定数据列,sample_n函数采样指定个数数据行

socket套接字函数

服务器中jdk、mysql的安装配置,以及linux一些使用的操作

项目立项管理

Zabbix之部署代理服务器

- 原文地址:https://blog.csdn.net/Carol0630/article/details/125885371