-

【蜂鸟E203的FPGA验证】Chap.9 FPGA平台硬件验证

前言:本文均为作者原创,内容均来自本人的毕业设计。未经授权严禁转载、使用。里面的插图和表格均为作者本人制作,如需转载请联系我并标注引用参考。分享仅供大家学习和交流。

DDR200T开发板

FPGA(Field Programmable Gate Array,可编程阵列逻辑)常用作流片(tape-out)之前的验证所设计的处理器是否能正常工作的测试手段。FPGA内部利用了其基本可编程逻辑单元可以多次编程、生成比特流文件后烧录下载到 FPGA中。

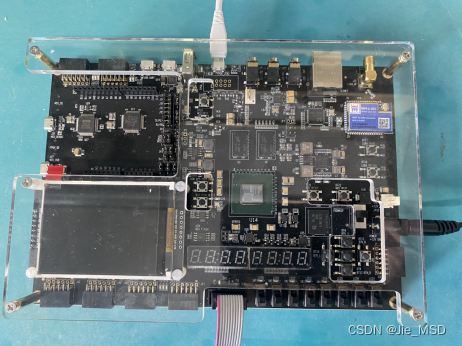

本设计采用芯来科技公司的Nuclei DDR200T开发板作为单核32位RISC-V处理器的硬件测试平台,搭载着Xilinx XC7A200TFBR484-2 FPGA核心,如图3-23所示。

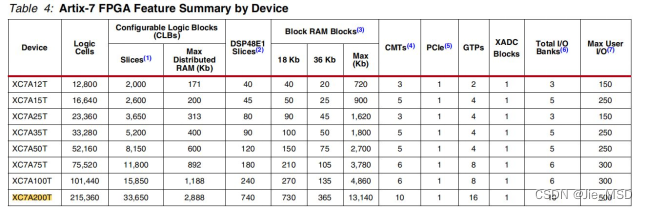

图3-23 Nuclei DDR200T开发板 XC7A200TFBR484-2型号的FPGA功能丰富,资源上满足处理器测试的条件,如图3-24所示。具有以下的资源:

- 具有215360个基本逻辑单元(Logic cells),每个基本逻辑单元包含1个查找表LUT、1个触发器FF,查找表使用组合逻辑可实现1个逻辑表达式;

- 具有33650个逻辑片(Slices),每个逻辑片有8个FF,即寄存器数目Slice Registers = 8×33650=269200;每个逻辑片中有4个6-input LUTs,即LUTs=4×33650 = 134600;

- 具有10个时钟管理模块(CMTs),每1个CMT由1个MMCM和1个PLL组成,用作时钟频率生成;

- 具有740个数字信号处理模块(DSP48E1 Slices)。

图3-24 XC7A200TFBR484-2型号FPGA的资源图 使用Vivado烧录FPGA

建立Vivado工程的详细步骤可见之前的博客

Vivado 蜂鸟 e203 MCU200T/DDR200T 逻辑综合 RISC-V 详细教程 https://blog.csdn.net/qq_43858116/article/details/123648746 Vivado 蜂鸟 e203 烧录下载MCU200T/DDR200T FPGA-FLASH里 bit/mcs/bin文件 详细教程 RISC-V https://blog.csdn.net/qq_43858116/article/details/124152615- 1

- 2

- 3

- 4

- 5

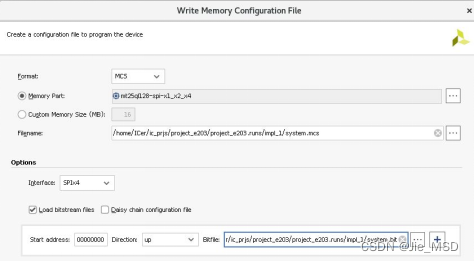

FPGA配置就是把配置数据通过外部控制电路加载到FPGA内部的FPGA的FLASH中的过程。打开Vivado 硬件管理里的Write Memory Configuration File工具,用于生成MCS、BIN文件,通过开发板原理图可知FPGA的FLASH型号为mt25q128,选中后可用于产生存储器配置文件,用于配置FPGA。Write Memory Configuration File工具生成MCS文件如图3-25所示。

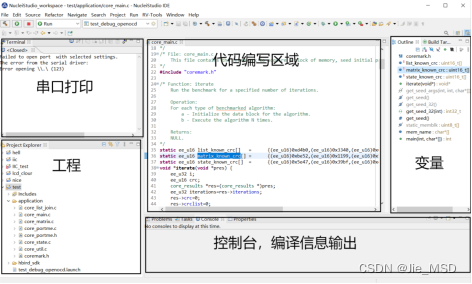

图3-25 生成MCS文件 本设计采用芯来科技的Nuclei Studio的编译器,基于开源的Eclipse框架,提供了非常易用的针对RISC-V处理器开发的IDE集成开发环境[18]。建立新的C++/C工程后就可以在Nuclei Studio编译器里编写C++/C程序,编译器会自动将程序翻译成所设计的基于E203内核设计的单核32位处理器的底层汇编程序,最终生成满足RISC-V指令集架构的运行指令。

Nuclei Studio的IDE环境如图3-26所示。调试RISC-V处理器的方式主要通过GDB和Openocd工具的方法。其中,GDB(GNU Project Debugger),是一款成熟的调试工具,能够用于调试C、 C++等语言编写的程序。GDB也用于下载程序、查看通用寄存器的值或内存地址的值等。第二,OpenOCD作为GdbServer与GDB进行配合的桥梁,能够支持Nuclei Studio的IDE环境下使用GDB调试处理器。

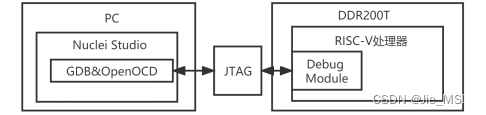

图3-26 Nuclei Studio编译器 由于已经将设计好的单核32位RISC-V处理器固化烧录到DDR200T开发板上的FPGA核心内,JTAG支持了使用GDB将程序动态下载到处理器中运行。JTAG的I/O经过物理约束文件连接到了RISC-V处理器的JTAG的pin脚上,JTAG调试器的另一端连接PC端的USB端口,其内部模块的连接图如图3-27所示。

图3-27 JTAG调试的连接 跑分测试

处理器的Benchmark测试,一般也称为“跑分”测试,在处理器完全执行一组标准程序的“运行分数”测试后,它是通过执行速度评估处理器分数来衡量处理器性能的指标。本节主要介绍在FPGA原型平台上运行CoreMark、Dhystone 的“跑分”测试程序。

CoreMark

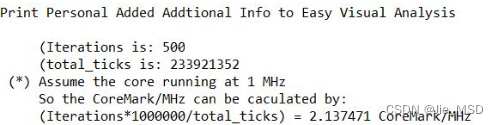

CoreMark是一套用C语言编写的标准软件程序,其中包含了嵌入式处理器领域的许多典型算法。处理器在一定主频下每秒可执行CoreMark程序的周期数用作衡量处理器性能的标准,是CoreMark跑分的运行得分,即单位为CoreMark/MHz[19]。在FPGA上板后,运行CoreMark程序编译下载到处理器内部,最后通过Nuclei Studio编译器的串口打印将运行CoreMark程序的信息打印出来,如图3-28所示。

图3-28 CoreMark跑分测试结果 从图中可以看出,执行CoreMark程序的周期数为500,且在FPGA上以16.667MHz的主频运行CoreMark程序,即分数为2.2137 CoreMark/MHz。

Dhystone

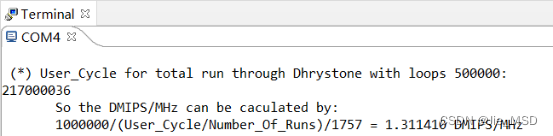

Dhystone是一个综合的处理器跑分程序,它的主要目标是测试处理器的整数操作和逻辑操作的性能,有着众多不同类型程序的典型方法,如函数调用、间接指针、赋值等。得分的基准是处理器能够在每秒执行的Dhystone主循环的次数。因为早期的VAX11/780型处理器能够达到的性能为1757每秒Dhystone次主循环,故业界一般以Dhystone Per Second除以1757所得值为1DMIPS为标准,其他处理器的跑分测试便以Dhystone Per Second除以1757再除以处理器主频作为跑分测试的结果。Dhystone 跑分测试结果如图3-29所示。

图3-29 Dhystone跑分测试结果 如图3-30所示,Dhystone程序的结果被打印到计算机端的串行端口中,执行Dhystone 程序循环次数为500000次,即得分为1000000 / (217000036/500000) / 1757= 1.311410DMIPS/MHZ。

在程序由不同处理器架构的编译器编译后,生成的汇编代码的数量级可能会有很大差异,从跑分测试的得分可以看出RISC-V精简指令集架构的E203内核处理器有着优秀的性能,如表3-3所示。经测试所设计的E203内核处理器的CoreMark跑分测试的得分接近ARM Cortex-M0+的得分,Dhystone跑分测试的得分强于同款的ARM Cortex-M0+处理器。跑分测试结果表面,E203内核的处理器在低功耗、小面积的嵌入式领域可以有效替代ARM Cortex-M0+型号处理器。表3-3 处理器跑分对比 E203 Cortex-M0 Cortex-M0+ Cortex-M3 Cortex-M4 Cortex-M7 Rocket Core-RV64I CoreMark(MHz) 2.14 2.33 2.46 3.34 3.42 5.01 2.32 Dhystone(DMIPS/MHZ) 1.23 0.87 0.95 1.25 1.25 2.14 1.72 -

相关阅读:

《异常检测——从经典算法到深度学习》27 可执行且可解释的在线服务系统中重复故障定位方法

利用衍射表面消色差的混合目镜建模

vue入门简单学习

两日总结十六

CDR最新CorelDRAWX8安装步骤教程

Day774.能向 Redis 学到什么 -Redis 核心技术与实战

防止PDF 盗版

SQL Server 中的 ACID 属性

论文管理系统(登录功能)

AI创作系统ChatGPT源码+AI绘画系统+支持OpenAI DALL-E3文生图,可直接对话文生图

- 原文地址:https://blog.csdn.net/qq_43858116/article/details/125519934