-

Verilog 的层次化事件队列+阻塞赋值与非阻塞赋值理解

在IEEE1364—1995 Verilog标准的5.3节定义了层次化的事件队列在逻辑上分为用于当前仿真时间的4个不同的队列,用于下一段仿真时间的若干附加队列。

(1)动态事件队列(下列事件执行的顺序随机安排)

① 阻塞赋值;

② 计算阻塞赋值右边的表达式;

③ 连续赋值(对wire型变量用assign赋值);

④ 执行$display命令;

⑤ 计算原语的输入与输出变化。

(2)停止运行的时间队列: #0 延时阻塞赋值。

(3)非阻塞事件队列:更新非阻塞赋值语句LHS(<=左边的变量)的值。

(4)监控事件队列:

① 执行$monitor命令;

② 执行$strobe命令。

(5)其他指定的PLI命令队列:其他PLI命令。

下面用一张图来表示:

动态事件就是活跃事件,它们的优先级最高,在当前的仿真时间中,活跃事件最先被执行。

上图可以看出,阻塞赋值是活跃事件,当前仿真时间中它最先被执行,阻塞赋值执行完RHS(右式计算)后,立刻赋值给LHS。并且在执行阻塞赋值期间,不允许其他语句干扰。对于非阻塞赋值,RHS是活跃事件,最先执行,但执行完后并不急于赋值,而是在事件队列列表中等待,等到后期仿真快要结束时再执行。

阻塞赋值特点:

(1)阻塞赋值可以认为只有一个步骤操作,即计算RHS并更新LHS,此时不允许有来自任何其他的Verilog语句的干扰。

(2)在同一个always块中,只有前面一条阻塞赋值语句执行完之后,才开始执行下一条。(这就是所谓阻塞的概念)。

非阻塞赋值特点:

非阻塞赋值可以看成是两个步骤:①在赋值开始时刻,计算非阻塞赋值RHS表达式;②在赋值结束时刻,更新非阻塞赋值LHS表达式。

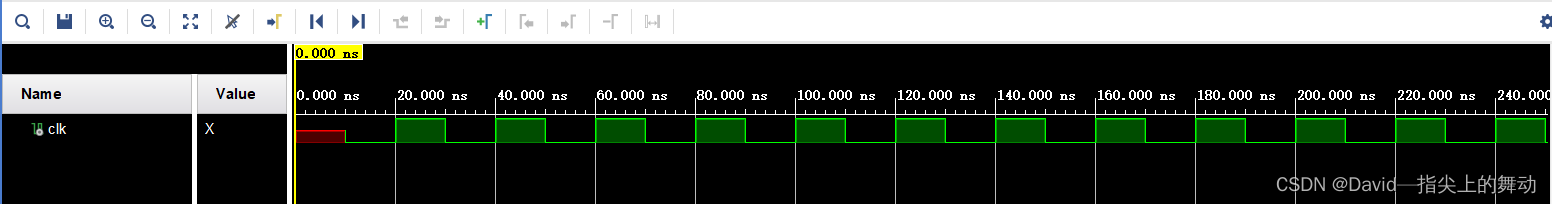

使用阻塞赋值不能进行自触发的振荡器

- module learn(

- output clk);

- reg clk;

- initial #10 clk = 0;

- always @(clk) #10 clk = ~clk;

- endmodule

在initial块中,经过10个单位时间的的延时,clk被立即阻塞赋值为0。当clk=0发生时,触发@(clk),经过10个单位的延迟,计算RHS(~clk)得到1,并立即更新LHS的值,clk被赋值为1。由于此过程不许被打扰,所以当always回到判断触发条件@(clk)时,此时clk电平已经为1,但是对于always而言,并没有感知到clk从0到1的变化,因此对于always而言,认为该clk并没有发生变化,所以就阻塞在那里,不触犯@(clk)条件。所以,clk翻转一次后不再变化。

使用非阻塞赋值的自触发振荡器

- module learn(

- output clk);

- reg clk;

- initial #10 clk = 0;

- always @(clk) #10 clk <= ~clk;

- endmodule

@(clk)第一次触发后,非阻塞赋值的RHS表达式便计算出来了,并把值付给LHS的事件安排在了更新事件的队列中。在非阻塞赋值更新事件队列被激活前,又遇到@(clk)触发语句,并且always块再次对clk的值变化产生反应。当非阻塞LHS的值在同一时刻被更新时,@(clk)再次触发。

参考文章:

-

相关阅读:

苍穹外卖day10(2)WebSocket、来单提醒、客户催单

Vue/ Vue ELement框架、表单效验正则属性、兜底效验(点击登录后会验证文本框是否满足条件)

Vue绑定样式

mnist数据集

1111111111111

virsh管理虚拟机的命令行工具

Redis 持久化之 RDB 与 AOF 详解

linux命令汇总

向量三重积的等式推导证明

vuedraggable影响点击事件的解决办法

- 原文地址:https://blog.csdn.net/weixin_43093226/article/details/125510701