-

【蜂鸟E203的FPGA验证】Chap.5 基于E203内核的处理器验证+ 基于FPGA的处理器设计与验证流程

前言:本文均为作者原创,内容均来自本人的毕业设计。未经授权严禁转载、使用。里面的插图和表格均为作者本人制作,如需转载请联系我并标注引用参考。分享仅供大家学习和交流。

总结

本设计基于E203开源内核,在充分地分析与掌握其源代码的基础上,基本掌握RISC-V指令集架构和E203内核的硬件结构。由于E203内核提供了开源的设计源码,本设计便基于此内核利用Iverilog工具完成了RISC-V基础指令集的测试、仿真E203内核流水线的信号、利用Vivado进行逻辑综合和布局布线、对形成的综合后报表进行分析、将设计好的单核32位RISC-V微处理器烧录到Nuclei DDR200T开发板(使用Xllinx公司Artix-7的FPGA核心)进行板载测试。具体内容在本章进行论述。

基于FPGA的处理器设计与验证流程

随着FPGA的工艺、功能不断发展,芯片设计验证工程师将设计好的RISC-V处理器以IP软核的形式移植到 FPGA,用于验证、测试和性能分析等。FPGA 平台可以同时满足芯片设计开发人员的需求,并且比使用传统的ASIC验证、设计周期要短得多,同时还能提高一次流片成功率。

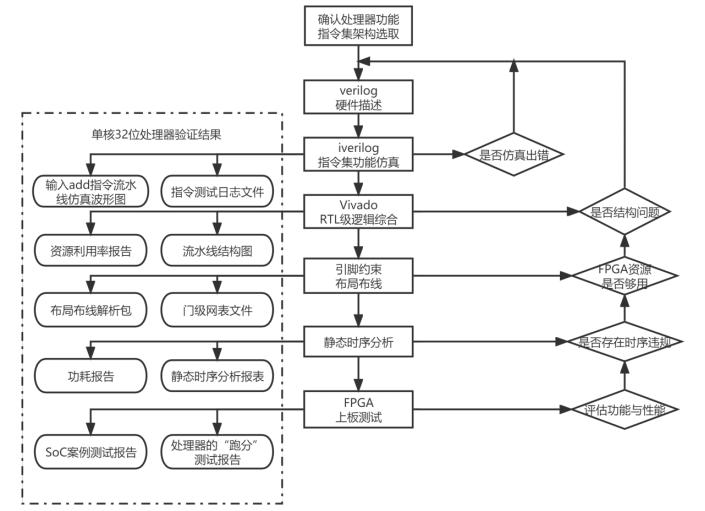

本设计的处理器设计验证方法基于FPGA平台实现,将设计好的RISC-V处理器以IP软核的形式移植到 FPGA,用于验证、测试和性能分析等。设计流程如图3-1所示,共包括八个步骤。首先需要明确处理器的功能和指令集框架的选取,接下来依次进行硬件描述、指令集功能仿真、RTL级逻辑综合、布局布线引脚约束、静态时序分析、FPGA上板测试[16]。

图3-1 基于FPGA的处理器设计与验证流程 1. 确定处理器功能与指令集架构选取

首先明确处理器所可以实现的具体功能和相关性能要求,针对需求和设计的复杂程度考虑指令集架构的选取。本设计想设计一款单核32位的处理器,故选用RISC-V架构的E203内核。其设计理念包括:模块化的设计、可重用的执行模块,系统性能不追求极端提倡够用即可[7],因此E203内核处理器在面向AIoT领域的低功耗处理器表现很好。

2. Verilog硬件描述

处理器系统设计一般要先选定一个硬件描述语言,根据要设计一个32位单核RISC-V处理器这个需求,需要一步步分解、细化,得到一个能够满足需求的电路设计方案。通常verilog硬件描述需要将电路设计细化到寄存器传输级(Register Transfer Level,简称RTL级),不需要细分到更低层次的逻辑门电路、晶体管器件。

本设计基于E203内核进行处理器SoC拓展设计,E203内核了选择基于verilog语言编写。以文本形式来描述数字系统硬件的结构和行为的语言,verilog 可以表示逻辑电路图、逻辑表达式,以及数字逻辑系统所完成的逻辑功能。

E203内核是基于Verilog语言编写,采用了严谨的工业级开发标准,使用标准的DFF模块例化、生成寄存器,使用Verilog中的assign语法替代if-else和case语法[6]。3. 指令集功能仿真

指令集功能仿真,一般利用特定的软件环境对所设计的电路进行仿真,以一种模拟输入的方式测试所设计的电路的逻辑功能是否实现指令集的指令,及流水线信号变化行为是否符合预期,如果不正常则说明电路的设计有错误。本阶段的主要为了测试电路的具体功能是否正常、是否实现指令集的功能。本阶段中可以检查代码是否包含语法错误以及Verilog的硬件描述代码功能的正确性,忽略晶体管中的延迟。

本设计处理器的指令集功能仿真利用了RISC-V官方的riscv-tests,能够检测指令集中的指令在处理器中运行结果是否成功,判断处理器的设计是否可以通过指令集架构定义的测试程序。具体实现步骤是做一个整体的testcase(测试用例),然后将verilog所编写的处理器电路代码搭建到Iverilog的仿真环境中,在Iverilog的仿真环境中批量化运行所有准备好的测试用例都输入测试。而指令集功能仿真过程和测试结果,全部记录到日志文件(.log)中。

Iverilog是一个开源的、轻量的仿真测试环境,相较于Modelsim其使用也是较为方便的。同时Iverilog也可以通过指定一条指令(如add加法指令)来仿真流水线中的各个单元的仿真波形图。本阶段最终生成两个验证结果报告:指令测试文档和流水线仿真波形图。4. RTL级逻辑综合

综合是将Verilog编写的基本逻辑单元连接成逻辑连接网表,为了使其设计层次设计平面化需要优化其内部的逻辑连接,综合过程中需要确认FPGA的具体芯片资源,之后需要将最终优化后的逻辑网表配置到FPGA芯片上。综合就是把硬件描述语言转换为与其相对应的查找表和寄存器构成的功能电路。

本设计的的逻辑综合在Vivado工具中得到实现。Vivado是Xilinx FPGA的生产厂商赛灵思公司于2012年发布的针对FPGA开发的集成设计环境。Vivado可生产综合后的相关报告,提供有关设计中各部分资源的使用情况,并且可以通过Vivado的工具看到所设计处理器的流水线结构并生成相关报告,以便于检查综合结果。本阶段最终生成两个验证结果报告:流水线结构图、资源利用率报告。5. 引脚约束布局布线

布局布线将所综合出的逻辑网表文件分配到FPGA核心中的具体资源,需要根据开发板的原理图对FPGA核心上做指定的引脚约束。布局既将逻辑网表中的基本逻辑单元映射到FPGA芯片内部固有的硬件逻辑模块上;布线,将FPGA核心上布局好的硬件逻辑模块做连线连接,也会进一步优化硬件逻辑模块的布局。

利用Vivado对指定型号的FPGA核心进行布局布线是FPGA上板验证的基础。Vivado提供了较为简单的自动化布局布线操作,可以自动在速度最优和面积最优之间做出选择,使得FPGA核心内对硬件逻辑模块的连线合理、正确。因为FPGA进行手动布局布线比较复杂,当考虑所设计处理器的时序约束时,需要利用Vivado的时序驱动的引擎进行自动化布局布线。自动化布局布线后,Vivado会自动生成相关报告,提供有关设计中布局布线的结果和门级网表文件。利用赛灵思Vivado工具可以极大的简化布局布线的复杂度。本阶段最终生成两个验证结果报告:布局布线解析包、门级网表文件。6. 静态时序分析

静态时序分析(Static Timing Analysis, 简称STA),是利用从指定布线的路径上提取出相关时序设计的寄生参数后测试时序是否正常[18],STA主要关注一些电路设计内部的延时信息比较突出的信号节点流的关键路径,以分析是否存在时序冲突的路径。

本设计利用Vivado工具进行静态时序分析,Vivado不仅可以对处理器内部电路的设计进行全面的时序检查,而且还可以利用静态时序分析的结果来优化设计。本阶段最终生成两个验证结果报告:静态时序分析报表、功耗报告。7. FPGA上板测试

处理器验证的最后一步是FPGA上板测试,将比特流(Bitstream)文件下载到FPGA芯片的Flash中。使用 FPGA 来验证处理器的电路设计,可以提高验证的效率、缩短验证的时间。在tape-out(流片)之前,在FPGA上通过实际验证硬件模块,并对设计进行调试,以提高验证效率[15]。

经过综合和布局布线后,可利用Vivado生成一个比特流(Bitstream)文件,然后将其下载到FPGA芯片的Flash中,这样所设计的处理器就存在于FPGA核心上作为一个完整的SoC硬件存在了。在上板调试阶段,启动上电后运行观察其工作是否正常,如果发生问题就要进行更进一步的调试。FPGA上板测试可以通过设计SoC案例做案例测试,以及最终的性能分析。性能分析一般采用处理器的“跑分”程序,测试所设计处理器的得分如何。本阶段最终生成两个验证结果报告:SoC案例测试报告、处理器的“跑分”测试报告。 -

相关阅读:

Kotlin

QT网络编程http

【数据结构】树与二叉树(四):满二叉树、完全二叉树及其性质

G1D8-GNN@lab0&APT论文&美亚2021个人赛

JupyterNotebook的快捷键

Leetcode85. 最大矩形

VUE右键菜单 vue-contextmenujs的使用

面向对象开发方法

uniapp 小程序图片懒加载组件 ImageLazyLoad

CSS常用技巧

- 原文地址:https://blog.csdn.net/qq_43858116/article/details/125515211