-

FIR 中级应用 - AM 调幅波调制解调(FIR + FIFO)

本文链接:https://blog.csdn.net/qq_46621272/article/details/125384724

FIR 中级应用 - AM 调幅波调制解调(FIR + FIFO)

文章目录

- 前言

- 一、 调幅波调制

- 二、 调幅波解调

- 三、 am_fifo_fir_testbench.v verilog 代码

- 四、 FIR IP 设置

- 五、 FIFO IP 设置

- 六、 综合布线后 FPGA 资源使用报告

- 七、相关 vivado 工程、IP 设置等详细文档连接,采用 Xilinx vivado 2017.4 版本

- [XILINX FIR IP 详解、Verilog 源码、Vivado 工程](https://blog.csdn.net/qq_46621272/article/details/125292610)

- [FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波)详细介绍](https://blog.csdn.net/qq_46621272/article/details/125334644)

- [FIR 基础应用 - FM 调频波调制解调(FIR 低通滤波) 详细介绍](https://blog.csdn.net/qq_46621272/article/details/125337119)

- [FIR 中级应用 - AM 调幅波调制解调(FIR + FIFO)详细介绍](https://blog.csdn.net/qq_46621272/article/details/125384724)

- [FIR 高级应用 - AM 调幅波调制解调(FIR 低通滤波+重采样,FIR 高阶系数,FIR+FIFO ) 详细介绍](https://blog.csdn.net/qq_46621272/article/details/125385375)

- [FIR 高级应用 - 多通道实验 (四个通道用一个 FIR IP,每通道用不同的系数) 详细介绍](https://blog.csdn.net/qq_46621272/article/details/125346332)

- [FIR 高级应用 FIR Reload的使用) 详细介绍](https://blog.csdn.net/qq_46621272/article/details/125348908)

- [AM 调幅波调制解调(FIR 低通滤波) vivado 工程文件下载](https://download.csdn.net/download/qq_46621272/85674733)

- [FM 调频波调制解调(FIR 低通滤波) Vivado 工程文件下载](https://download.csdn.net/download/qq_46621272/85722410)

- [AM 调幅波调制解调(FIR + FIFO) Vivado 工程文件下载](https://download.csdn.net/download/qq_46621272/85722449)

- [AM 调幅波调制解调(FIR 低通滤波+重采样,FIR 高阶系数,FIR+FIFO ) Vivado 工程文件下载](https://download.csdn.net/download/qq_46621272/85722484)

- [FIR 高级应用 - 多通道实验 Vivado 工程文件下载](https://download.csdn.net/download/qq_46621272/85722518)

- [FIR 高级应用 FIR Reload 的使用 vivado 工程文件下载](https://download.csdn.net/download/qq_46621272/85722534)

前言

这是 XILINX FIR IP 详解、Verilog 源码、Vivado 工程 这篇文章的实验部分,这篇文章是介绍 FIR + FIFO 的使用方法。

一、 调幅波调制

1. 参考 FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波)

二、 调幅波解调

1. 参考 FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波)

2. am_fifo_demodulation_fir 模块逻辑框图

3. am_fifo_demodulation_fir.v verilog 代码

//am_fifo_demodulation_fir.v module am_fifo_demodulation_fir ( input rst_n, input clk, input clk_100mhz, input s_axis_data_tvalid, output s_axis_data_tready, input signed[15:0] s_axis_data_tdata, output m_axis_data_tvalid, input m_axis_data_tready, output signed[15:0] m_axis_data_tdata ); reg [15:0] abs_data_r = 0; reg abs_valid_r = 0; wire abs_tready_i; always @(posedge clk) begin if(rst_n == 0 ) abs_valid_r <= 0; else if(abs_tready_i == 1) abs_valid_r <= s_axis_data_tvalid; end always @(posedge clk) begin if(rst_n == 0 ) abs_data_r <= 0; else if(abs_tready_i == 1 && s_axis_data_tvalid == 1) begin if(s_axis_data_tdata >= 0) abs_data_r <= s_axis_data_tdata; else abs_data_r <= -s_axis_data_tdata; end end assign s_axis_data_tready = abs_tready_i; wire signed [15:0] fifo_as_tdata_i; wire fifo_as_tvalid_i; wire fifo_as_tready_i; wire fifo_as_clk_i; wire signed [15:0] fifo_am_tdata_i; wire fifo_am_tvalid_i; wire fifo_am_tready_i; wire fifo_am_clk_i; wire signed [15:0] fifo_bs_tdata_i; wire fifo_bs_tvalid_i; wire fifo_bs_tready_i; wire fifo_bs_clk_i; wire signed [15:0] fifo_bm_tdata_i; wire fifo_bm_tvalid_i; wire fifo_bm_tready_i; wire fifo_bm_clk_i; assign fifo_as_clk_i = clk; assign fifo_am_clk_i = clk_100mhz; assign fifo_bs_clk_i = clk_100mhz; assign fifo_bm_clk_i = clk; assign fifo_as_tdata_i = abs_data_r; assign fifo_as_tvalid_i = abs_valid_r; assign abs_tready_i = fifo_as_tready_i; axi_fifo_a16 fifo_ua ( .wr_rst_busy (), // output wire wr_rst_busy .rd_rst_busy (), // output wire rd_rst_busy .m_aclk (fifo_am_clk_i), // input wire m_aclk .s_aclk (fifo_as_clk_i), // input wire s_aclk .s_aresetn (rst_n), // input wire s_aresetn .s_axis_tvalid (fifo_as_tvalid_i), // input wire s_axis_tvalid .s_axis_tready (fifo_as_tready_i), // output wire s_axis_tready .s_axis_tdata (fifo_as_tdata_i), // input wire [15 : 0] s_axis_tdata .m_axis_tvalid (fifo_am_tvalid_i), // output wire m_axis_tvalid .m_axis_tready (fifo_am_tready_i), // input wire m_axis_tready .m_axis_tdata (fifo_am_tdata_i) // output wire [15 : 0] m_axis_tdata ); wire fir_a_clk_i; wire signed [15:0] fir_as_tdata_i; wire fir_as_tvalid_i; wire fir_as_tready_i; wire signed [39:0] fir_am_tdata_i; wire fir_am_tvalid_i; wire fir_am_tready_i; assign fir_a_clk_i = fifo_am_clk_i; assign fir_as_tvalid_i = fifo_am_tvalid_i; assign fir_as_tdata_i = fifo_am_tdata_i; assign fifo_am_tready_i = fir_as_tready_i; fir_compiler_lowpass_10k_30k_100m am_fir_u1 ( .aresetn (rst_n), // input wire aresetn .aclk (fir_a_clk_i), // input wire aclk .s_axis_data_tvalid (fir_as_tvalid_i), // input wire s_axis_data_tvalid .s_axis_data_tready (fir_as_tready_i), // output wire s_axis_data_tready .s_axis_data_tdata (fir_as_tdata_i), // input wire [15 : 0] s_axis_data_tdata .m_axis_data_tvalid (fir_am_tvalid_i), // output wire m_axis_data_tvalid .m_axis_data_tready (fir_am_tready_i), // input wire m_axis_data_tready .m_axis_data_tdata (fir_am_tdata_i) // output wire [39 : 0] m_axis_data_tdata ); assign fifo_bs_tvalid_i = fir_am_tvalid_i; assign fifo_bs_tdata_i = fir_am_tdata_i >>>19; assign fir_am_tready_i = fifo_bs_tready_i; axi_fifo_a16 fifo_ub ( .wr_rst_busy (), // output wire wr_rst_busy .rd_rst_busy (), // output wire rd_rst_busy .m_aclk (fifo_bm_clk_i), // input wire m_aclk .s_aclk (fifo_bs_clk_i), // input wire s_aclk .s_aresetn (rst_n), // input wire s_aresetn .s_axis_tvalid (fifo_bs_tvalid_i), // input wire s_axis_tvalid .s_axis_tready (fifo_bs_tready_i), // output wire s_axis_tready .s_axis_tdata (fifo_bs_tdata_i), // input wire [15 : 0] s_axis_tdata .m_axis_tvalid (fifo_bm_tvalid_i), // output wire m_axis_tvalid .m_axis_tready (fifo_bm_tready_i), // input wire m_axis_tready .m_axis_tdata (fifo_bm_tdata_i) // output wire [15 : 0] m_axis_tdata ); assign fifo_bm_tready_i = m_axis_data_tready; assign m_axis_data_tdata = fifo_bm_tdata_i; assign m_axis_data_tvalid = fifo_bm_tvalid_i; endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

三、 am_fifo_fir_testbench.v verilog 代码

/////////////////////////////////////////////////////////////////////// `timescale 1ns / 100ps //am_fifo_fir_testbench.v module am_fifo_fir_testbench; reg rst_n; reg clk; reg clk_100mhz; parameter CLK_PERIOD = 1000; //1MHz parameter CLK_PERIOD_100MHz = 10; //100MHz initial begin rst_n = 0; #(20 * CLK_PERIOD) rst_n = 1; #(1000 * CLK_PERIOD) $stop; end initial clk = 0; always begin clk = #(CLK_PERIOD/2.0) ~clk; end initial clk_100mhz = 0; always begin clk_100mhz = #(CLK_PERIOD_100MHz/2.0) ~clk_100mhz; end wire signed [15:0] am_mod_tdata; //调幅波数据,载波100KHz 正弦波,调制信号 4KHz 正弦波 wire am_mod_tvalid; wire am_mod_tready; wire signed [15:0] am_demod_tdata; //经过解调还原的 4KHz 正弦波 wire am_demod_tvalid; wire am_demod_tready=1; am_modulation_dds am_u1 //调幅波调制模块,生成 载波100KHz 正弦波,调制信号 4KHz 正弦波的调幅信号 ( .clk (clk), //1MHz .rst_n (rst_n), //复位 .m_axis_data_tdata (am_mod_tdata), //调幅波数据输出, output wire [16 : 0] .m_axis_data_tvalid (am_mod_tvalid), .m_axis_data_tready (am_mod_tready) ); am_fifo_demodulation_fir am_u2 //调幅波解调模块,将调幅波解调还原调制信号 ( .clk (clk), //1MHz .clk_100mhz (clk_100mhz), //100MHz .rst_n (rst_n), //复位 .s_axis_data_tdata (am_mod_tdata), //调幅信号输入 intput wire [16 : 0] .s_axis_data_tvalid (am_mod_tvalid), .s_axis_data_tready (am_mod_tready), .m_axis_data_tdata (am_demod_tdata), //调幅波解调数据输出, output wire [16 : 0] .m_axis_data_tvalid (am_demod_tvalid), .m_axis_data_tready (am_demod_tready) ); endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

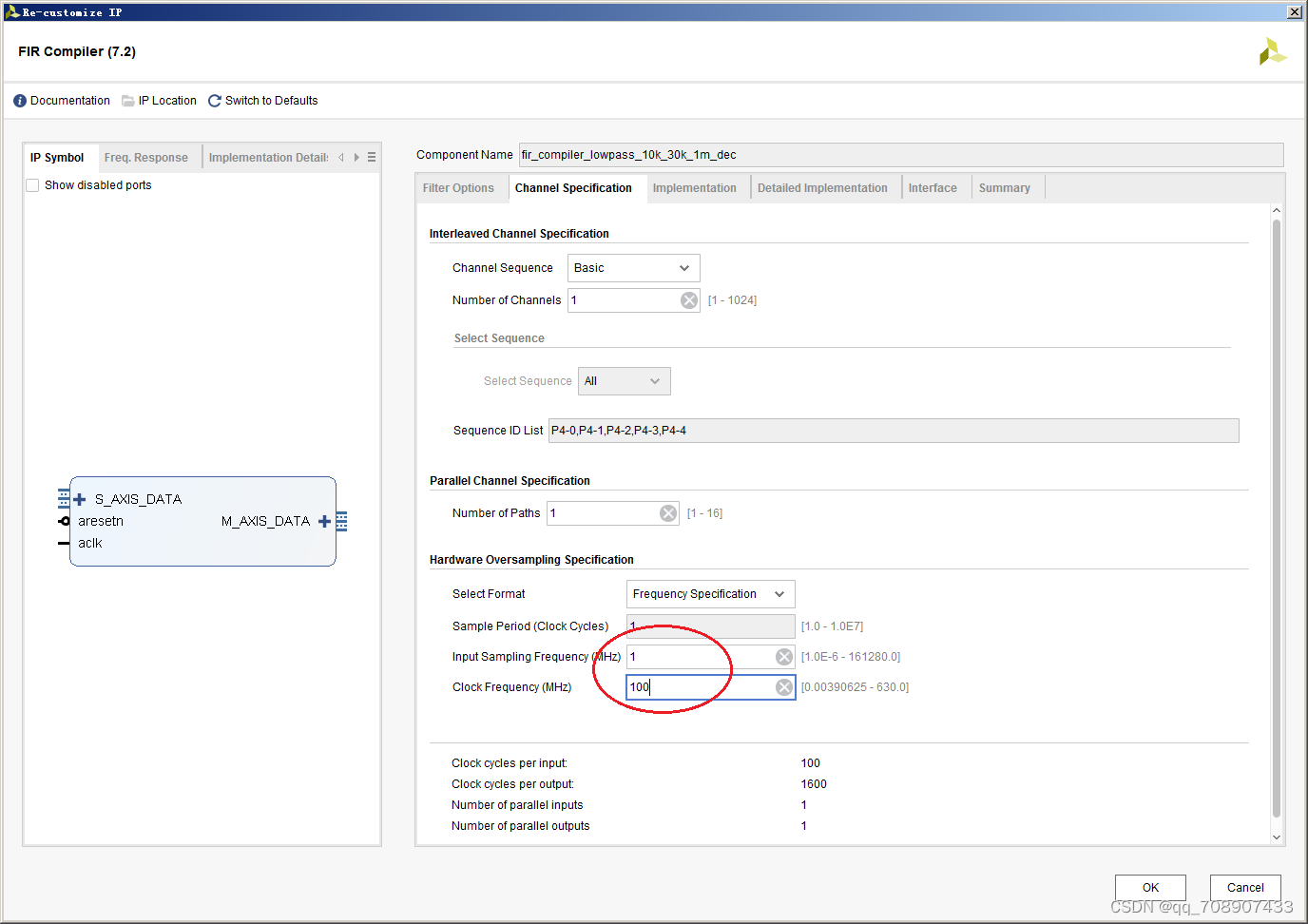

四、 FIR IP 设置

FIR IP 设置,COE 系数文件参考 FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波)

- FIR IP 不一样的地方贴图

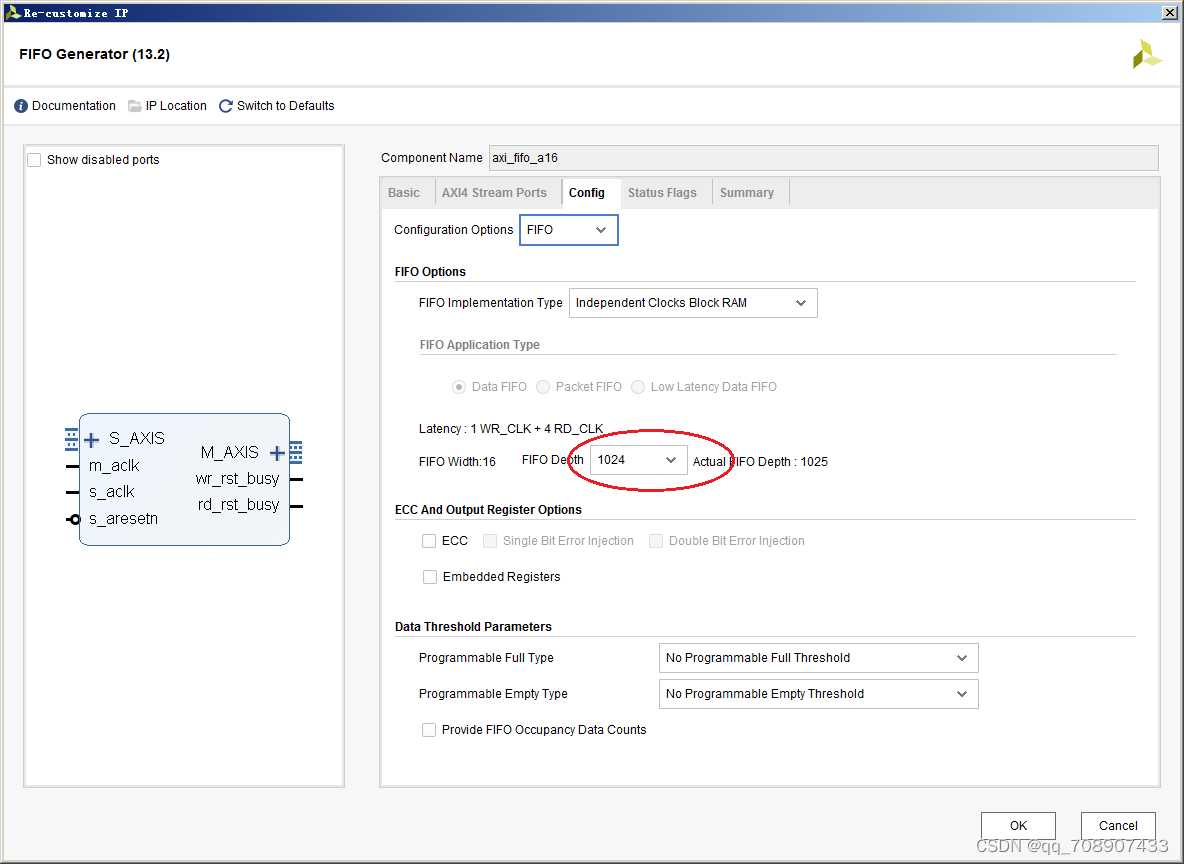

五、 FIFO IP 设置

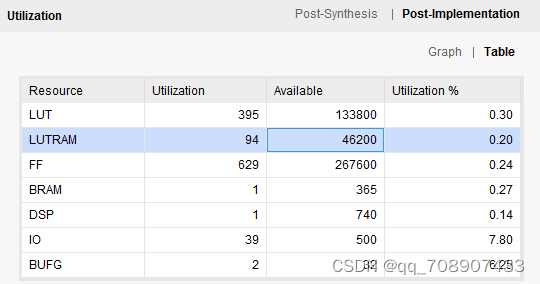

六、 综合布线后 FPGA 资源使用报告

七、相关 vivado 工程、IP 设置等详细文档连接,采用 Xilinx vivado 2017.4 版本

-

XILINX FIR IP 详解、Verilog 源码、Vivado 工程

-

FIR 基础应用 - AM 调幅波调制解调(FIR 低通滤波)详细介绍

-

FIR 基础应用 - FM 调频波调制解调(FIR 低通滤波) 详细介绍

-

FIR 中级应用 - AM 调幅波调制解调(FIR + FIFO)详细介绍

-

FIR 高级应用 - AM 调幅波调制解调(FIR 低通滤波+重采样,FIR 高阶系数,FIR+FIFO ) 详细介绍

-

FIR 高级应用 - 多通道实验 (四个通道用一个 FIR IP,每通道用不同的系数) 详细介绍

-

FIR 高级应用 FIR Reload的使用) 详细介绍

-

AM 调幅波调制解调(FIR 低通滤波) vivado 工程文件下载

-

FM 调频波调制解调(FIR 低通滤波) Vivado 工程文件下载

-

AM 调幅波调制解调(FIR + FIFO) Vivado 工程文件下载

-

AM 调幅波调制解调(FIR 低通滤波+重采样,FIR 高阶系数,FIR+FIFO ) Vivado 工程文件下载

-

FIR 高级应用 - 多通道实验 Vivado 工程文件下载

-

FIR 高级应用 FIR Reload 的使用 vivado 工程文件下载

-

相关阅读:

全国双非院校考研信息汇总整理 Part.8

someip 入门

最新网站证书提示风险的原因和几个解决方法

【 java 面向对象】多态性以及 instanceof 关键字的使用

跨桌面端Web容器演进

【Mybatis】浅谈延迟加载

使用两个不相关的模式模拟VCSEL光源

安装MYSQL遇到问题:write configuration file卡主

核心实验11合集_hybrid接口特殊用法_ENSP

二叉树的几个递归问题

- 原文地址:https://blog.csdn.net/qq_46621272/article/details/125384724