-

关于FPGA对 DDR4 (MT40A256M16)的读写控制 3

关于FPGA对 DDR4 (MT40A256M16)的读写控制 3

- 关键词: 调用,Verilog HDL,ifdef 和 endif ,generate语句

一、引言

博主将会写一个系列的文章 关于FPGA对DDR4(MT40A256M16)的有效读写控制,最大化FPGA对DDR4的读写控制。首先将对DDR4的技术文档进行研读,注重DDR4的读写操作、刷新时间等。

二、DDR的功能性描述

DDR4 SDRAM是一种高速动态随机存取存储器,其内部配置为16个存储体(对于x4/x8设备,是4个存储体组,每组4个存储体;对于x16设备,是2个存储体组,每组4个存储体)。该设备使用双数据速率(DDR)架构来实现高速操作。DDR4架构本质上是一种8n预取架构,其接口设计能够在I/O引脚上每个时钟周期传输两个数据字。

一个设备模块的单次读写访问实际上包括在内部DRAM核心的8n位宽、四个时钟周期的数据传输,以及在I/O引脚上的八个相应的n位宽、半个时钟周期的数据传输。

对设备的读写访问是突发导向的。访问从选定的位置开始,并以八个或四个的突发长度继续,按照程序序列进行。操作始于ACTIVE命令,然后是READ或WRITE命令。与ACTIVE命令同时发出的地址位用于选择要访问的存储体组和行(对于x4/x8,BG[1:0]选择存储体组,对于x16,BG0选择存储体组;BA[1:0]选择存储体,A[17:0]选择行);与READ或WRITE命令同时发送的地址位用于选择突发操作的起始列位置,确定是否发出自动PRECHARGE命令(通过A10),以及在模式寄存器中启用时,即时选择BC4或BL8模式(通过A12)。

在正常操作之前,设备必须以预定方式进行上电和初始化。三、SDRAM设备中模式寄存器的可编程性

模式寄存器需要用户通过特定的命令进行初始化和编程,以确保设备按照预期的方式运行

1、为了应用的灵活性,设备提供了七个模式寄存器(MRn),这些寄存器可以被编程为用户定义的变量,必须通过一个模式寄存器设置(MRS)命令来编程。

2、模式寄存器的默认值是未定义的,因此必须在上电和/或复位后完全初始化或重新初始化模式寄存器的内容,以确保设备正常工作

3、在正常操作期间,可以通过重新执行MRS命令来改变模式寄存器的内容。

4、编程模式寄存器时,即使用户选择只修改MRS字段的一个子集,当发出MRS命令时,也必须重新定义被访问的模式寄存器中的所有地址字段。

5、MRS命令和DLL重置命令不会影响存储阵列的内容,这意味着这些命令可以在上电后的任何时间执行,而不会影响存储阵列的内容MRS(Mode Register Set)的命令周期时间Tmrd, 是完成向模式寄存器写入操作所需的时间, 是两个MRS命令之间所需的最短时间,时间才能发送下一个MRS命令。这个时间间隔确保了第一个MRS命令能够完全执行,模式寄存器能够正确地接收并存储新的配置值。如果在这个时间间隔内发送了另一个MRS命令,可能会影响第一个命令的执行,导致设备配置不正确。

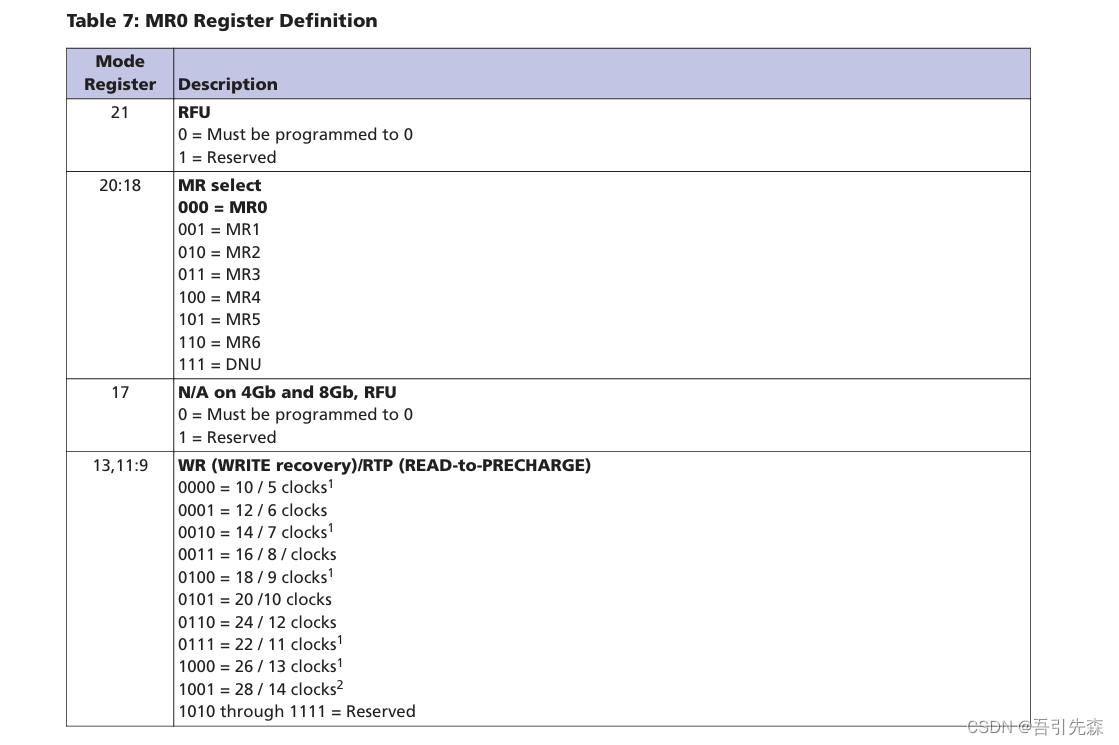

四、重要的模式寄存器之MR0

1、功能:MR0控制着设备的各种操作模式,具体的设置可以在随后提供的寄存器定义表中查看。并不是表中列出的所有设置在每个芯片上都可用;只有那些对于速度等级支持所必需的设置才是可用的。

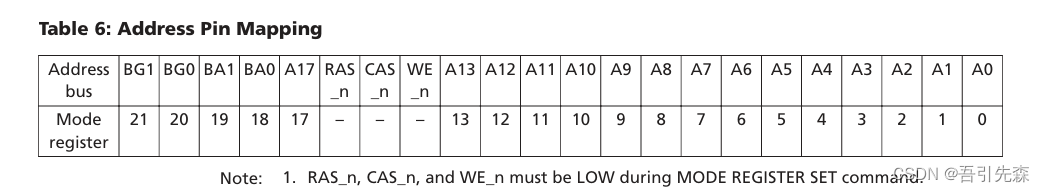

2、写入方法:MR0是通过发出模式寄存器设置(MRS)命令来写入的。在发出MRS命令的同时,需要控制BGx、BAx和Ax地址引脚的状态。

3、地址引脚映射:在MRS命令期间,地址引脚的映射关系会在随后的MR0寄存器定义表中展示

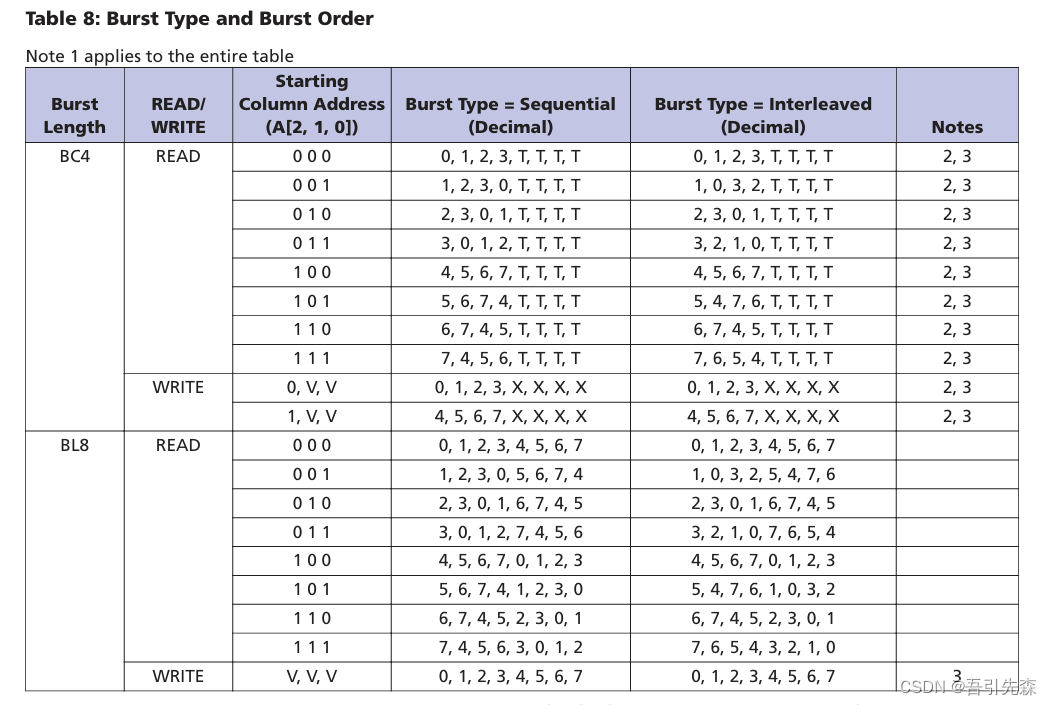

(1) Burst Length、Type、Order

这三个参数是控制内存访问行为的关键参数

1、Burst Length(突发长度)

这指的是在一次突发访问中连续读取或写入的数据块的大小。常见的突发长度有BC4:突发长度为4个字节

BL8:突发长度为8个字节2、Type(类型)

这通常指的是突发访问的模式,主要有两种类型Fixed:固定突发,意味着每次访问都使用相同的突发长度。 On-the-fly

(OTF):动态突发,允许在每次访问时根据需要选择BC4或BL83、Order(顺序)

这决定了在突发访问中数据是如何被读取或写入的。有两种主要的顺序:Sequential:顺序突发,数据按照内存中的物理顺序被访问。

Interleaved:交错突发,数据访问不是按照物理顺序,而是可能跳过某些存储体,按照特定的模式进行。突发访问的顺序可以被编程为顺序或交错顺序

顺序访问:在给定的突发中,访问可以按顺序进行,即按照存储体中数据的物理顺序。

交错访问:访问可以按交错顺序进行,这通常意味着数据访问不是按照物理顺序,而是按照特定的模式跳过某些存储体突发访问的顺序由以下因素决定:

1、突发长度:可以是固定的BC4(4个字节的突发)或BL8(8个字节的突发)。

2、突发类型:这可能指的是访问模式,比如正常突发或交错突发。

3、起始列地址:访问开始的列地址也会影响访问的顺序。

4、OTF选项:“On-the-fly”(OTF)选项允许在寄存器读或写命令的同时通过A12/BC_n选择BC4或BL8。这意味着突发长度可以在每次读写命令时动态选择,而不是固定在设备初始化时。

对上表作如下注释:

1、CA[2:0]的值:0到7的位数字表示在突发访问期间,该位将成为第一个被读取的位。CA[2:0]是一个3位地址字段,它决定了突发访问的起始列地址。

2、突发长度对写入操作的影响:

当在MR0(模式寄存器0)中将突发长度设置为BC4(固定)时,内部写入操作比BL8模式提前两个时钟周期开始。这意味着tWR(写入恢复时间)和tWTR(写入到读取时间)的起始点会提前两个时钟周期。当在MR0中将突发长度设置为OTF(即动态突发长度)时,即使在列地址时间使用A12/BC4_n选择了BC4,内部写入操作的开始时间也与BL8相同。这意味着如果使用OTF MR0设置,tWR和tWTR的起始点不会像BC4(固定)情况那样提前两个时钟周期。

3、输出驱动器状态

T:表示输出驱动器为数据和存取信号处于高阻抗状态(High-Z),即不驱动信号。

V:表示有效的逻辑电平(0或1),但相应的缓冲区输入在输入引脚上忽略电平。

X:表示“不关心”,即在该上下文中,该位的值不影响操作或结果。(2)CAS延迟

CAS延迟(CL)是DDR4 SDRAM内存性能的关键参数之一。

1、CAS延迟(CL)定义:CAS延迟在MR0寄存器定义表中给出,它指的是从内部读命令发出到第一个输出数据位可用之间的延迟,这个延迟以时钟周期来计量。

**2、不支持半时钟延迟:**设备不支持以半个时钟周期为单位的延迟设置,延迟必须以完整的时钟周期来定义。

3、整体读延迟(RL):整体读延迟是加法延迟(AL)与CAS延迟(CL)的总和,即: RL=AL+CLRL=AL+CL

**4、加法延迟(AL):**这是除了CAS延迟之外的其他延迟,可能包括命令发出到地址寄存器的延迟等。

**5、CAS延迟(CL):**如上所述,是读命令到数据可用的延迟。

这个公式说明了内存的读操作总延迟是如何由这两部分组成的。在系统设计中,了解和优化这些延迟对于确保内存性能满足应用需求至关重要。不同的应用可能对延迟有不同的容忍度,因此选择合适的CL和AL值对于实现最佳性能非常重要。(3)Test Mode

DDR4 SDRAM设备中模式寄存器0(MR0)的第7位(MR0[7])的作用以及正常操作模式的设置方法:

1、正常操作模式的选择:正常操作模式是通过设置MR0的第7位以及将其他位设置为MR0寄存器定义表中所显示的期望值来选择的。

2、MR0[7]的设置:当MR0[7]设置为0时,设备将进入正常操作模式。

当MR0[7]设置为1时,设备将进入由DRAM制造商定义的测试模式。这种模式仅供制造商使用,而不是最终用户。3、制造商测试模式: 如果MR0[7]设置为1,设备将处于制造商测试模式,这种模式下的操作或功能对最终用户来说是未指定的。这意味着在这种模式下,设备的行为可能与正常操作模式不同,并且可能包括用于诊断或测试的特定功能。

(4)Write Recovery (WR)/READ-to-PRECHARGE

1、tDAL的确定:tDAL(数据访问时间)可以通过tRP(行预充电时间)来确定

2、自动预充电的最小写入延迟(WR (MIN))

写入延迟(tWR)以纳秒为单位,时钟周期(tCK)也以纳秒为单位

动预充电的最小写入延迟(WR (MIN))通过将tWR除以tCK,并向上取整到下一个整数来计算

WR (MIN) cycles = roundup (tWR[ns]/tCK[ns])设备的写入延迟(WR)必须被编程为等于或大于最小写入延迟(WR (MIN))。

3、CRC对tWR的影响:

如果在模式寄存器中同时启用了DM(数据掩码)和写CRC(循环冗余校验),设备会在将写入数据发送到存储阵列之前计算CRC。

当启用CRC时,tWR值会改变。如果出现CRC错误,设备将阻止写入操作并丢弃数据4、RTP值的用途: 编程后的RTP值与tRP一起用于确定对同一存储体的激活(ACT)时序

这些时序参数对于确保DDR4 SDRAM设备正确地执行读写操作至关重要。它们需要根据具体的时钟频率和设备要求进行精确计算,并在模式寄存器中进行适当编程。如果启用了额外的错误检测或校验功能,如CRC,还需要考虑它们对时序参数的影响。

-

相关阅读:

Electron笔记

17-VMware Horizon 2203 虚拟桌面-Win10 手动桌面池浮动(十七)

经典OJ题:链表中的倒数第K个节点

JAVA 基础网络编程(后一部分)

数据结构 ----- 折半插入排序

删除 PostgresSql 数据库 报错:有 N 个其它会话正在使用数据库 的解决方案

年薪高达115万元,Rust成2021年最赚钱的编程语言

计算机中整数的表示和整数运算

【Web安全】HTML5安全

Spring SSM整合步骤

- 原文地址:https://blog.csdn.net/qq_34895681/article/details/139772669