-

MEMS:Lecture 19 Wafer bonding & package

讲义

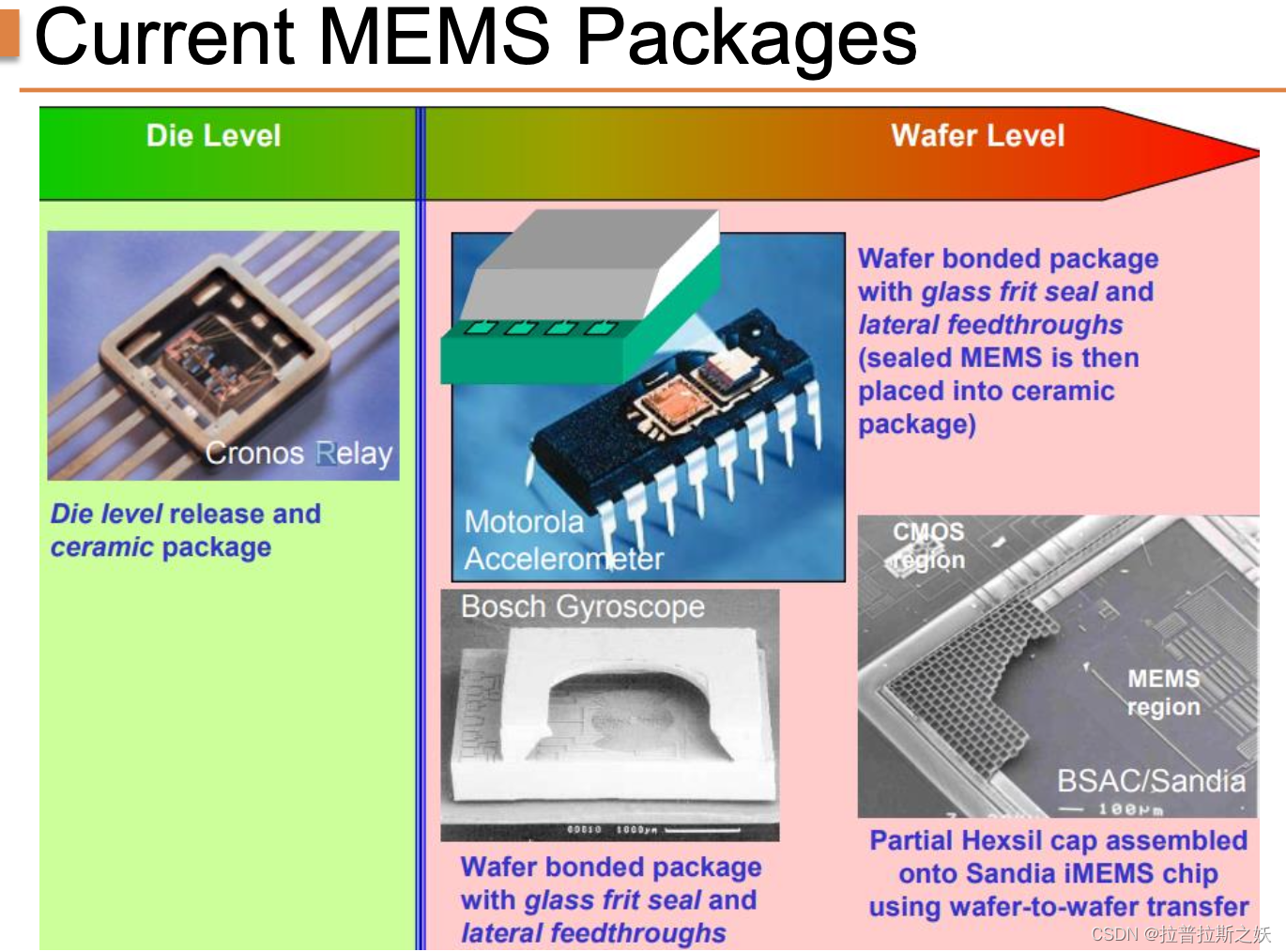

Current MEMS Packages

Die Level (芯片级) 封装

- 图片描述:左侧的图显示了Cronos继电器的芯片级封装。这种封装方式是在晶圆切割后,将独立的MEMS芯片组装到单独的陶瓷封装中。

- 特点:

- Die level release and ceramic package:MEMS器件在切割后释放,然后装入陶瓷封装。此方法适用于单个芯片,需要较大的封装空间。

Wafer Level (晶圆级) 封装

- 图片描述:右侧的图包括摩托罗拉加速度计、博世陀螺仪等示例,显示了晶圆级封装方法。这些MEMS器件使用了玻璃熔融密封和横向通孔,随后将封装好的MEMS放入陶瓷封装中。

- 特点:

- Wafer bonded package with glass frit seal and lateral feedthroughs:采用晶圆键合技术进行玻璃熔融密封和横向通孔。这种方法可以实现更小的封装尺寸和更高的集成度。

- Examples:包括摩托罗拉加速度计、博世陀螺仪,这些器件利用晶圆级封装来简化生产和提高器件性能。

Wafer Bonding in MEMS

概述

- 晶圆级封装:强调MEMS器件的构建过程中晶圆级封装的重要性。

- MEMS器件构建:

- Sealed structures:封装结构,如压力传感器和流体通道。

- Multiwafer structures:多晶圆结构,如微型全分析系统(μTAS)、微型涡轮机、光学设备、喷墨打印头。

图示

- Motorola pressure sensor(摩托罗拉压力传感器):展示了使用玻璃熔融密封的截面图,该密封方法用于高精度的压力传感器。

- Jensen group, MIT:展示了微型流体通道的高分辨率结构,这些通道用于精密流体控制。

- MIT microturbine(MIT微型涡轮机):展示了复杂的微型涡轮结构,代表了多晶圆结构在微机械应用中的复杂性和精度。

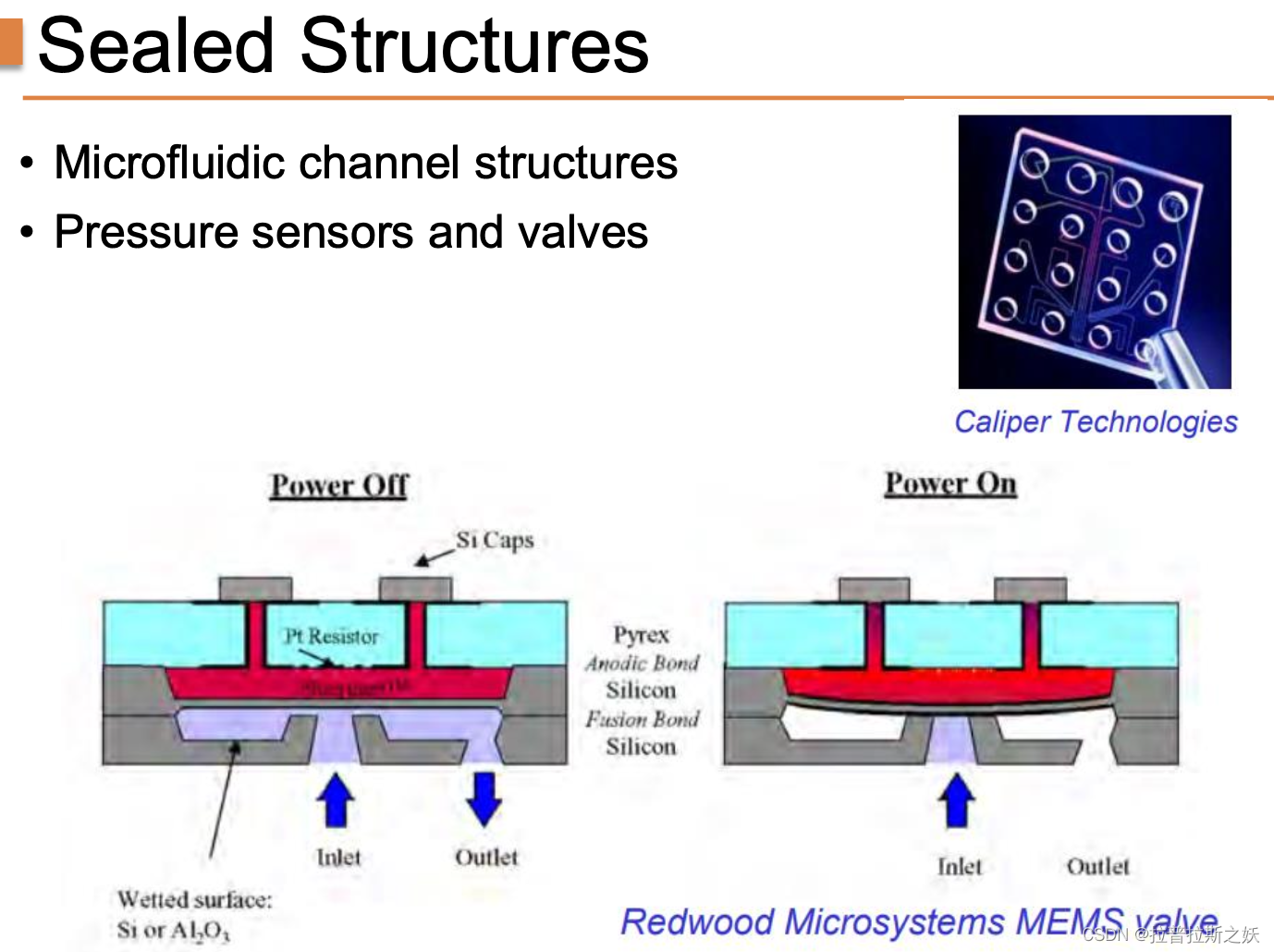

Sealed Structures

微流体通道结构

- 图示:展示了使用微流体通道结构的典型示例,这些结构用于压力传感器和阀门。

- 细节:

- Microfluidic channel structures:显示了微流体通道结构的横截面图,这些结构用于流体控制和精确测量。

- Pressure sensors and valves:展示了压力传感器和阀门的设计细节,强调了在无电源和有电源情况下的结构变化。

技术细节

- Caliper Technologies:提供了一个微流体通道的实际应用示例,说明了如何在微流体系统中使用这些通道进行精确控制。

- Redwood Microsystems MEMS valve:展示了MEMS阀门的结构设计,在电源开/关状态下的工作原理,使用了阳极键合和融合键合方法进行密封。

Wafer Bonding Methods 晶圆键合方法

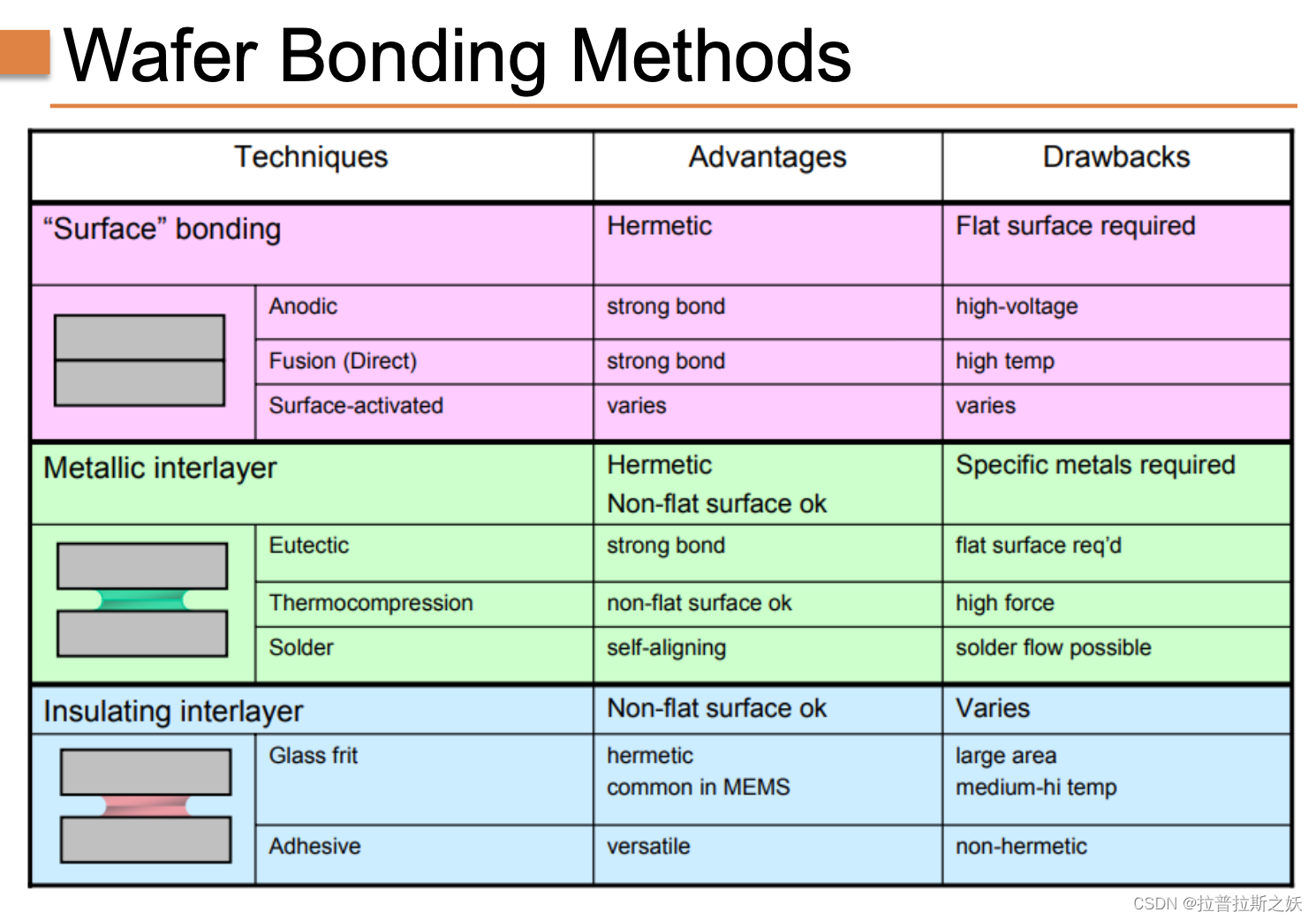

晶圆键合是将两个或多个晶圆结合在一起的过程,用于制造MEMS和其他微型器件。这一页展示了三种主要的晶圆键合方法:

-

表面键合 (Surface Bonding)

- 描述:简单的表面接触方式。两个超平滑的表面通过范德华力、氢键等弱力结合。

- 图示:顶部示意图表示两个无中间层的晶圆直接接触键合。

-

金属层键合 (Metallic Layer Bonding)

- 描述:在两个晶圆之间加入一层金属,用于提高导电性或增强机械强度。

- 图示:中间示意图显示了在两个晶圆之间添加了一层绿色的金属层。

-

绝缘层键合 (Insulating Layer Bonding)

- 描述:在两个晶圆之间加入一层绝缘材料,如玻璃或聚合物,用于电气隔离或特定应用场景。

- 图示:底部示意图显示了在两个晶圆之间添加了一层红色的绝缘层。

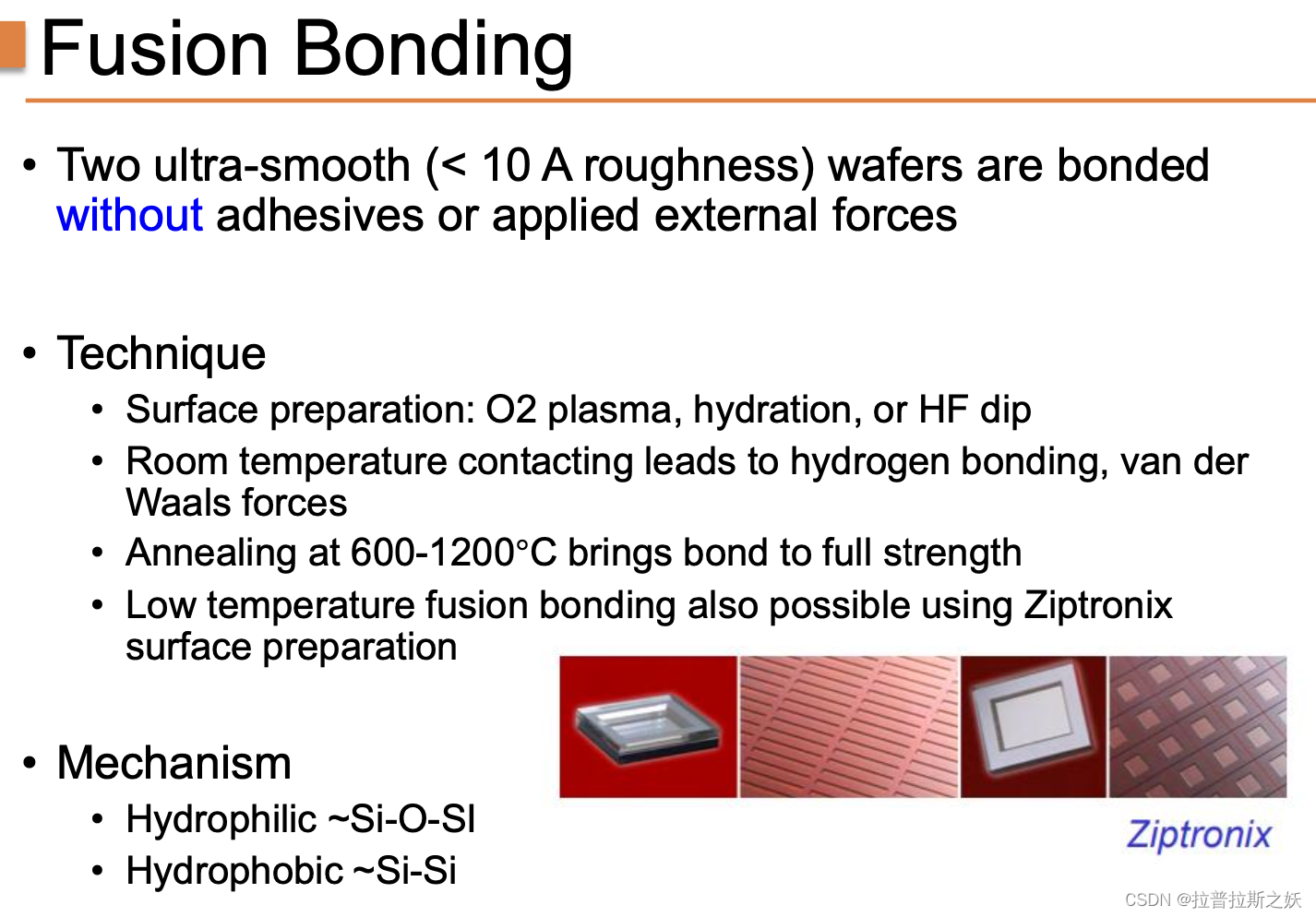

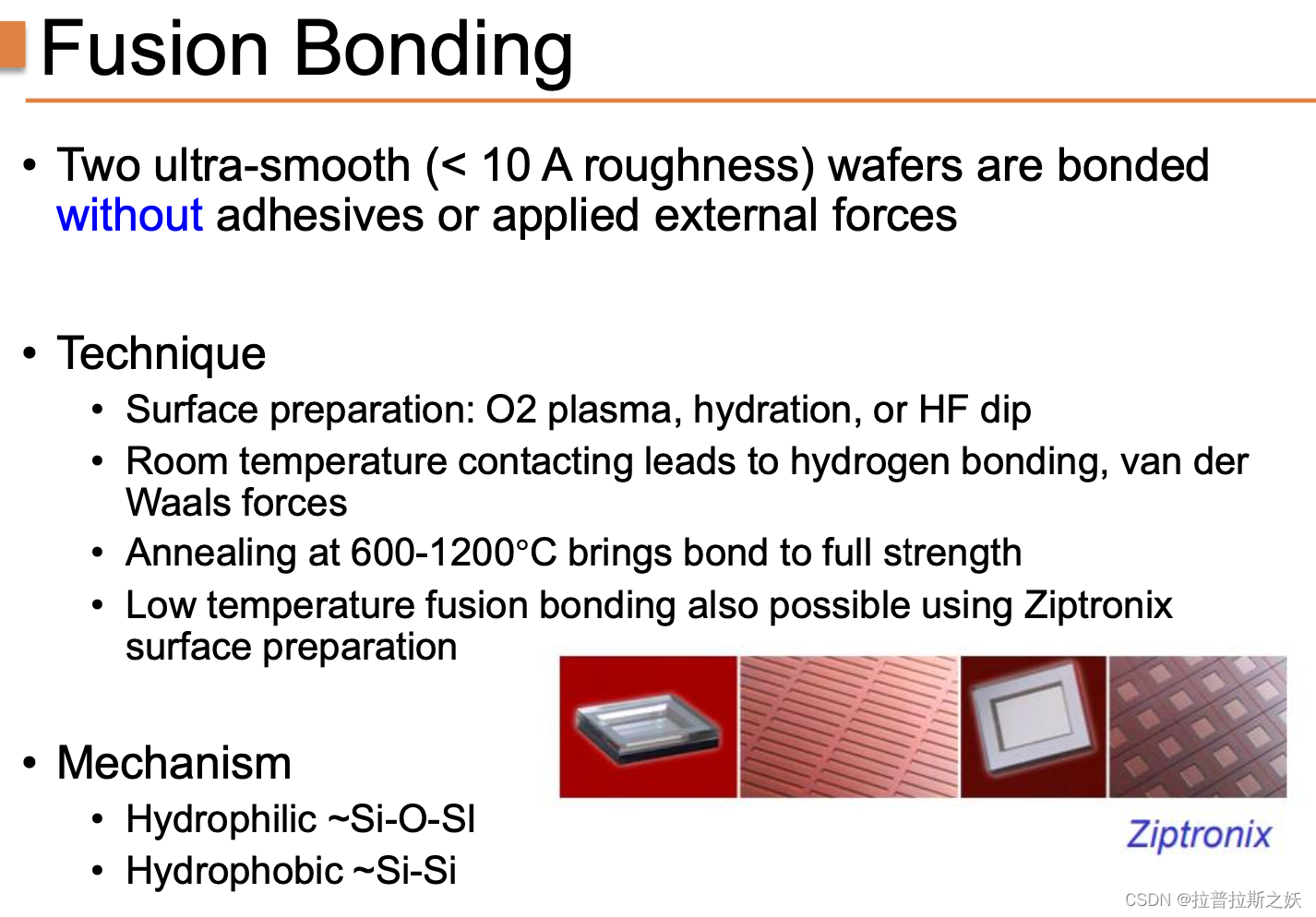

Fusion Bonding

融合键合是一种不使用粘合剂或外部施加的力,仅通过清洁和光滑表面的直接接触实现晶圆结合的方法。

技术细节

- 表面准备 (Surface preparation):包括O2等离子体处理、水合处理或氢氟酸(HF)浸泡,使表面活化以增加结合力。

- 室温接触 (Room temperature contacting):通过氢键和范德华力在室温下使两个表面初步结合。

- 退火 (Annealing):在600-1200°C下退火,使键合达到完全强度。

- 低温融合键合 (Low temperature fusion bonding):使用Ziptronix表面处理技术,可以在较低温度下实现融合键合。

机制

- 亲水性键合 (Hydrophilic Bonding):通过Si-O-Si键合。

- 疏水性键合 (Hydrophobic Bonding):通过Si-Si键合。

图示

- 右侧展示了典型的融合键合设备和样品图。最左侧的图片展示了带有键合特征的MEMS芯片。

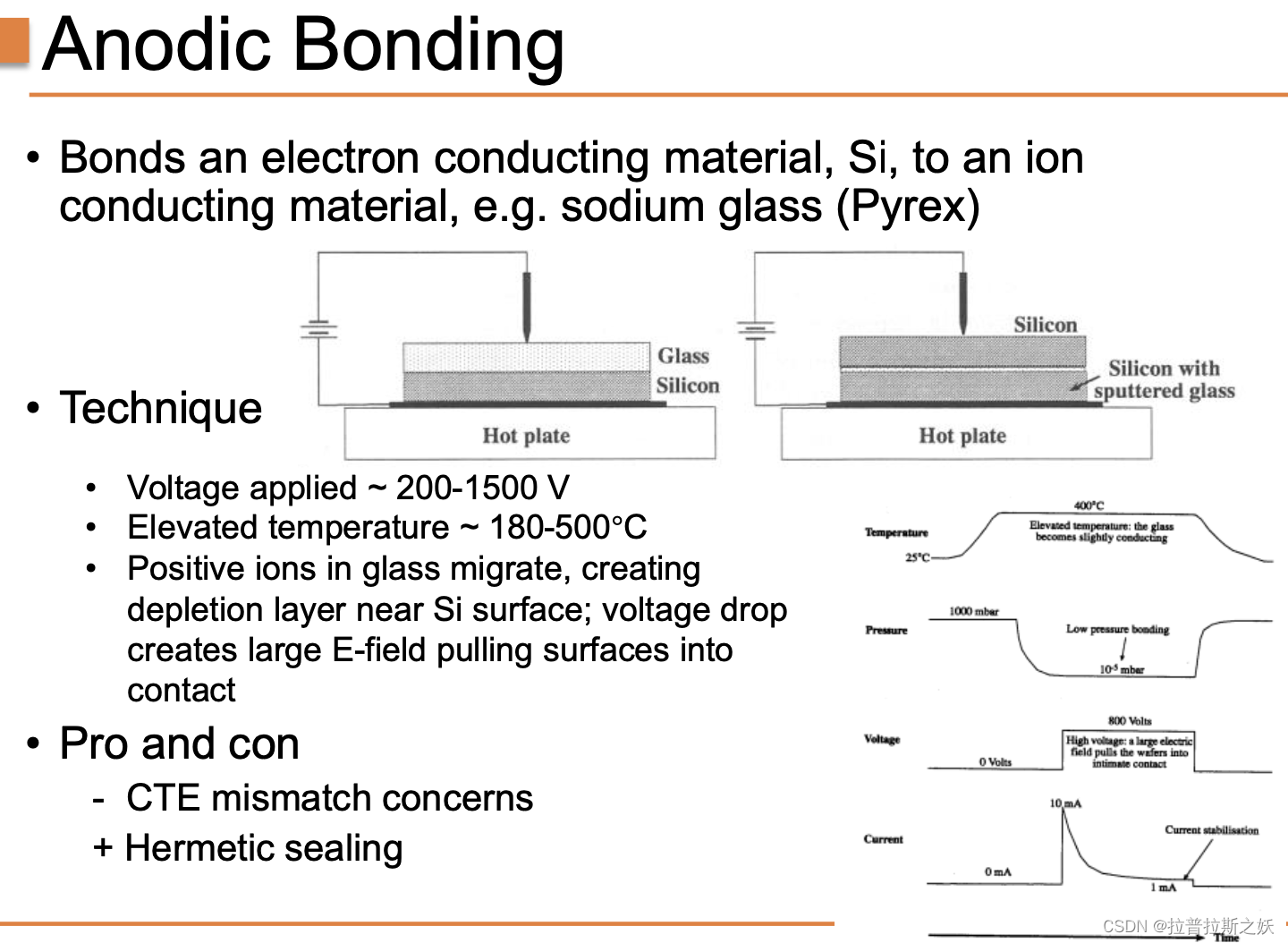

Anodic Bonding 阳极键合

阳极键合是一种将电子导电材料(如硅)与离子导电材料(如含钠玻璃)结合的方法,通常用于制造气密封装的MEMS器件。

技术细节

- 电压 (Voltage applied):通常在200-1500V之间。

- 温度 (Elevated temperature):工作温度在180-500°C之间。

- 离子迁移 (Ion migration):玻璃中的正离子在电场下迁移,形成耗尽层,使表面在电场作用下紧密接触。

优缺点

- 缺点 (Cons):热膨胀系数不匹配(CTE mismatch)可能导致应力和失效。

- 优点 (Pros):能实现高气密性的封装。

图示

- 右侧上部展示了阳极键合的典型装置结构图,其中包括了玻璃和硅在热板上的排列,以及在不同电压和温度条件下的键合过程。

- 下部的流程图展示了阳极键合的典型过程,包括温度和电流的变化。

阳极键合过程

图示解释

- 步骤 1:在中心键合销激活后5秒,显示出玻璃和硅之间形成的初步键合区域。

- 步骤 2:20秒后,所有键合销都激活,形成了更大的键合区域。

- 步骤 3:2.5分钟后,键合前缘进一步扩展,显示出键合过程的逐步进行。

- 步骤 4:8分钟后,键合完成98%,几乎整个晶圆都被均匀地键合。

- 参数设置:

- 晶圆直径:100 mm

- 玻璃厚度:500 µm

- 温度:430°C

- 电压:800 V

- 氮气压力:1000 mbar

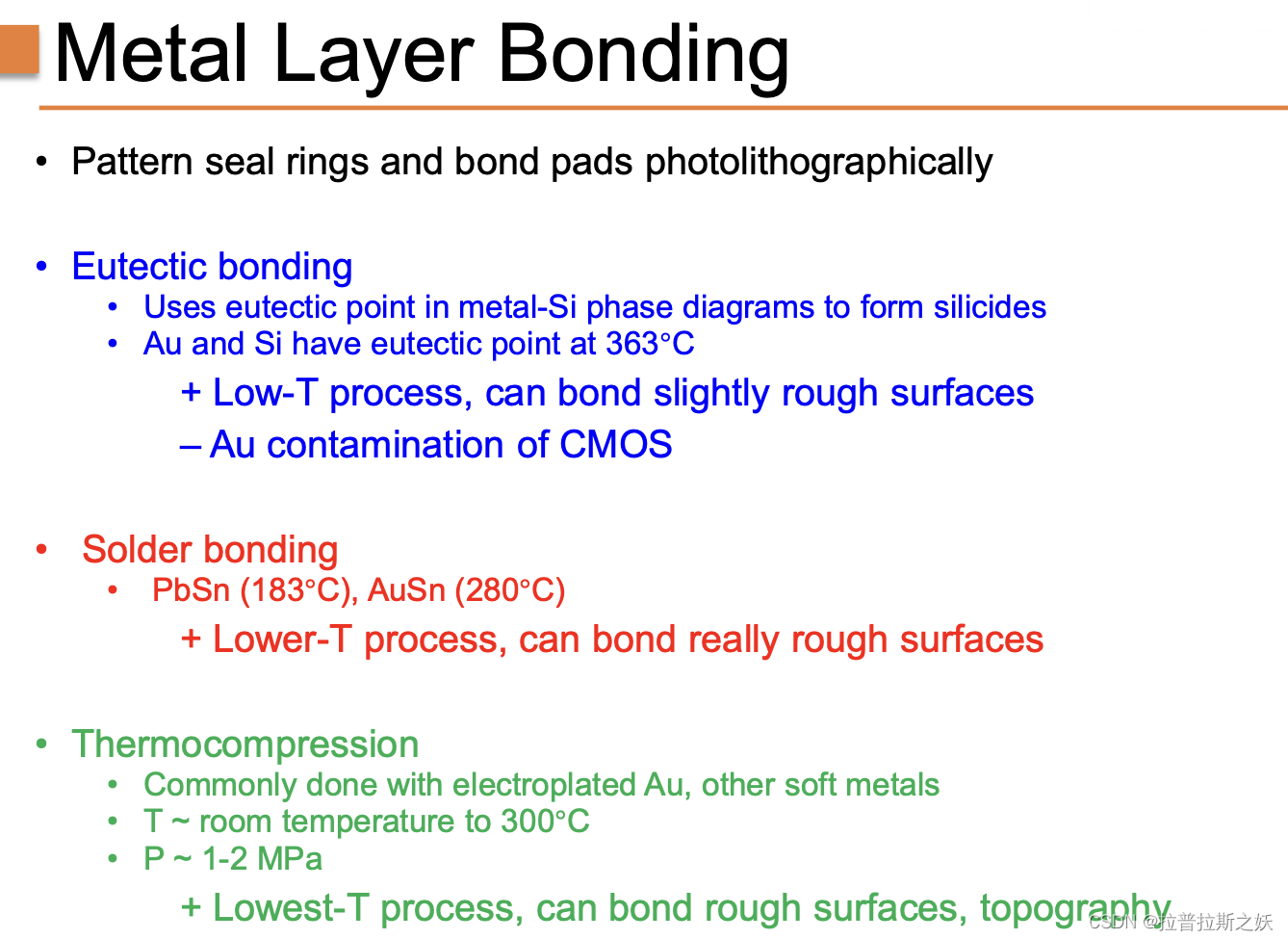

Metal Layer Bonding、

金属层键合是通过在晶圆之间插入金属层来实现的,主要用于增强机械强度、导电性和形成密封环。这一页介绍了三种主要的金属层键合方法:

-

共晶键合 (Eutectic Bonding)

- 描述:利用金属-硅相图中的共晶点形成硅化物。例如,金和硅在363°C下具有共晶点。

- 优点 (Pros):

- 低温工艺,适用于稍微粗糙的表面。

- 缺点 (Cons):

- 可能导致CMOS器件的金污染。

- 图示:图中的蓝色文本部分描述了共晶键合的温度和效果。

-

焊料键合 (Solder Bonding)

- 描述:使用铅锡(PbSn,183°C)或金锡(AuSn,280°C)等焊料进行键合。

- 优点 (Pros):

- 更低温的工艺,适用于非常粗糙的表面。

- 图示:图中的红色文本部分描述了焊料键合的温度和效果。

-

热压键合 (Thermocompression Bonding)

- 描述:通常使用电镀金或其他软金属进行键合,操作温度为室温至300°C,压力为1-2 MPa。

- 优点 (Pros):

- 最低温度工艺,可键合粗糙表面和复杂地形。

- 图示:图中的绿色文本部分描述了热压键合的工艺参数和优点。

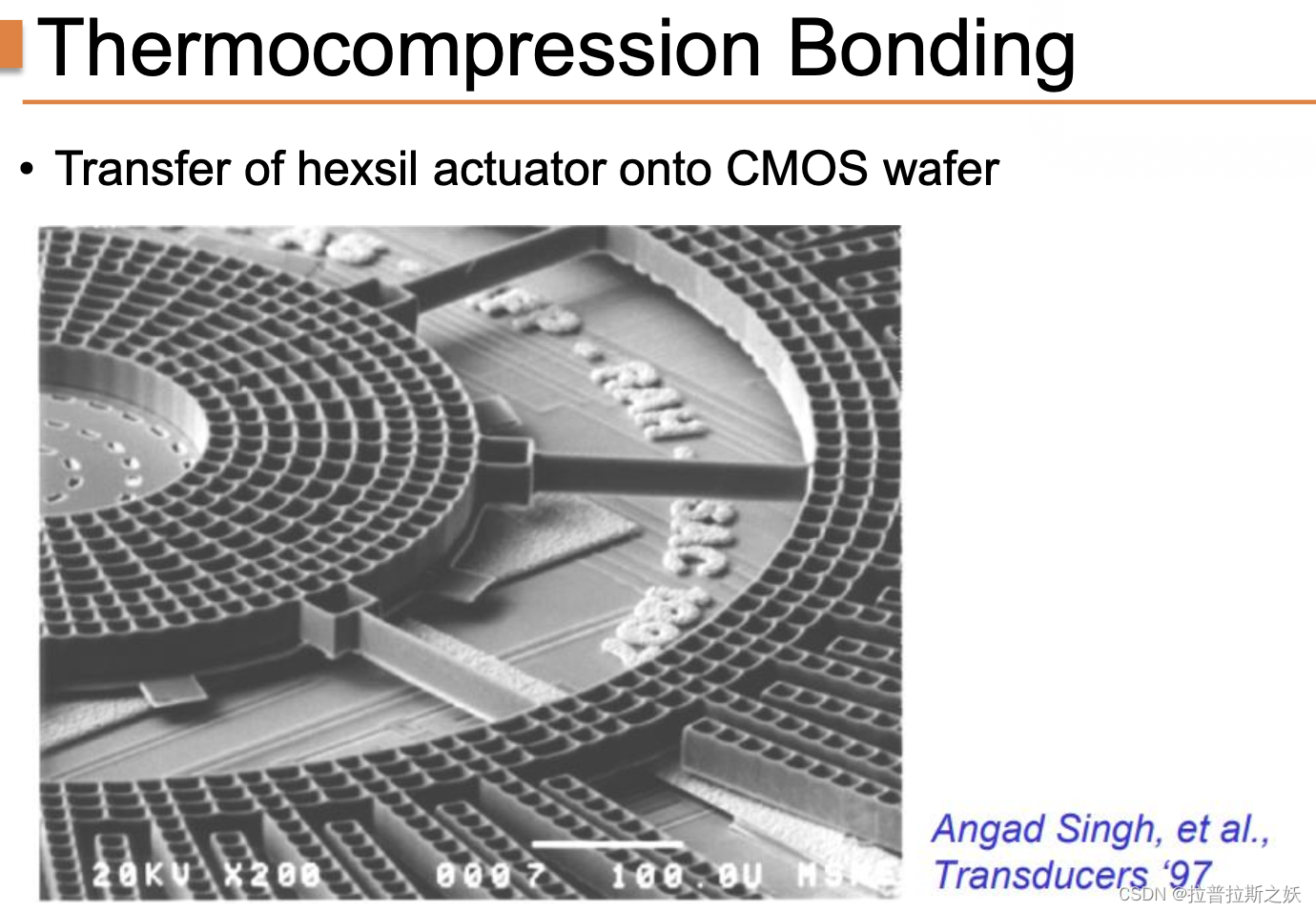

Thermocompression Bonding 热压键合

热压键合是一种通过在相对较低的温度和压力下结合两个表面的方法,特别适用于需要高精度对准的应用。

技术细节

- 工艺参数:通常在室温至300°C范围内进行,压力约为1-2 MPa。

- 应用示例:

- Hexsil执行器传输 (Transfer of hexsil actuator):显示了将Hexsil微型执行器传输到CMOS晶圆上的图像,展示了热压键合的应用。

图示

- 图像描述:右侧图像是扫描电子显微镜(SEM)下的Hexsil结构示例,展示了该结构在CMOS晶圆上的集成。这些结构通常用于精密机械应用。

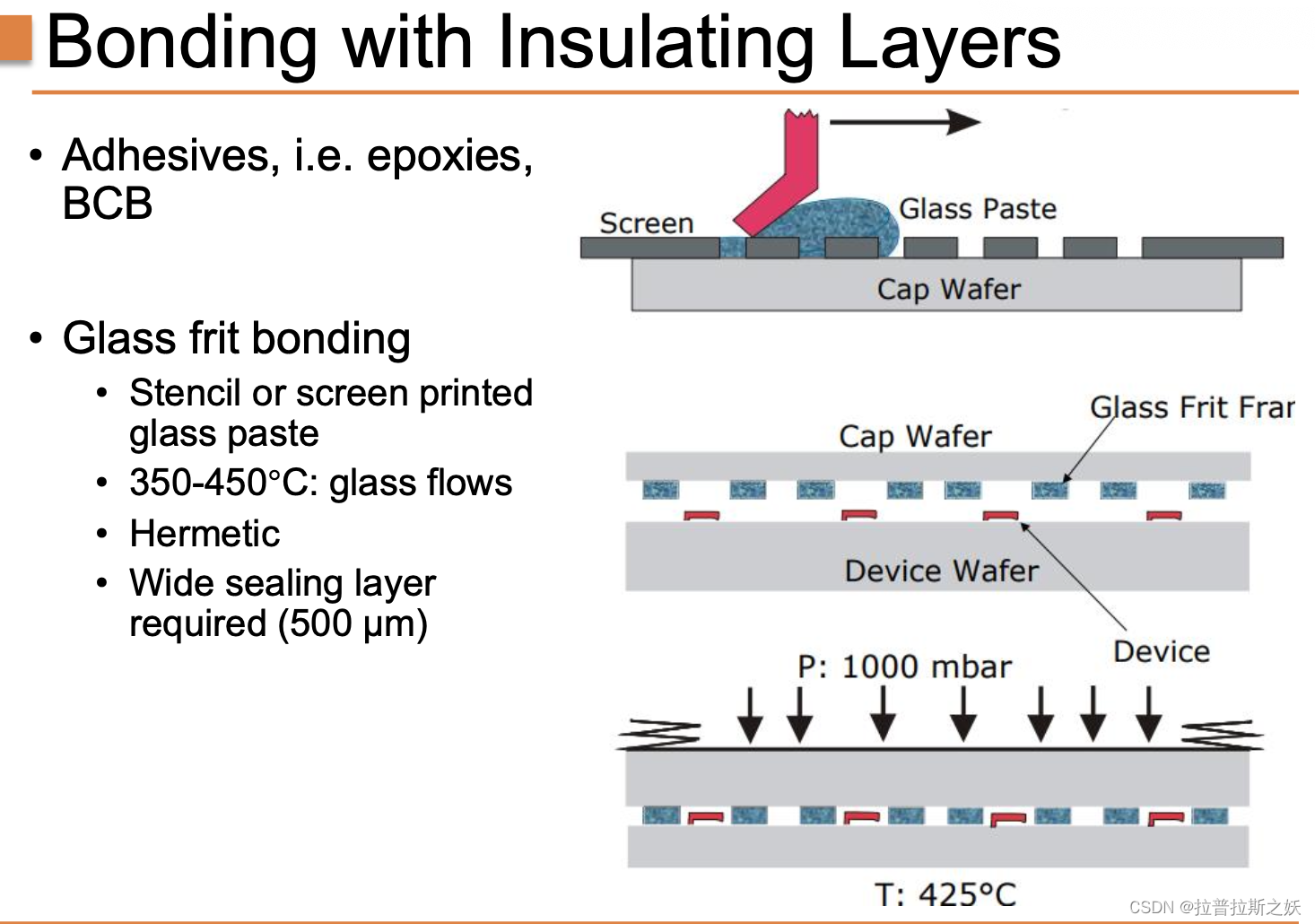

使Bonding with Insulating Layers 用绝缘层的键合

标题: Bonding with Insulating Layers

概述

绝缘层键合通过在晶圆之间插入绝缘材料来实现,这种方法通常用于电气隔离或特定应用场景。-

粘合剂 (Adhesives)

- 描述:使用环氧树脂(epoxies)或BCB(苯并环丁烯)等粘合剂进行键合。

- 应用:适用于需要电气隔离的应用。

-

玻璃熔融键合 (Glass Frit Bonding)

- 描述:通过模板或丝网印刷玻璃浆,在350-450°C下玻璃流动形成键合层。

- 优点:能够实现气密封装。

- 缺点:需要宽的密封层(500 µm)。

- 图示:显示了玻璃浆料的印刷和流动,以及典型的键合过程和参数(如压力1000 mbar,温度425°C)。

图示

- 图像描述:

- 上方图示:展示了玻璃浆料的印刷过程,将浆料印刷到封帽晶圆上,然后与器件晶圆键合。

- 下方图示:展示了玻璃熔融键合过程中的典型步骤,包括压力和温度条件。

Glass Frit Bonding玻璃熔融键合

标题: Glass Frit Bonding

概述

玻璃熔融键合是通过将玻璃浆料在高温下熔融,形成密封的键合层,用于制造气密封装的MEMS器件。技术细节

- 工艺参数:玻璃浆料在350-450°C下熔融,形成坚固的键合层。

- 应用:用于需要高气密性的应用,如开关和微机械结构。

图示

- 左上角图示:显示了玻璃熔融键合的截面图,展示了玻璃层在高温下的结构变化。

- 右上角图示:展示了一个键合完成的晶圆图,显示了整体键合的均匀性。

- 左下角图示:展示了由Radant MEMS封装的开关,这些开关利用了玻璃熔融键合技术。

- 右下角图示:展示了Suss MicroTEC的一个典型器件,说明了玻璃熔融键合在微型开关和其他器件中的应用。

技术分类:

-

表面键合 (Surface Bonding)

- 优点 (Advantages):

- 气密性 (Hermetic):能够形成高质量的气密封装。

- 强键合 (Strong Bond):不同的表面键合方法提供不同程度的强键合。

- 缺点 (Drawbacks):

- 需要平整表面 (Flat Surface Required):大多数表面键合技术要求晶圆表面非常平整,以确保有效的接触和键合。

- 具体方法 (Specific Techniques):

- 阳极键合 (Anodic Bonding):

- 优点:提供强键合和气密性。

- 缺点:需要高电压。

- 融合键合 (Fusion Bonding):

- 优点:提供强键合和气密性。

- 缺点:需要高温。

- 表面活化键合 (Surface-Activated Bonding):

- 优点:键合强度可变,视具体表面处理技术而定。

- 缺点:缺点因表面活化技术的不同而异。

- 阳极键合 (Anodic Bonding):

- 优点 (Advantages):

-

金属中间层键合 (Metallic Interlayer Bonding)

- 优点 (Advantages):

- 气密性 (Hermetic):同样能够提供高质量的气密封装。

- 适用于非平整表面 (Non-Flat Surface OK):一些金属键合方法对表面平整度要求较低。

- 缺点 (Drawbacks):

- 需要特定金属 (Specific Metals Required):某些方法要求使用特定的金属中间层。

- 具体方法 (Specific Techniques):

- 共晶键合 (Eutectic Bonding):

- 优点:提供强键合。

- 缺点:要求平整表面。

- 热压键合 (Thermocompression Bonding):

- 优点:适用于非平整表面。

- 缺点:需要高压力。

- 焊料键合 (Solder Bonding):

- 优点:自对准,焊料流动可以补偿表面缺陷。

- 缺点:焊料流动可能影响精度。

- 共晶键合 (Eutectic Bonding):

- 优点 (Advantages):

-

绝缘中间层键合 (Insulating Interlayer Bonding)

- 优点 (Advantages):

- 适用于非平整表面 (Non-Flat Surface OK):这些方法对表面平整度要求较低。

- 缺点 (Drawbacks):

- 差异化较大 (Varies):根据具体绝缘材料和工艺的不同,性能会有较大差异。

- 具体方法 (Specific Techniques):

- 玻璃熔融键合 (Glass Frit Bonding):

- 优点:提供气密封装,常用于MEMS器件。

- 缺点:需要大面积封装层和中高温处理。

- 粘合剂键合 (Adhesive Bonding):

- 优点:多功能性强,可适用于各种材料和结构。

- 缺点:非气密封装。

- 玻璃熔融键合 (Glass Frit Bonding):

- 优点 (Advantages):

各方法对比

表面键合

表面键合技术通常需要非常平整的表面,以确保两个晶圆在接触时能有效结合。阳极键合通过高电压结合硅和含钠玻璃,适用于需要高气密性的封装。融合键合利用高温使两个超光滑表面结合,适合高温环境。表面活化键合通过表面活化处理增强结合力,应用较为广泛,但需要具体选择适合的活化方法。

金属中间层键合

金属中间层键合利用金属层的物理和化学性质实现键合。共晶键合利用金属-硅相图中的共晶点,适合高温工艺。热压键合在相对较低的温度和高压力下进行,适合复杂表面结构。焊料键合使用低熔点金属进行自对准,适合需要补偿表面缺陷的应用。

绝缘中间层键合

绝缘中间层键合通过插入绝缘材料实现,适合需要电气隔离或特定应用。玻璃熔融键合使用玻璃浆料形成气密封装,常用于MEMS器件。粘合剂键合则具有广泛的适用性,但通常不能提供气密封装。

Wafer Bonding Considerations

关键考虑因素

-

地形:平面或纹理?(Topography: planar or textured?)

- 解释:晶圆的表面形貌对键合方法的选择至关重要。平面表面通常适用于各种键合方法,而带有纹理或复杂结构的表面可能需要特定的键合技术,如热压键合或使用金属层的键合,以补偿表面不平整带来的影响。

-

材料:绝缘或导电?(Material: insulating or conducting?)

- 解释:材料的电气特性(绝缘或导电)决定了适用的键合方法。例如,阳极键合需要一种材料能够导电,而另一种材料是离子导电的(如含钠玻璃),而金属层键合则需要特定的金属材料。

-

需要气密性吗?(Hermeticity required?)

- 解释:气密性需求决定了选择何种键合方法。气密封装对于MEMS器件的环境控制和可靠性至关重要。阳极键合、融合键合和玻璃熔融键合等方法通常可以提供优异的气密性。

-

允许的最高温度或力?(Maximum temperature or force allowed?)

- 解释:键合过程中所能承受的最高温度和力的限制会影响选择的键合方法。例如,低温工艺(如热压键合)适合对温度敏感的材料,而高温工艺(如融合键合)可能需要对材料的热稳定性有较高要求。

-

生物相容性?(Biocompatibility?)

- 解释:对于植入式MEMS或与生物系统直接接触的器件,材料和键合方法的生物相容性至关重要。必须选择不会引起生物反应或毒性的材料和工艺。

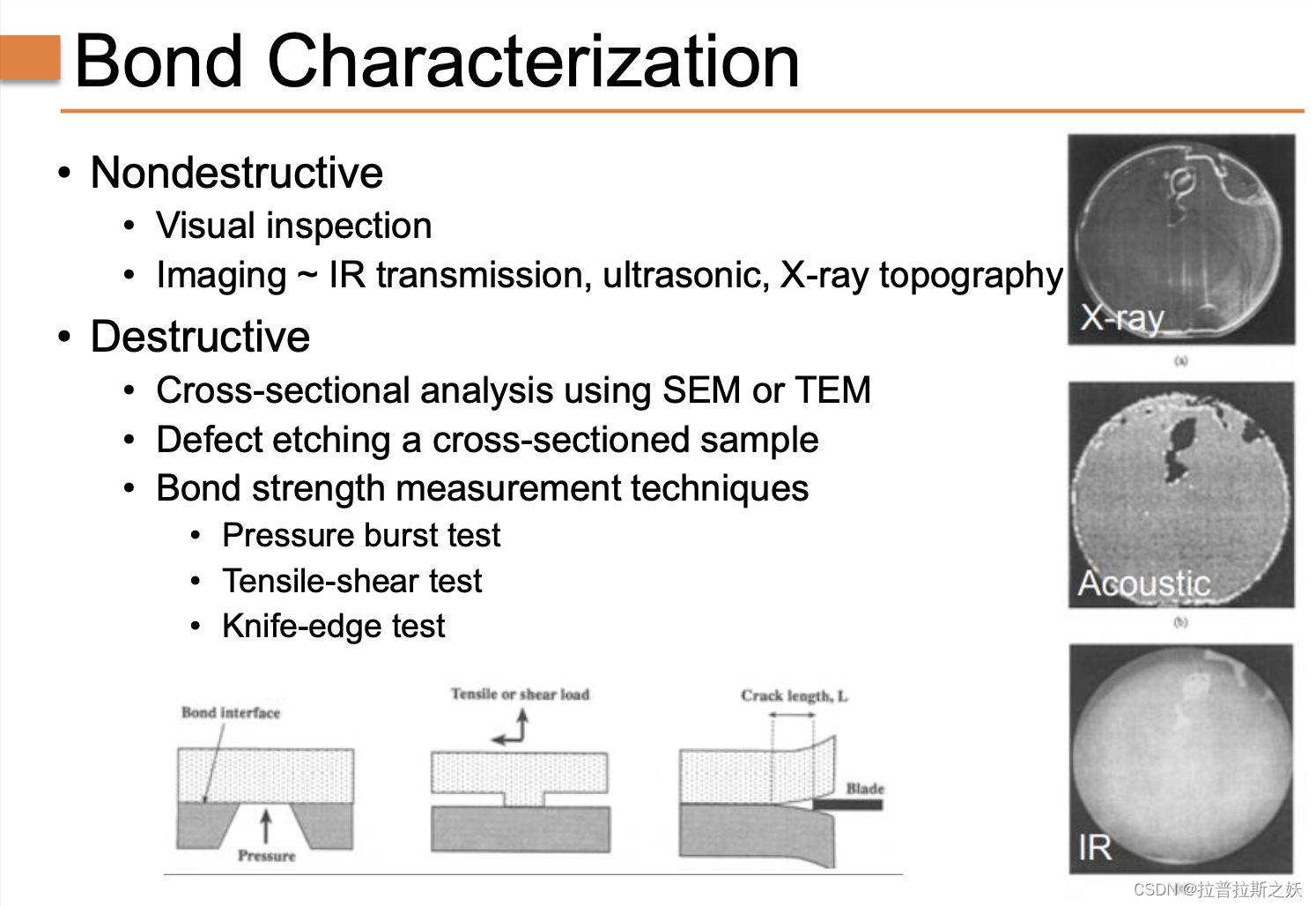

Bond Characterization

分析方法

-

无损检测 (Nondestructive)

-

目视检查 (Visual Inspection):通过显微镜或其他光学方法检查键合表面,识别明显的缺陷和不均匀性。

-

成像技术 (Imaging Techniques):

- 红外透射 (IR Transmission):使用红外光透射成像检测晶圆中的气泡或不均匀区域。

- 超声波 (Ultrasonic):利用声波在材料中的传播特性来检测键合界面上的缺陷。

- X射线拓扑成像 (X-ray Topography):使用X射线成像来识别材料内部和表面结构的缺陷。

-

图示:

- X-ray:X射线成像的图像示例,显示晶圆内部结构。

- Acoustic:超声波成像的图像示例,显示键合界面上的气泡或空隙。

- IR:红外成像的图像示例,显示晶圆上的热分布和潜在缺陷区域。

-

-

破坏性检测 (Destructive)

-

截面分析 (Cross-Sectional Analysis):使用扫描电子显微镜(SEM)或透射电子显微镜(TEM)进行横截面观察,详细分析键合界面的结构。

-

缺陷蚀刻 (Defect Etching):通过化学蚀刻暴露横截面的缺陷,进一步分析键合区域的完整性。

-

键合强度测量 (Bond Strength Measurement Techniques):

- 压力爆破测试 (Pressure Burst Test):通过施加压力直到键合界面破裂,测量其强度。

- 拉伸剪切测试 (Tensile-Shear Test):施加拉伸或剪切力以测量键合界面的粘合强度。

- 刀刃测试 (Knife-Edge Test):使用刀片切割界面并测量裂纹扩展,以评估键合强度。

-

图示:

- 压力爆破测试:示意图展示了如何在界面上施加压力以测试其强度。

- 拉伸剪切测试:示意图展示了在界面上施加拉伸或剪切力的过程。

- 刀刃测试:示意图展示了使用刀片切割并测量裂纹扩展的测试方法。

-

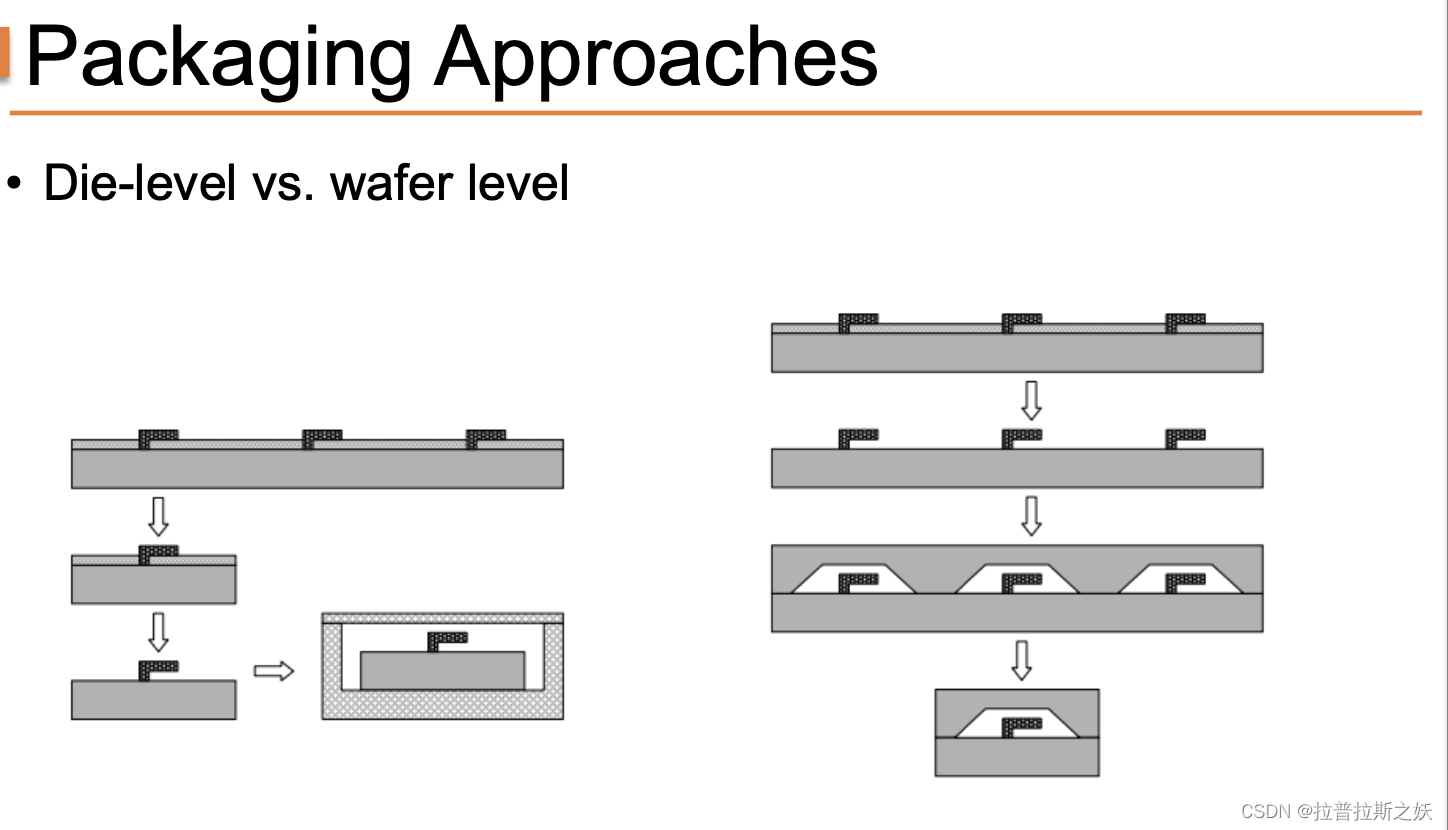

Packaging

比较芯片级与晶圆级封装

-

芯片级封装 (Die-Level Packaging)

- 描述:图示显示了在芯片级进行MEMS封装的过程:

- 步骤:

- 在晶圆上制造多个独立的MEMS器件。

- 将每个器件从晶圆上切割下来(单独的芯片)。

- 每个芯片被单独封装在各自的封装体中。

- 步骤:

- 优势:适合小批量生产和高定制化的MEMS器件。

- 缺点:封装过程复杂、成本高,适合单一器件的封装。

- 描述:图示显示了在芯片级进行MEMS封装的过程:

-

晶圆级封装 (Wafer-Level Packaging)

- 描述:图示显示了在晶圆级进行MEMS封装的过程:

- 步骤:

- 在晶圆上制造多个MEMS器件。

- 在晶圆级进行整体封装。

- 将封装后的晶圆切割成单独的封装MEMS芯片。

- 步骤:

- 优势:适合大批量生产,成本较低,效率高。

- 缺点:初始开发复杂度较高,但在规模生产中具有成本优势。

- 描述:图示显示了在晶圆级进行MEMS封装的过程:

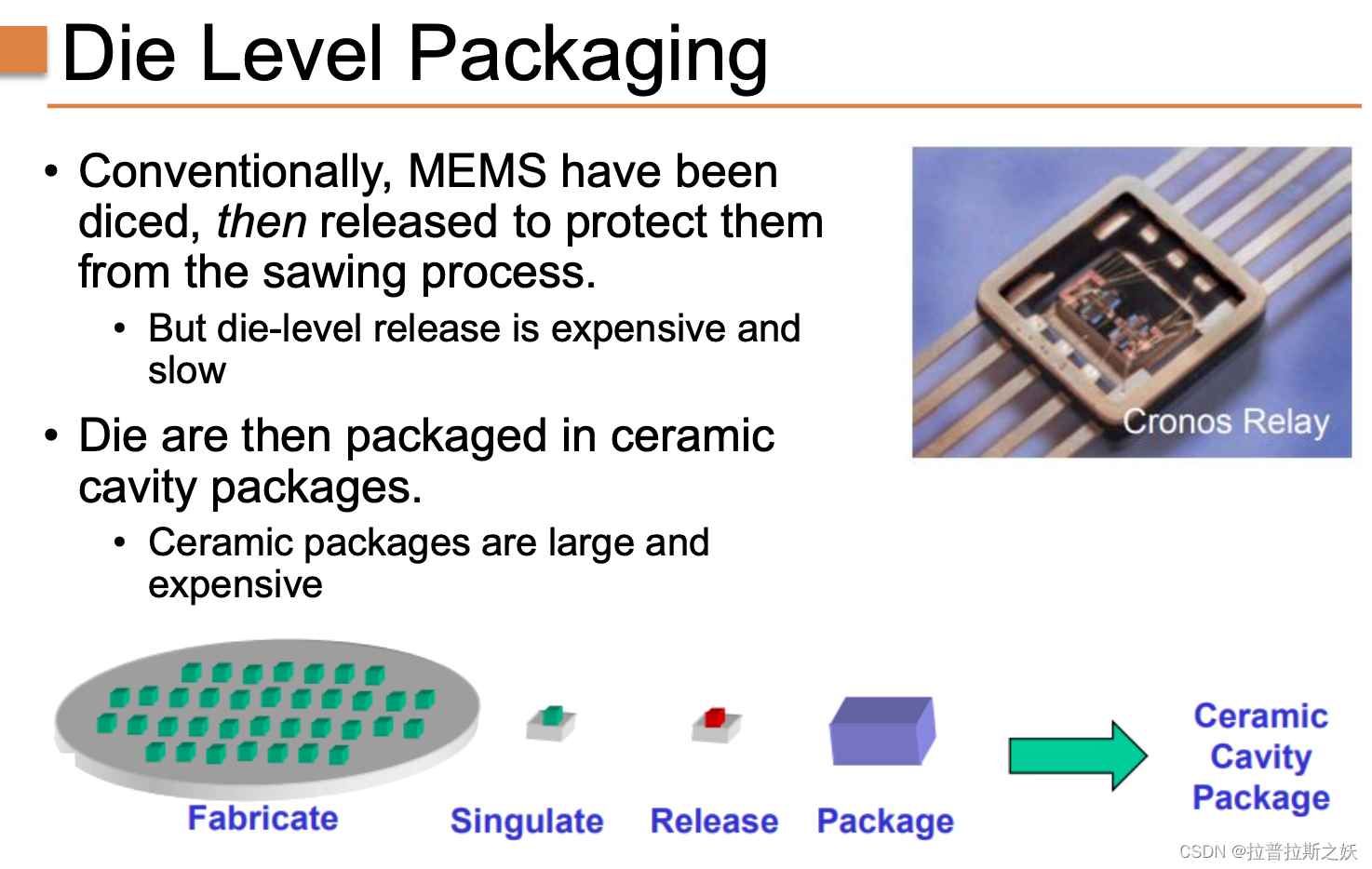

Die Level Packaging

描述

- 传统方法:MEMS器件通常是在切割后进行释放,以保护器件不受切割过程的损伤。

- 过程:

- 制造 (Fabricate):在晶圆上制造多个MEMS器件。

- 切割 (Singulate):将每个MEMS器件从晶圆上切割下来。

- 释放 (Release):对每个芯片进行后续处理,如释放微机械结构。

- 封装 (Package):每个芯片单独封装到陶瓷或其他封装体中。

- 缺点:

- 成本高且慢 (Expensive and slow):芯片级的释放和封装步骤成本较高,效率较低。

- 大尺寸和高成本 (Large and expensive):陶瓷封装体通常体积较大,成本较高。

图示

- 左侧图示:展示了Cronos继电器的芯片级封装。

- 下方图示:展示了典型的芯片级封装流程图,从制造到最终封装的各个步骤。

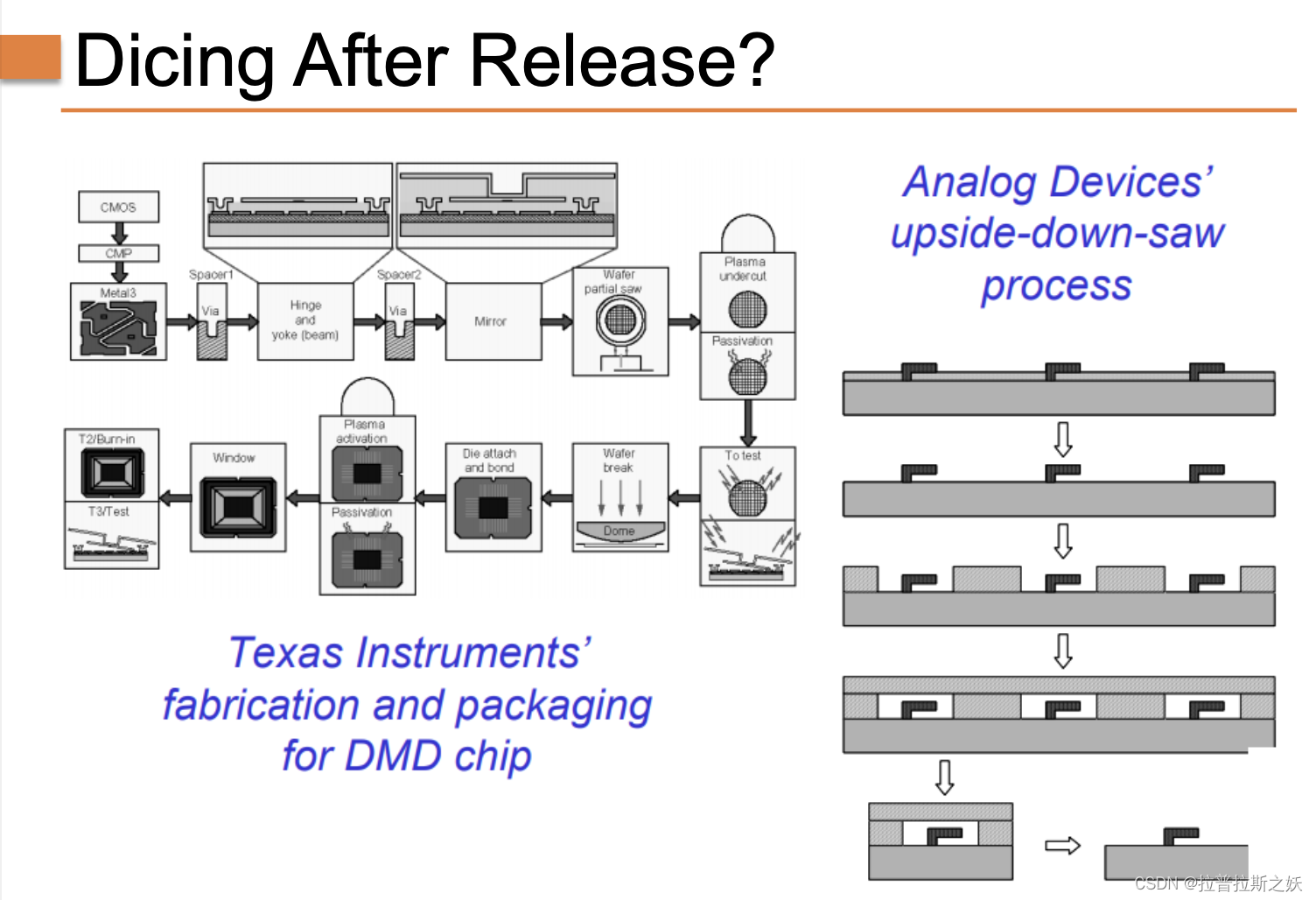

Dicing After Release?

描述

- 替代方法:在一些情况下,可以在释放后进行切割,以减少MEMS器件在切割过程中的损伤。

- 应用:

- 德州仪器 (Texas Instruments):

- 工艺流程:显示了DMD(数字微镜设备)芯片的制造和封装过程:

- 在晶圆级进行一系列处理(如等离子活化、钝化等),然后将每个芯片从晶圆上切割下来并进行封装。

- 工艺流程:显示了DMD(数字微镜设备)芯片的制造和封装过程:

- 模拟设备公司 (Analog Devices):

- 上下倒锯工艺 (Upside-Down-Saw Process):

- 采用特殊的切割方法,将已经释放的MEMS器件从晶圆上切割下来,以减少切割损伤。

- 上下倒锯工艺 (Upside-Down-Saw Process):

- 德州仪器 (Texas Instruments):

- 优缺点:

- 优势:可以更好地保护MEMS器件,减少切割过程中可能的损伤。

- 挑战:需要复杂的工艺控制,以确保切割后的器件完整性和功能性。

图示

- 左侧图示:显示了德州仪器的DMD芯片的制造和封装流程,从最初的晶圆制造到最终的芯片封装。

- 右侧图示:展示了模拟设备公司上下倒锯工艺的示意图,详细说明了每一步骤如何处理晶圆和器件。

芯片级封装适合于高定制化和小批量的应用,但成本高,效率较低。晶圆级封装在大批量生产中具有成本和效率优势,适合标准化的大规模生产。释放后切割提供了一种减少MEMS器件损伤的方法,但需要更加复杂的工艺控制。根据具体应用需求选择合适的封装方法,可以优化生产成本、效率和器件性能。

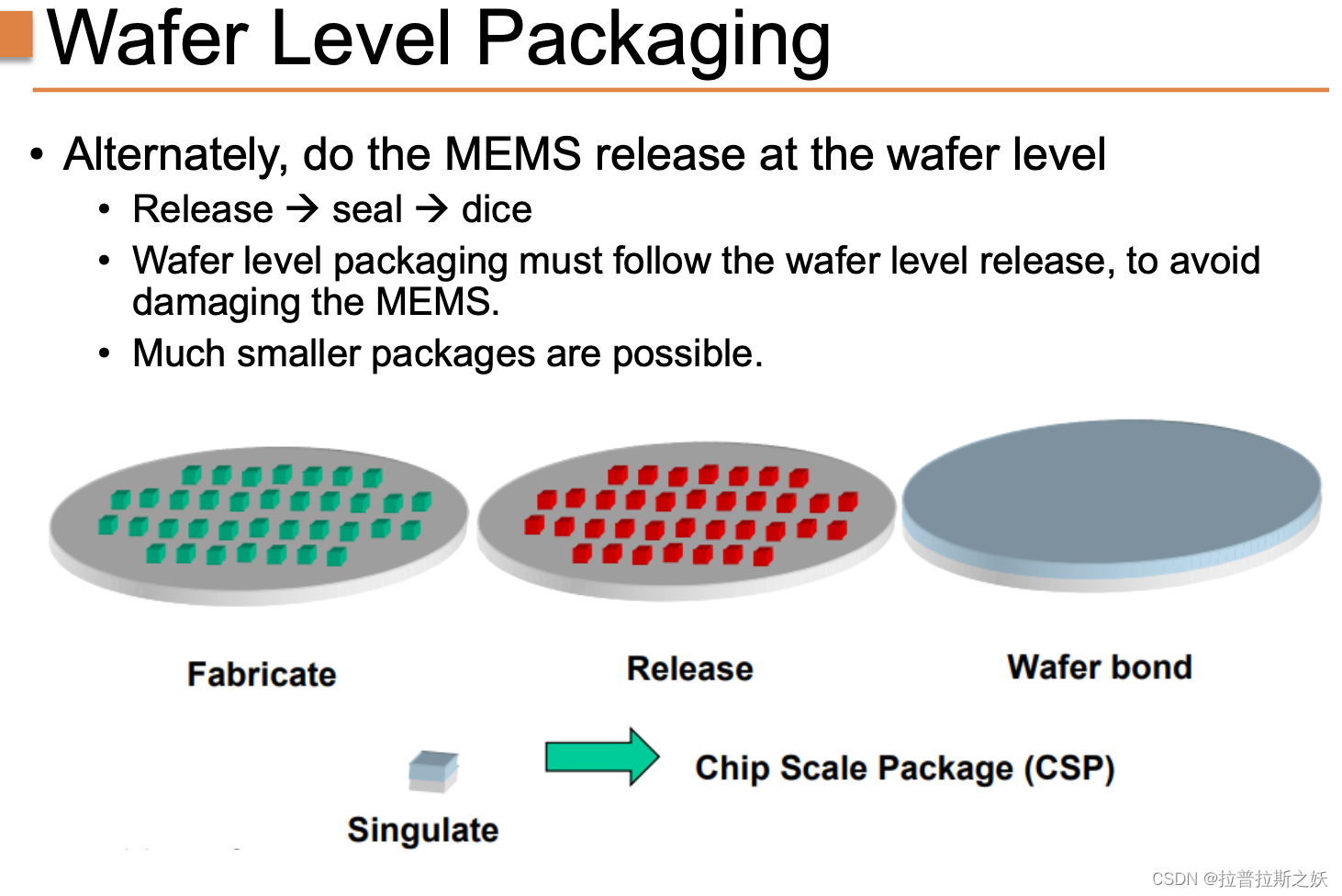

Wafer Level Packaging

概述

晶圆级封装是一种在晶圆级别完成MEMS器件封装的工艺,整个封装过程在晶圆上进行,然后再进行切割和分离。这种方法可以显著减少封装尺寸,提升生产效率。

步骤

-

制造 (Fabricate):

- 在晶圆上制造多个MEMS器件。这个阶段通常包括微机械结构的形成和电路的集成。

-

释放 (Release):

- 在晶圆上完成MEMS结构的释放。这一步是为了使微机械结构脱离基底或者达到所需的工作状态。

- 释放过程需要非常精确,以避免损伤器件。

-

晶圆键合 (Wafer Bond):

- 将已经释放的MEMS器件与另一个保护晶圆进行键合,以形成最终的封装。这一步提供了保护并有助于封装的气密性。

- 键合完成后,可以进行整体的封装测试和检查。

-

切割 (Dice):

- 最后,将封装好的晶圆切割成单个封装的MEMS芯片。这一步骤使得每个MEMS器件都被封装在一个小型的芯片封装中,称为芯片级封装(Chip Scale Package, CSP)。

优势

- 减小封装尺寸:晶圆级封装使得封装可以更紧凑,更小。

- 保护器件:在键合和封装过程中保护MEMS结构,减少损坏风险。

图示

- 图示:展示了从制造、释放、晶圆键合到切割的整个晶圆级封装流程。

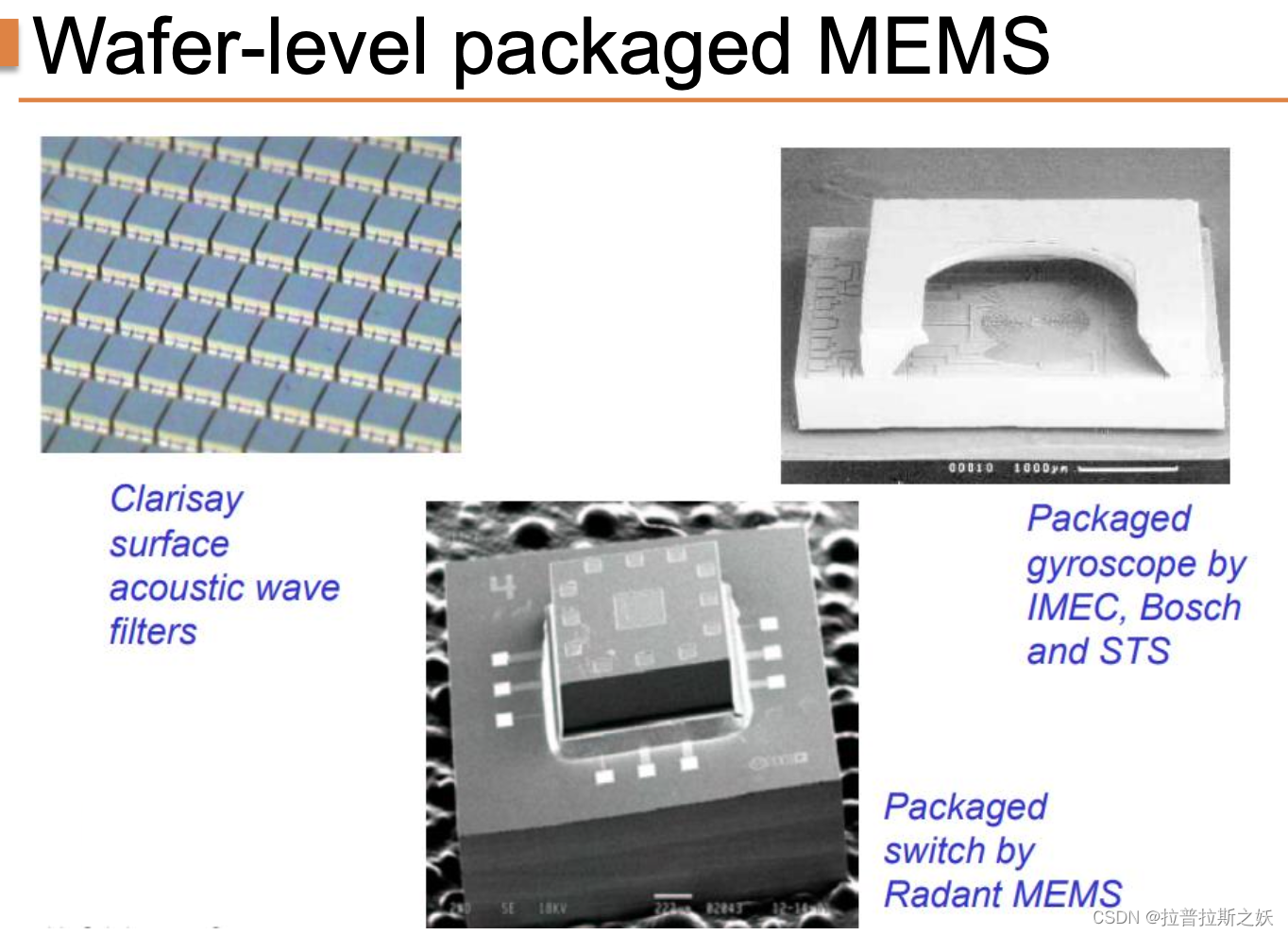

Wafer-Level Packaged MEMS

描述

展示了一些典型的采用晶圆级封装的MEMS器件,表明这种方法在实际应用中的效果和优势。

-

Clarisay表面声波滤波器 (Clarisay Surface Acoustic Wave Filters)

- 描述:这些器件使用晶圆级封装技术实现高密度集成,适用于高频信号处理应用。

-

IMEC、博世和STS封装的陀螺仪 (Packaged Gyroscope by IMEC, Bosch, and STS)

- 描述:展示了晶圆级封装的陀螺仪,这些器件在封装过程中保护了敏感的机械结构。

-

Radant MEMS封装的开关 (Packaged Switch by Radant MEMS)

- 描述:展示了使用晶圆级封装技术的微型开关,这种封装提高了器件的可靠性和小型化。

图示

- 左上角图示:展示了Clarisay的表面声波滤波器,显示了高密度排列的MEMS器件。

- 右上角图示:展示了IMEC、博世和STS封装的陀螺仪,显示了高精度的封装结构。

- 下方图示:展示了Radant MEMS封装的开关,显示了其精密的封装技术。

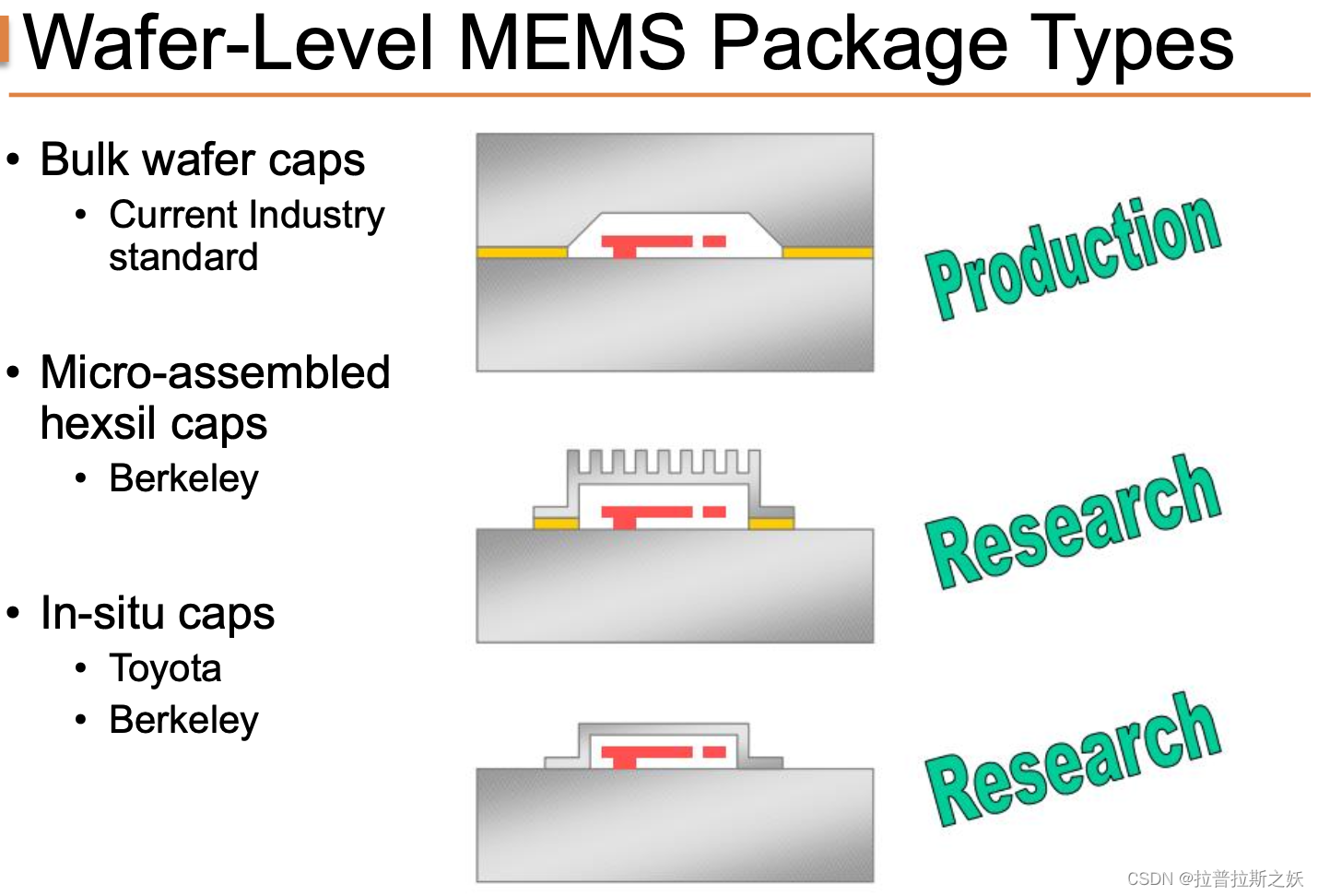

Wafer-Level MEMS Package Types

描述

展示了晶圆级MEMS封装的几种类型,说明了不同封装方法的应用场景。

-

整体晶圆封帽 (Bulk Wafer Caps)

- 描述:当前工业标准,适用于大规模生产,封装可靠。

- 应用:量产。

-

微装配Hexsil封帽 (Micro-Assembled Hexsil Caps)

- 描述:由伯克利开发的微型封帽技术,用于研究阶段的高精度应用。

- 应用:研究。

-

原位封帽 (In-Situ Caps)

- 描述:由丰田和伯克利开发的技术,用于原位形成封帽,适合研究应用。

- 应用:研究。

图示

- 上方图示:展示了整体晶圆封帽的结构,显示了标准工业应用中的封装方式。

- 中间图示:展示了微装配Hexsil封帽,适用于研究阶段的应用。

- 下方图示:展示了原位封帽的结构,适合研究开发的应用。

Bulk Wafer Caps 整体晶圆封帽

整体晶圆封帽是当前MEMS封装的工业标准,它涉及在整个晶圆上制造封帽,并在封装后切割成单个器件。这种方法提供了坚固、气密的封装环境。

示例

-

摩托罗拉加速度计 (Motorola Accelerometers)

- 使用整体晶圆封帽技术,提供了对加速度传感器的保护和封装。

-

博世陀螺仪 (Bosch Gyroscopes)

- 利用这种封装方法,实现了对精密陀螺仪的保护,确保其在高精度应用中的稳定性。

-

Clarisay表面声波滤波器 (Clarisay SAW Filter)

- 整体晶圆封帽用于高频滤波器,提供了必要的环境保护。

-

Radant MEMS开关 (Radant MEMS Switch)

- 使用整体晶圆封帽技术,提供了对微型开关的气密封装。

优缺点 (Pros and Cons)

-

优点:

- 坚固 (Robust):提供了结构上坚固的封装,能够承受物理应力。

- 气密 (Hermetic):保证了封装的气密性,适合环境敏感的MEMS器件。

- 晶圆级 (Wafer-Level):封装在晶圆级完成,提高了生产效率。

-

缺点:

- 大芯片面积需求 (Large On-Chip Area Required for Seal Ring):密封环需要较大的芯片面积,这可能会限制器件的尺寸优化。

图示

- 右侧图示:展示了整体晶圆封帽的剖面视图,显示了封帽如何覆盖在MEMS器件上。

第二页:微装配封帽

标题: Micro-Assembled Caps

描述

微装配封帽涉及在供体晶圆上制造微封帽,然后通过晶圆键合和分离将其转移到目标晶圆上。这种方法减少了封装面积,并且成本较低。

过程

-

在供体晶圆上制造微封帽 (Fabricate Microcaps on Donor Wafer):

- 在供体晶圆上制造微型封帽,这些封帽用于封装MEMS器件。

-

将微封帽转移到目标晶圆 (Transfer Microcaps to Target Wafer):

- 通过晶圆键合和分离,将微封帽从供体晶圆转移到目标晶圆上。

- 这种方法允许在目标晶圆上直接形成封帽,从而减少了额外的封装步骤。

-

薄密封环 (Thin Seal Ring):

- 使用薄密封环,只需占用很少的芯片面积(约占传统封帽的1%)。

- 潜在的优势在于这种方法比传统晶圆封帽便宜得多。

图示

- 右侧图示:展示了微装配封帽的示意图,从对准(Align)、键合(Bond)到分离(Separate)的整个过程。

第三页:微装配封帽的制造

标题: Micro-Assembled Cap Fabrication

描述

展示了Hexsil工艺如何制造“蜂窝状”高纵横比结构,这种结构由薄膜沉积形成,用于微装配封帽的制造。

过程

-

蚀刻凹槽 (Recess Etch):

- 在供体晶圆上蚀刻出所需的凹槽结构,形成封帽的初步形状。

-

深沟蚀刻 (Deep Trench Etch):

- 进一步蚀刻形成更深的结构,用于提高封帽的结构强度。

-

沉积和图案化牺牲层 (Deposit & Pattern Sacrificial, Structural Layers):

- 沉积牺牲层和结构层,并对其进行图案化处理,以形成最终的封帽结构。

-

电镀金凸点和密封环 (Electroplate Gold Bumps & Seal Ring):

- 在结构上电镀金凸点和密封环,以确保封帽与目标晶圆的有效键合。

-

释放蚀刻 (Release Etch):

- 通过释放蚀刻将封帽从供体晶圆上分离,并进行热压键合到目标晶圆。

图示

- 图示:展示了微装配封帽制造过程的各个步骤,从蚀刻到最终的封帽形成。

第四页:微封帽装配

标题: Microcap Assembly

描述

展示了Hexsil微封帽在实际应用中的装配,表明这种方法如何在目标晶圆上形成封帽。

-

几个Hexsil封帽装配在裸金芯片上 (Several Hexsil Caps Assembled onto Bare Gold Die)

- 描述:展示了多个Hexsil封帽如何装配到裸金芯片上,提供了封装保护。

-

部分Hexsil封帽装配到Sandia iMEMS芯片上 (Partial Hexsil Cap Assembled onto Sandia iMEMS Chip)

- 描述:展示了部分Hexsil封帽如何装配到MEMS芯片上,提供了必要的封装和保护。

图示

- 左侧图示:展示了多个Hexsil封帽装配在裸金芯片上的实际照片。

- 右侧图示:展示了Hexsil封帽装配在Sandia iMEMS芯片上的照片,表明了封帽在保护MEMS器件方面的应用。

总结

这些幻灯片详细介绍了整体晶圆封帽和微装配封帽的不同方法。整体晶圆封帽提供了坚固和气密的封装,但占用了较大的芯片面积。微装配封帽则通过使用薄密封环和供体晶圆的转移技术,显著减少了封装面积和成本。微装配封帽的制造和装配展示了高精度和高效的封装方法,适用于对封装尺寸和成本有较高要求的MEMS器件。

第一页:原位密封

标题: In Situ Sealing

描述

原位密封是一种在晶圆级释放后,对MEMS器件进行密封的技术。此方法在MEMS制造完成并释放后,直接在原位进行封装。

步骤

-

在MEMS上方制造微外壳 (Microshells Fabricated Over MEMS)

- 在MEMS器件的上方制造微型外壳,以保护和密封微机械结构。

-

通过通孔释放蚀刻释放MEMS (Release Etch Frees MEMS Through Access Holes)

- 通过预先设计的通孔进行蚀刻,将MEMS结构从基底释放出来。

-

使用薄膜沉积密封通孔 (Access Holes Are Sealed Using Film Deposition)

- 通过薄膜沉积技术密封这些通孔,可能在低压下进行。

- 薄膜沉积通常使用多种材料来确保密封性和气密性。

优点

- 简化了封装过程 (Simplifies Packaging Process)

- 直接在原位完成封装,减少了传统封装所需的多个步骤。

缺点

- 增加了制造工艺的复杂性 (Adds Development to Fabrication Process)

- 在制造过程中需要额外的开发和工艺步骤,增加了复杂性。

图示

- 上方图示:展示了原位密封的原理图,包括在硅基底上方的聚硅薄膜和反应密封区域。

- 下方图示:展示了原位密封的实际应用,显示了微外壳和MEMS结构的电子显微镜图像。

第二页:气密性

标题: Hermeticity

描述

气密性封装指的是具有可接受气密程度的内腔封装,用于防止气体泄漏和保护内部的MEMS器件。

特性

-

气密封装 (Hermetic Package)

- 气密封装具有内腔,能够有效地防止气体的渗透,保持内部环境的稳定。

-

材料 (Materials)

- 气密材料 (Hermetic Materials):包括金属、玻璃和半导体,这些材料具有良好的气密性。

- 非气密材料 (Non-Hermetic Materials):塑料密封则通常不具备良好的气密性,容易发生气体渗透。

-

吸气剂 (Getters)

- 作用 (Function):某些金属合金可以吸收并与封装内的气体反应,以保持较低的压力。

- 应用 (Applications):用于在气密封装中控制内部气压,防止气体影响器件性能。

图示

- 左下角图示:展示了不同材料(如硅橡胶、环氧树脂、氟化碳、玻璃和金属)的气体渗透率与时间和厚度的关系。

- 右下角图示:展示了气密封装的剖面图,说明了玻璃和硅之间的气密密封、金属导体以及可能存在的气体泄漏通道。

总结

这些幻灯片详细介绍了原位密封和气密性封装在MEMS器件中的应用。原位密封通过在MEMS制造完成后直接在原位进行封装,简化了封装过程,但增加了制造工艺的复杂性。气密性封装通过使用气密材料和吸气剂来维持内部气体环境的稳定性,提供了对MEMS器件的有效保护。这些方法在保证MEMS器件性能和可靠性方面发挥了关键作用,适用于对封装气密性和微结构保护有高要求的应用。

Wafer Level Packaging and Interconnects

在微机电系统 (MEMS) 封装中,晶圆级封装(Wafer Level Packaging, WLP) 是一种先进的封装方法,它在晶圆上完成所有封装步骤,而不是在单个芯片上进行封装。这种方法提供了较高的集成度和显著的小型化优势,同时也有助于提高性能和降低成本。

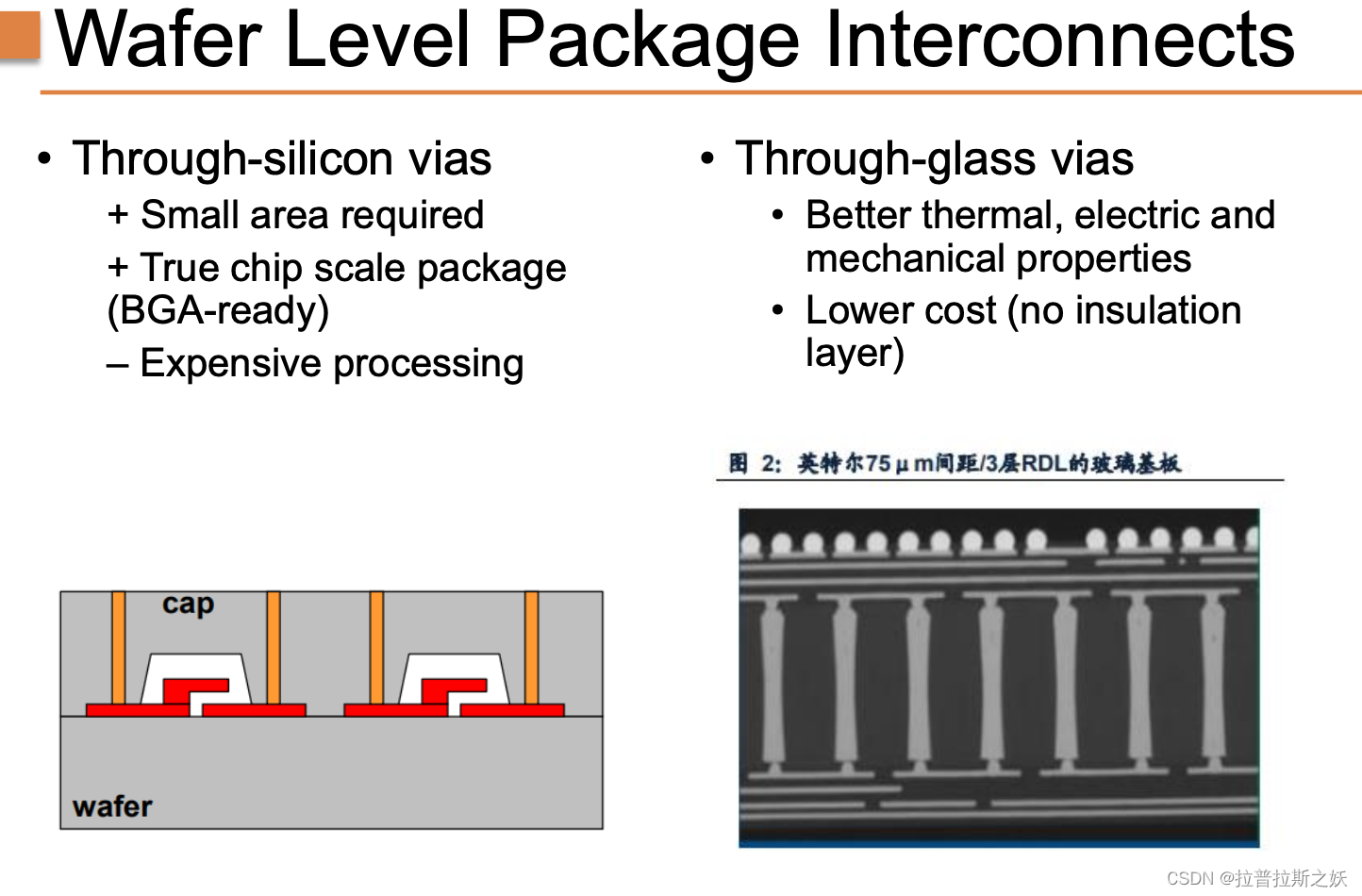

1. 晶圆级封装的基本方法

Through-Silicon Vias (TSVs) 和 Through-Glass Vias (TGVs) 是两种常见的晶圆级封装方法:

-

Through-Silicon Vias (TSVs):

- 优点:TSV 占用较小的面积,适用于真正的芯片级封装(BGA-ready)。

- 缺点:加工成本较高。

- 结构:TSV 技术使用硅通孔将芯片与基板或封装内的其他组件相连,形成高密度的垂直互连结构。

-

Through-Glass Vias (TGVs):

- 优点:TGV 提供更好的热、电和机械性能,成本较低(无需绝缘层)。

- 结构:TGV 是在玻璃基板上制作的通孔,能承受较高的热应力,并且电学和机械性能优越。

图示:

- TSV(左图):显示硅通孔如何在芯片上形成与下层基板的垂直互连。

- TGV(右图):通过玻璃基板制作的通孔,显示其电学和机械优点。

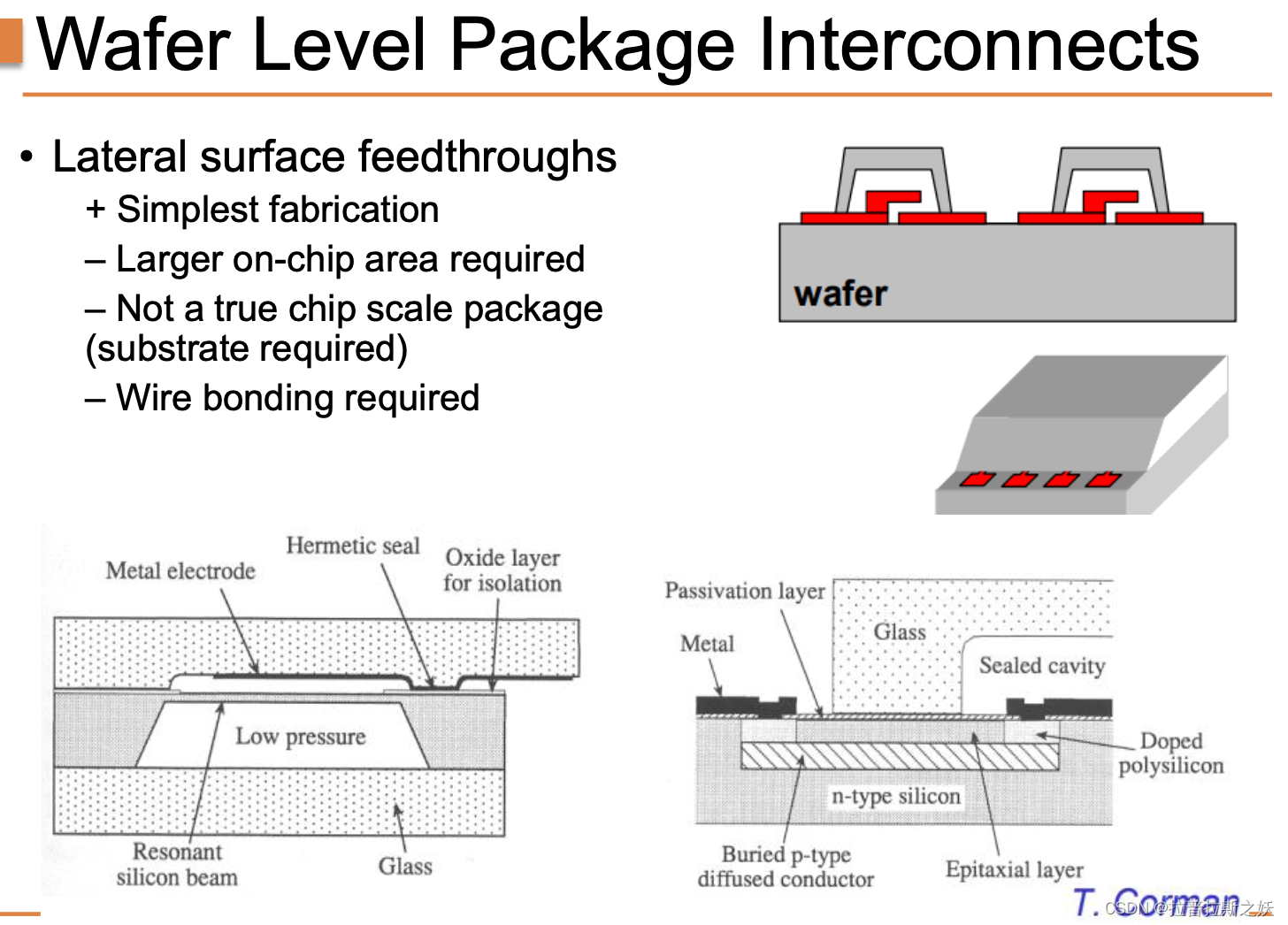

2. 晶圆级封装中的其他互连方法

- Lateral Surface Feedthroughs:

- 优点:制造最简单。

- 缺点:需要更大的芯片面积,不是真正的芯片级封装(需要基板),需要引线键合。

- 结构:该方法在芯片侧面制作贯穿的导线,用于连接芯片与外部引线。

图示:

-

显示侧面通道如何与芯片表面平行运行,并连接到外部引线。

-

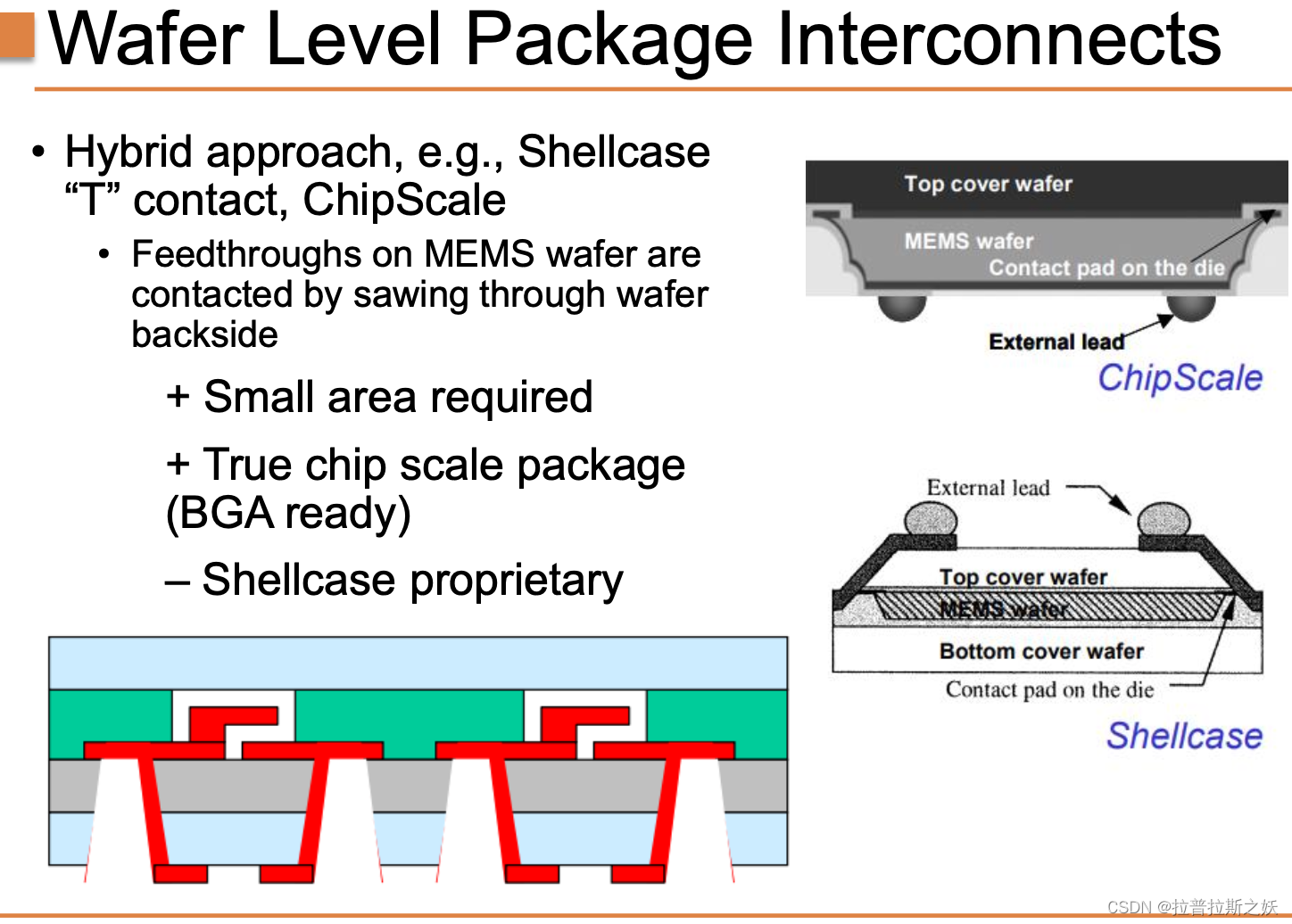

Hybrid Approach (Shellcase, ChipScale):

- 优点:需要较小的面积,真正的芯片级封装(BGA-ready)。

- 缺点:Shellcase 为专有技术,可能存在兼容性和成本问题。

- 结构:这种方法结合了芯片背面的锯切技术,以实现更有效的封装和互连。

图示:

- 描述了 Shellcase 和 ChipScale 技术如何在封装中结合使用,为封装提供高集成度和小型化。

In Situ Sealing

In Situ Sealing 是指在晶圆级封装过程中,直接在晶圆上进行 MEMS 器件的密封。这个方法旨在简化封装工艺,并在晶圆层面上完成所有密封步骤,从而避免在芯片级进行复杂的封装操作。

要点:

- 微壳:在 MEMS 上制作微壳,通过释放刻蚀在通孔中释放 MEMS。

- 封装孔的密封:使用薄膜沉积(可能在低压下)密封通孔。

- 优点:简化封装过程。

- 缺点:增加了制造工艺的复杂性。

图示:

- 显示微壳如何覆盖 MEMS 器件,并通过在 MEMS 上进行的薄膜沉积和密封过程,保持封装的完整性。

Hermeticity

Hermeticity 指的是封装内部腔体的气密性,确保封装内的气体环境保持恒定,从而保护 MEMS 器件的功能和寿命。

要点:

- 材料:金属、玻璃、半导体被认为是气密材料,而塑料密封并不气密。

- 吸气剂:某些金属合金能够吸收和与封装中的气体反应,以保持低压力。

图示:

- 描绘了不同材料的透气性以及如何通过气密封装保持内部环境的稳定。

Interconnects in Wafer Level Package

在晶圆级封装中,互连的设计对封装的性能和集成度有着重要影响。下面详细讲解了晶圆级封装中的几种互连方法:

1. Through-Silicon Vias (TSVs)

Through-Silicon Vias (TSVs) 是在硅晶圆上形成贯穿的通孔,用于实现芯片与封装层之间的电气连接。

优点:

- 占用面积小,适用于芯片级封装(BGA-ready)。

- 提供了高密度的垂直互连,增强了芯片的集成度。

缺点:

- 制造过程复杂且成本较高。

图示:

- TSV 的结构图,显示通孔如何贯穿芯片,与封装层进行电气连接。

2. Through-Glass Vias (TGVs)

Through-Glass Vias (TGVs) 则是在玻璃基板上形成的通孔,常用于需要优异的电气和机械性能的应用。

优点:

- 提供更好的热、电、机械性能。

- 制造成本相对较低,因为不需要绝缘层。

图示:

- TGV 的结构图,显示其如何利用玻璃基板提供高性能的电气连接。

3. Lateral Surface Feedthroughs

Lateral Surface Feedthroughs 是一种侧面通道技术,通过在芯片侧面形成导线,实现芯片与外部的电气连接。

优点:

- 制造最为简单,适合低成本和快速原型制作。

缺点:

- 需要更大的芯片面积,增加了封装的复杂性。

- 不是真正的芯片级封装,通常需要基板支持。

图示:

- 显示侧面通道如何与芯片表面平行布置,并连接到外部电气系统。

4. Hybrid Approach

Hybrid Approach 结合了多种封装和互连技术,以实现更高效的封装方式。这种方法通常包括:

- Shellcase 和 ChipScale 技术,通过在 MEMS 晶圆背面进行锯切,实现更高效的电气连接。

- 优点:需要较小的面积,适用于真正的芯片级封装(BGA-ready)。

- 缺点:Shellcase 为专有技术,可能存在兼容性和成本问题。

图示:

- 描绘了 Hybrid Approach 的结构,显示了如何结合不同的封装和互连技术,提供高性能的封装解决方案。

总结

晶圆级封装方法提供了 MEMS 器件小型化和高性能的解决方案。通过使用 TSV、TGV、侧面通道和混合技术,可以在保证封装气密性的同时,实现高效的电气互连。这些方法各有优缺点,选择合适的封装技术需要根据具体应用需求、成本和制造工艺进行权衡。

-

相关阅读:

C++ 指向数组的指针

微信小程序 解决 当套在scroll-view中后 wx.pageScrollTo 函数失效问题解决

数据开发与数据治理的关系

做自媒体月入一千的有超过百分之十吗?

备战数学建模42-缺失值和异常值的处理方法(攻坚战6)

汇聚行业领先产品 828 B2B企业节发布百款重磅新品

如何给国产32位单片机添加SEGGER RTT 日志打印

1353016-70-2,DBCO-COOH,DBCO-Acid,二苯并环辛炔-羧酸科研专用

基于JAVA抑郁症患者博客交流平台计算机毕业设计源码+系统+数据库+lw文档+部署

太炫酷,3分钟学会,视频倒放技能

- 原文地址:https://blog.csdn.net/weixin_45603120/article/details/139712215