-

STM32的GPIO控制寄存器开发

寄存器GPIO控制

寄存器地址

寄存器地址计算

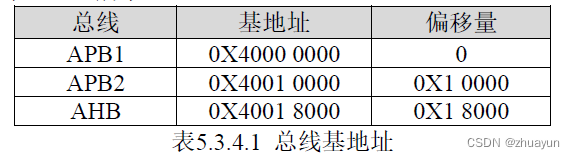

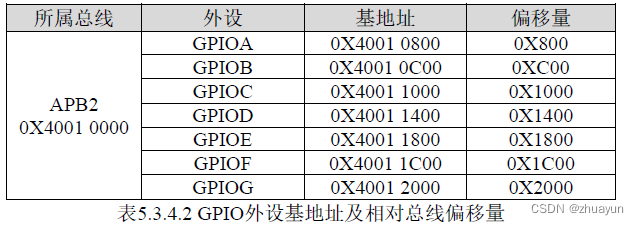

某个寄存器地址,由三个参数决定:1、总线基地址(BUS_BASE_ADDR);2,外设基于总线基地址的偏移量(PERIPH_OFFSET);3,寄存器相对外设基地址的偏移量(REG_OFFSET)。可以表示为:

寄存器地址 = BUS_BASE_ADDR + PERIPH_OFFSET + REG_OFFSET

相关寄存器

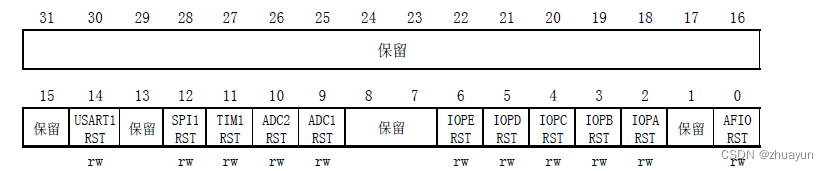

APB2外设时钟使能寄存器(RCC_APB2ENR)

-

复位和时钟控制(RCC) 0x4002 1000 - 0x4002 13FF

-

偏移地址:0x18 ;其地址为0x4002 1018

-

复位值:0x0000 0000

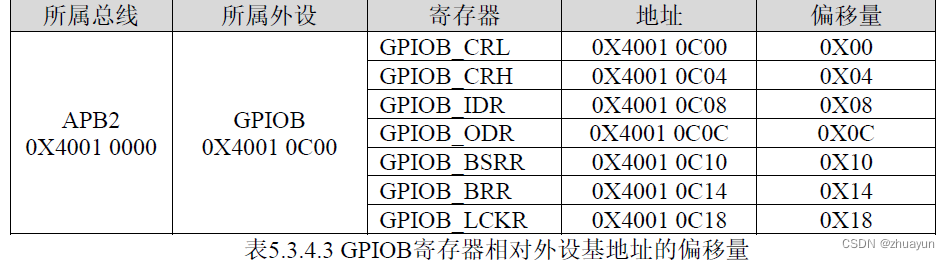

端口配置低寄存器(GPIOx_CRL) (x=A…E)

控制GPIOx的0-7针脚

- 偏移地址:0x00 复位值:0x4444 4444

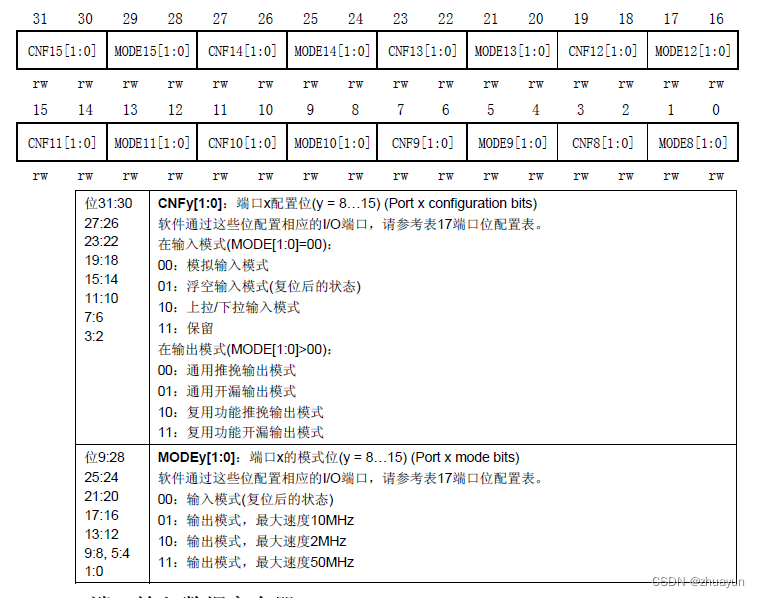

端口配置高寄存器(GPIOx_CRH) (x=A…E)

控制GPIO的8-15针脚

- 偏移地址:0x04 复位值:0x4444 4444

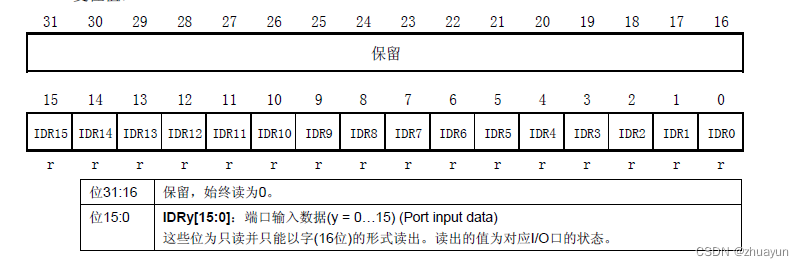

端口输入数据寄存器(GPIOx_IDR) (x=A…E)

- 地址偏移:0x08 复位值:0x0000 XXXX

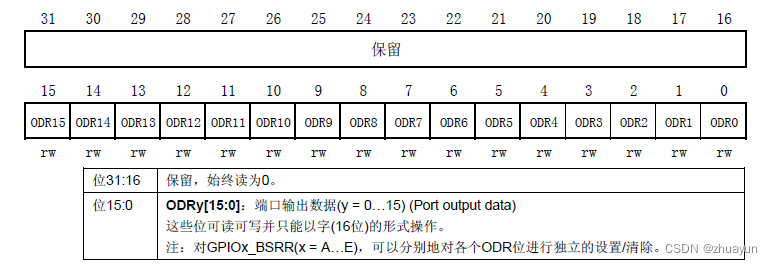

端口输出数据寄存器(GPIOx_ODR) (x=A…E)

- 地址偏移:0Ch 复位值:0x0000 0000

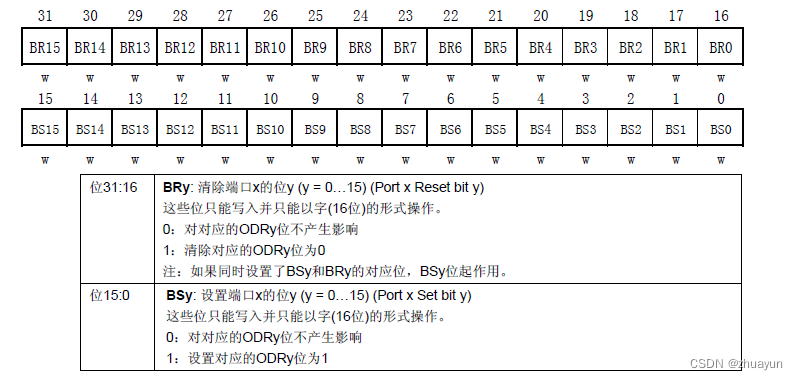

端口位设置/清除寄存器(GPIOx_BSRR) (x=A…E)

- 地址偏移:0x10 复位值:0x0000 0000

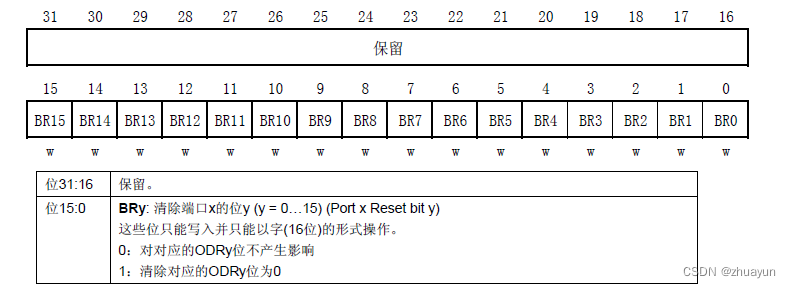

端口位清除寄存器(GPIOx_BRR) (x=A…E)

- 地址偏移:0x14 复位值:0x0000 0000

端口配置锁定寄存器(GPIOx_LCKR) (x=A…E)

- 地址偏移:0x18 复位值:0x0000 0000

- 当对相应的端口位执行了LOCK序列后,在下次系统复位之前将不能再更改端口位的配置。

2.简单GPIO控制

每个GPI/O端口有两个32位配置寄存器(GPIOx_CRL,GPIOx_CRH),两个32位数据寄存器(GPIOx_IDR和GPIOx_ODR),一个32位置位/复位寄存器(GPIOx_BSRR),一个16位复位寄存器(GPIOx_BRR)和一个32位锁定寄存器(GPIOx_LCKR)。 根据数据手册中列出的每个I/O端口的特定硬件特征, GPIO端口的每个位可以由软件分别配置成多种模式。

- 输入浮空

- 输入上拉

- 输入下拉

- 模拟输入

- 开漏输出

- 推挽式输出

- 推挽式复用功能

- 开漏复用功能

- 每个I/O端口位可以自由编程,然而I/0端口寄存器必须按32位字被访问(不允许半字或字节访问)。GPIOx_BSRR和GPIOx_BRR寄存器允许对任何GPIO寄存器的读/更改的独立访问;这样,在读和更改访问之间产生IRQ时不会发生危险。

//#define GPIOB_CRH_addr 0X40010C04 //#define GPIOB_IDR_addr 0X40010C08 //#define GPIOB_ODR_addr 0X40010C0C //#define GPIOB_BSRR_addr 0X40010C10 //#define GPIOB_BRR_addr 0X40010C14 //#define GPIOB_LCKR_addr 0X40010C18 //#define RCC_APB2ENR_addr 0X4002 1018 //偏移0x18 //#define GPIOB_CRL (*(unsigned int *)(0X40010C00)) //#define GPIOB_CRH (*(unsigned int *)(0X40010C04)) //#define GPIOB_IDR (*(unsigned int *)(0X40010C08)) //#define GPIOB_ODR (*(unsigned int *)(0X40010C0C)) //#define GPIOB_BSRR (*(unsigned int *)(0X40010C10)) //#define GPIOB_BRR (*(unsigned int *)(0X40010C14)) //#define GPIOB_LCKR (*(unsigned int *)(0X40010C18)) #define RCC_APB2ENR (*(unsigned int *)(0X40021018)) #define GPIOB_BASE_addr 0X40010C00 typedef struct{ volatile unsigned int CRL; volatile unsigned int CRH; volatile unsigned int IDR; volatile unsigned int ODR; volatile unsigned int BSRR; volatile unsigned int BRR; volatile unsigned int LCKR; }GPIO; GPIO *GPIO_B=(GPIO*)(GPIOB_BASE_addr); //由于结构体连续分配内存,并且GPIO配置寄存器也是连续的相隔4个字节,故寄存器地址能完整映射到结构体。 int main() { RCC_APB2ENR=8; // GPIOB_CRL = 0XD00000;//00000000 10110000 00000000 0000000; // 配置PB5为复用推挽输出模式速度为50MHz //GPIOB_ODR = 0X10; // //GPIOB_ODR= 0; // GPIO_B->CRH=0X0011; GPIO_B->CRL=0Xd00000; //GPIO_B->ODR|=(1<<5);//低电平驱动LED GPIO_B->ODR|=(1<<8);//高电平驱动有源蜂鸣器 while(1); }- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

-

-

相关阅读:

【课程作业】最优化理论与方法:第一次作业

2020研究生数学建模竞赛C题——面向康复工程的脑电信号分析和判别模型——论文研读

园子的商务合作-腾讯云:欢迎下载《泛智能开启下一代云时代》IDC白皮书

分布式架构篇

c++ nlohmann::json 中文支持

web网页设计期末课程大作业 我的美丽家乡盐城 HTML+CSS+JavaScript

基于Python实现情感分析实验

算法通关村-----透彻理解动态规划

【C进阶】动态内存管理

基于FPGA的spwm产生VHDL

- 原文地址:https://blog.csdn.net/zhuayun/article/details/138090839