-

FPGA-时钟管理单元

时钟管理单元(Clock Management Tile, CMT) :

即时钟管理片,是FPGA器件中一个十分重要的时钟资源。能够对内部和外部的时钟去偏斜、去抖动,同时还支持频率合成、分倍频等功能。

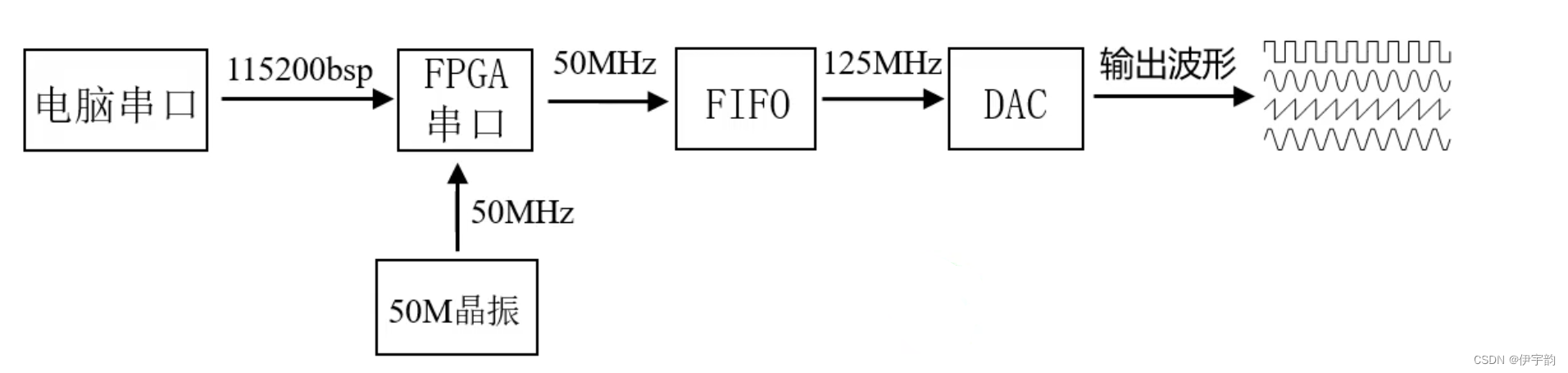

举例,下面这个例子数据从FIFO输出时钟频率为125MHZ,这个时钟频率可以通过50M晶振产生的频率倍频得到,但是时钟质量却很差。

所以,使用CMT生成125MHZ的频率。

那么为什么CMT生成的时钟质量比倍频生成的时钟质量要好呢?

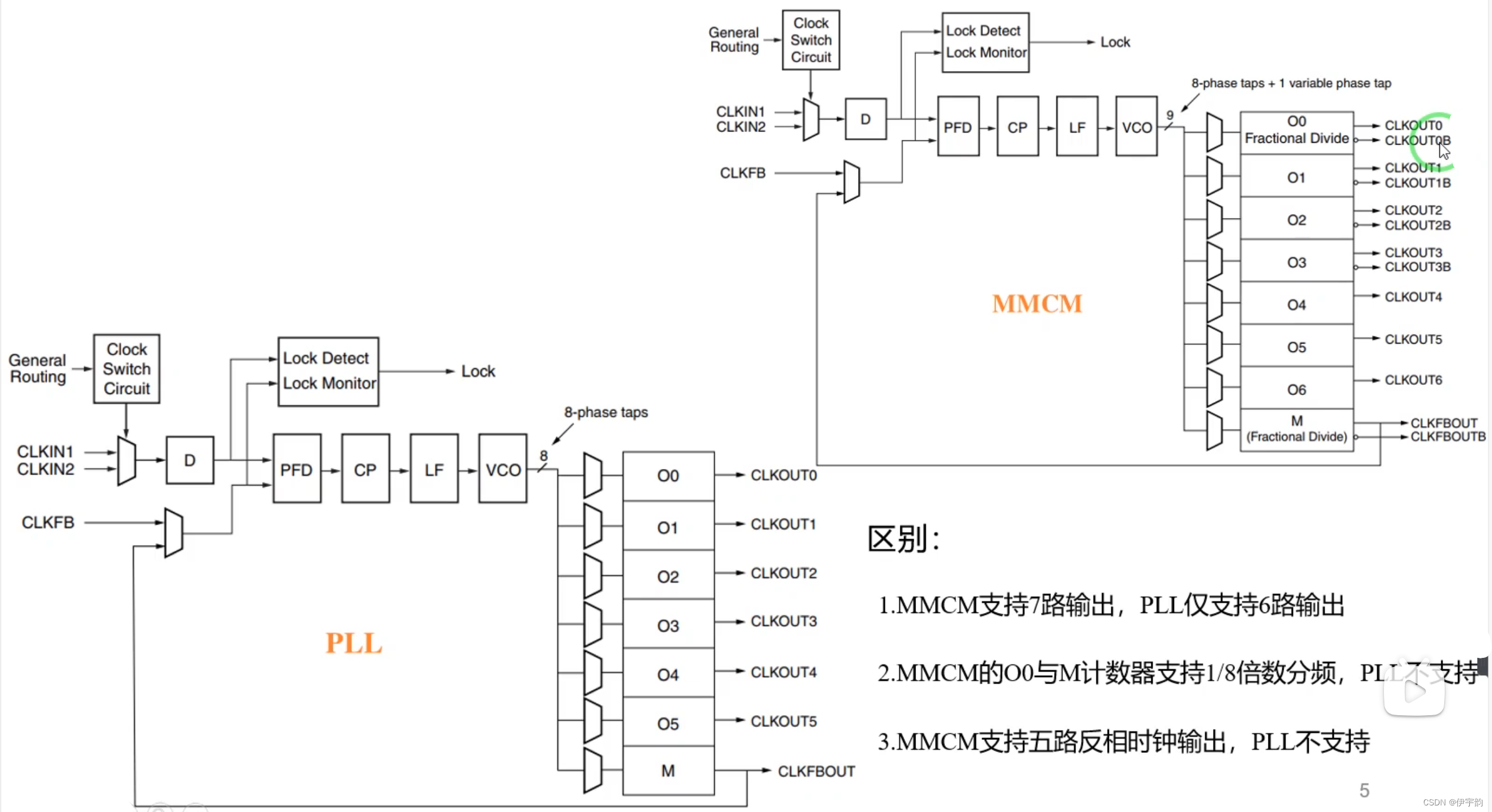

看下图,下图是赛灵思官方手册中给出的CMT的框图

、

、锁相环(PLL,Phase-Locked Loop),是一种反馈控制电路,常常用于利用 外部输入的参考信号控制环路内部振荡信号的频率和相位。锁相环在工作时, 当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的 相位差值,即输出电压与输入电压的相位被锁住,因此得名锁相环。

PLL 就是所说的锁相环,它能通过纯模拟电路,产生一定 范围内频率、相位、占空比等可控的时钟。而 MMCM(Mixed-Mode Clock Manager,混合模式时钟管理器)则是在此之上,通过数字电路设计增加了动态 调相的功能,因此被称为混合模式时钟管理器。

用以下例子来实验:

、

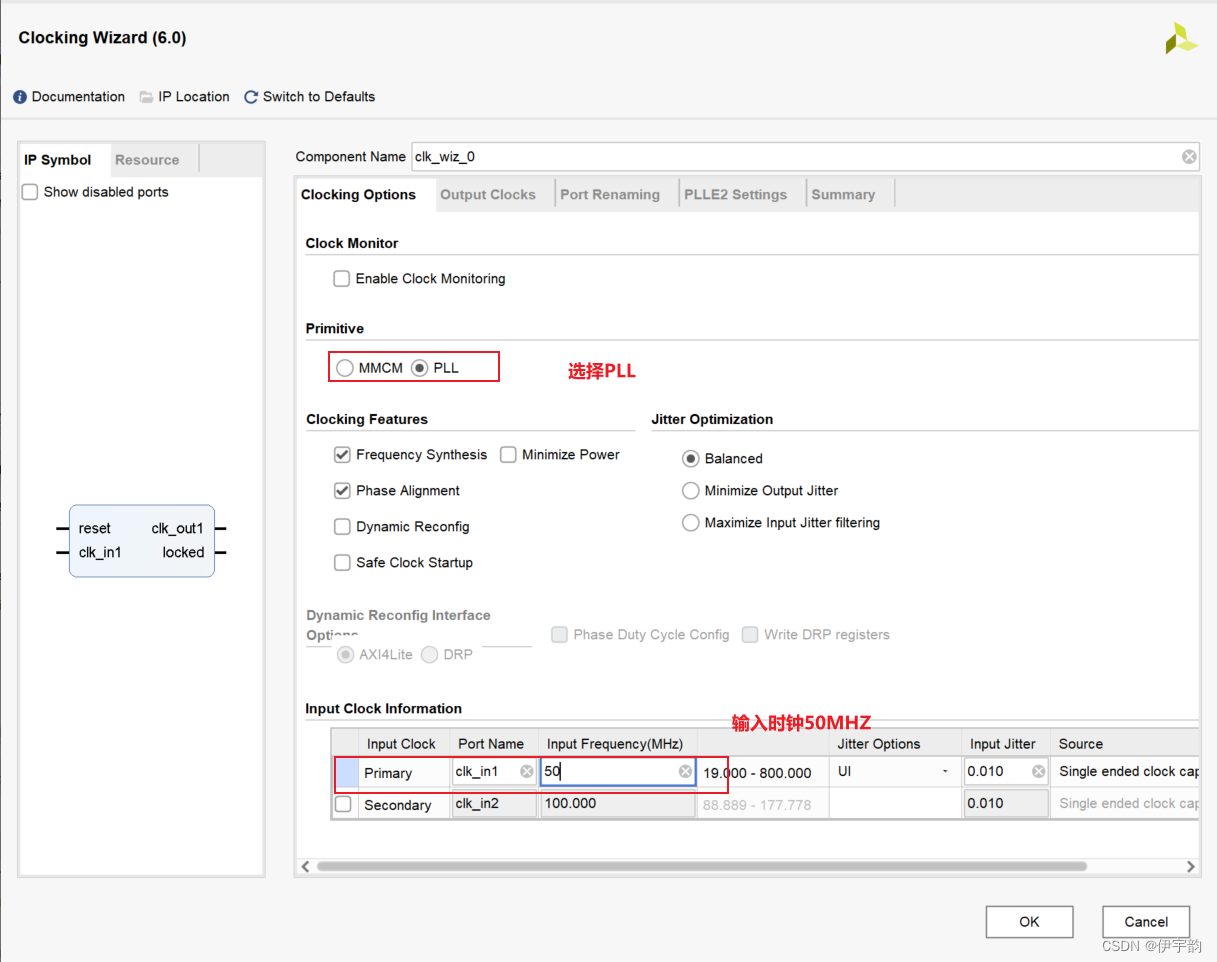

、打开vivado 创建工程

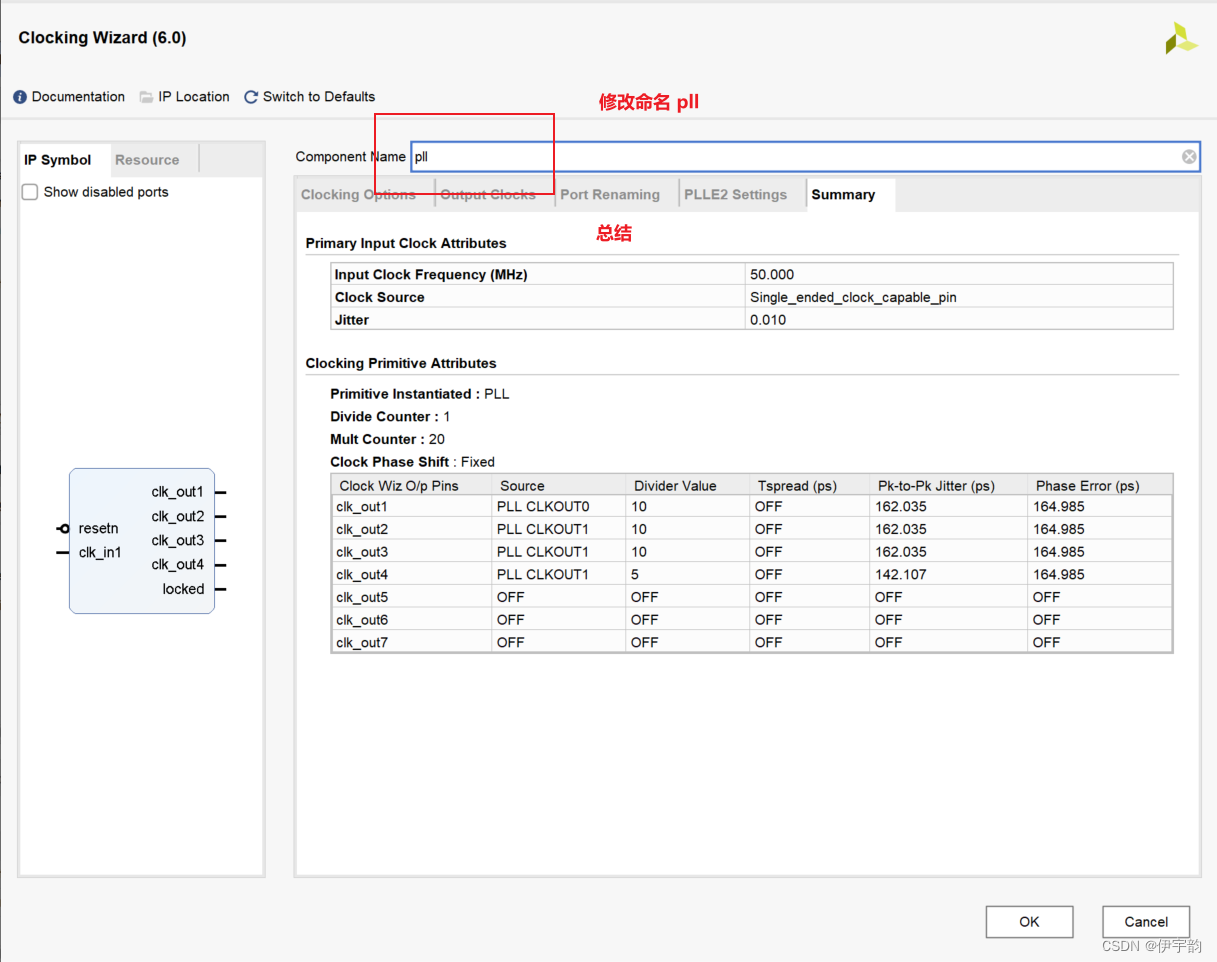

根据例子中的要求配置输出频率

点击ok 配置完成

然后编写测试文件

代码如下

- `timescale 1ns / 1ps

- module pll_tb;

- wire clk100m; // output clk_out1

- wire clk100m_phase; // output clk_out2

- wire clk100m_duty; // output clk_out3

- wire clk200m; // output clk_out4

- // Status and control signals

- reg resetn; // input resetn

- wire locked; // output locked

- // Clock in ports

- reg clk_in1;

- pll instance_name

- (

- // Clock out ports

- .clk_out1(clk100m), // output clk_out1

- .clk_out2(clk100m_phase), // output clk_out2

- .clk_out3(clk100m_duty), // output clk_out3

- .clk_out4(clk200m), // output clk_out4

- // Status and control signals

- .resetn(resetn), // input resetn

- .locked(locked), // output locked

- // Clock in ports

- .clk_in1(clk_in1));

- initial clk_in1 = 1;

- always #10 clk_in1 = ~clk_in1;

- initial begin

- resetn = 1'b0;

- #201;

- resetn = 1'b1;

- #20000;

- $stop;

- end

- endmodule

仿真波形:

可以观察到输出波形与例子中的要求一致。

-

相关阅读:

了解如何使用 Node.js 构建微服务

用C语言将无符号整数转换为字符串

Linux 线程同步、互斥锁、避免死锁、条件变量

js控制图片在可视区域才展示,图片懒加载

ESP32网络开发实例-非接触式水位监测

【消息队列笔记】chp3-如何确保消息不丢失

路由懒加载

Mathtype插入编号的高级格式会重置之前的简单格式的问题

等比例缩放

Java中可以用的大数据推荐算法

- 原文地址:https://blog.csdn.net/weixin_46897065/article/details/136356331