-

RISC-V特权架构 - 中断与异常概述

本文属于《 RISC-V指令集基础系列教程》之一,欢迎查看其它文章。1 中断概述

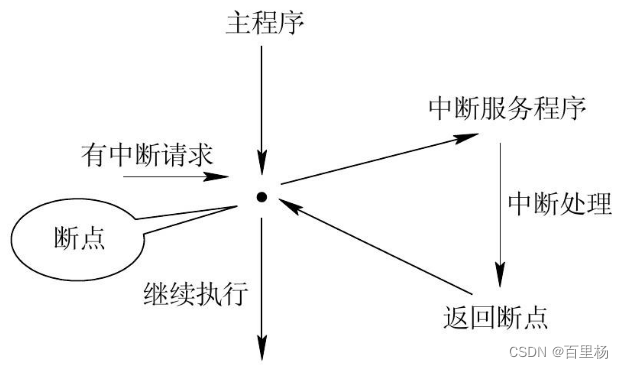

中断(Interrupt)机制,即处理器核在顺序执行程序指令流的过程中,突然被别的请求打断而中止执行当前的程序,转而去处理别的事情,待其处理完了别的事情,然后重新回到之前程序中断的点,继续执行之前的程序指令流,其要点如下。- 打断处理器执行程序指令流的“别的请求”便称之为中断请求(Interrupt Request),“别的请求”的来源便称之为中断源(Interrupt Source)。中断源通常来自于外围硬件设备。

- 处理器转而去处理的“别的事情”便称之为中断服务程序(Interrupt Service Routine,ISR)。

- 中断处理是一种正常的机制,而非一种错误情形。处理器收到中断请求之后,需要保存当前程序的现场,简称为保存现场。等到处理完中断服务程序后,处理器需要恢复之前的现场,从而继续执行之前被打断的程序,简称为“恢复现场”。

- 可能存在多个中断源,同时向处理器发起请求的情形,因此需要对这些中断源进行仲裁,从而选择哪个中断源被优先处理。此种情况称为“中断仲裁”,同时可以给不同的中断分配优先级以便于仲裁,因此中断存在着“中断优先级”的概念。

- 还有一种可能是,处理器已经在处理某个中断过程中(执行该中断的ISR 之中),此时有一个优先级更高的新中断请求到来,此时处理器该如何是好呢?有如下两种可能。

第一种,可能是处理器并不响应新的中断,而是继续执行当前正在处理的中断服务程序,待到彻底完成之后才响应新的中断请求,这种称为处理器“不支持中断嵌套”。

第二种,可能是处理器中止当前的中断服务程序,转而开始响应新的中断,并执行其“中断服务程序”,如此便形成了中断嵌套(即前一个中断还没响应完,又开始响应新的中断),并且嵌套的层次可以有很多层。注意:

假设新来的中断请求的优先级,比正在处理的中断优先级低(或者相同),则不管处理器是否能支持“中断嵌套”,都不应该响应这个新的中断请求,处理器必须完成当前的中断服务程序之后,才考虑响应新的中断请求(因为新中断请求的优先级并不比当前正在处理的中断优先级高)。RISC-V架构默认不支持中断嵌套。

2 异常概述

异常(Exception)机制,即处理器核在顺序执行程序指令流的过程中,突然遇到了异常的事情而中止执行当前的程序,转而去处理该异常,其要点如下。

• 处理器遇到的“异常的事情”称为异常(Exception)。异常与中断的最大区别在于中断往往是一种外因,而异常是由处理器内部事件或程序执行中的事件引起的,譬如本身硬件故障、程序故障,或者执行特殊的系统服务指令而引起的,简而言之是一种内因。

• 与中断服务程序类似,处理器也会进入异常服务处理程序。

• 与中断类似,可能存在多个异常同时发生的情形,因此异常也有优先级,并且也可能发生多重异常的嵌套。3 广义上的异常

如上文所述,中断和异常最大的区别是起因内外有别。除此之外,从本质上来讲,中断和异常对于处理器而言基本上是一个概念。中断和异常发生时, 处理器将暂停当前正在执行的程序,转而执行中断和异常处理程序;返回时,处理器恢复执行之前被暂停的程序。

因此中断和异常的划分是一种狭义的划分。从广义上来讲,中断和异常都被认为是一种广义上的异常。处理器广义上的异常,通常只分为同步异常(Synchronous Exception)和异步异常(Asynchronous Exception)。

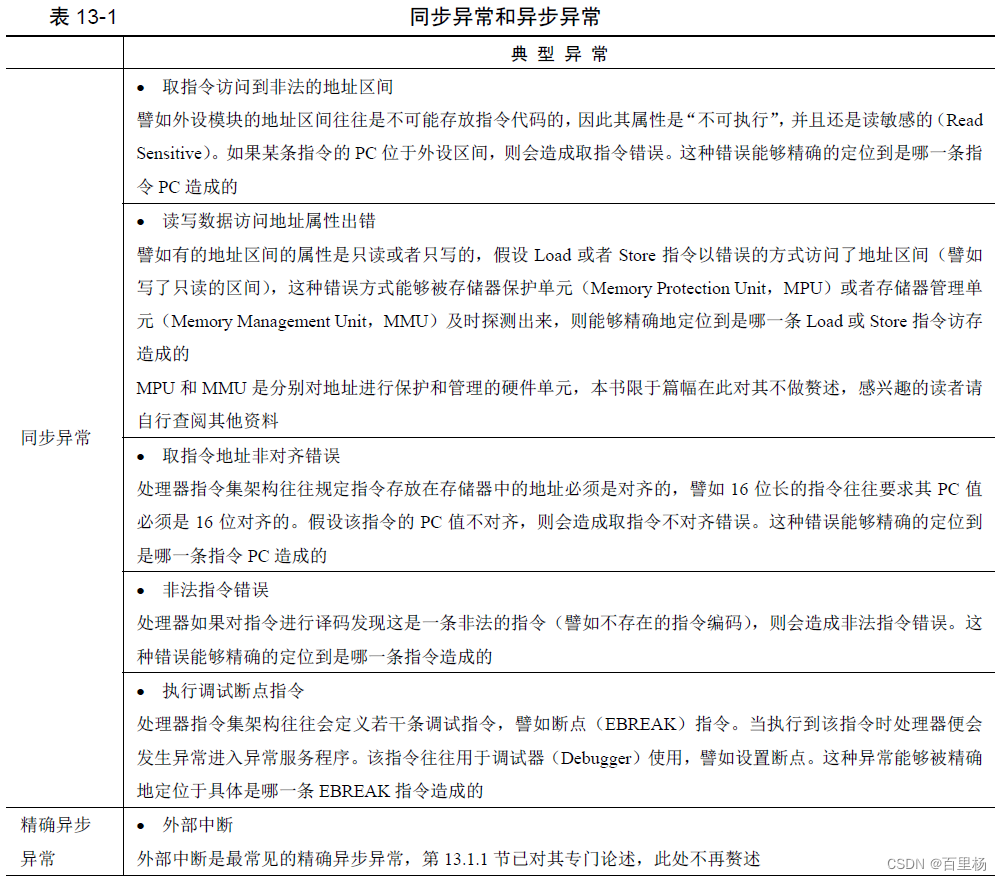

3.1 同步异常

同步异常,是指由于执行程序指令流或者试图执行程序指令流而造成的异常。这种异常的原因,能够被精确定位于某一条执行的指令。同步异常的另外一个通俗的表象便是,无论程序在同样的环境下执行多少遍,每一次都能精确地重现出来。

譬如,程序流中有一条非法的指令,那么处理器执行到该非法指令便会产生非法指令异常(Illegal Instruction Exception),能被精确地定位于这一条非法指令,并且能够被反复重现。

3.2 异步异常

异步异常,是指那些产生原因不能够被精确定位于某条指令的异常。异步异常的另外一个通俗的表象便是,程序在同样的环境下执行很多遍,每一次发生异常的指令PC 都可能会不一样。

最常见的异步异常是“外部中断”。比如,外部中断的发生,是由外围设备驱动的,一方面外部中断的发生带有偶然性,另一方面中断请求抵达于处理器核之时,处理器的程序指令流执行到具体的哪一条指令更带有偶然性。因此一次中断的到来,可能会巧遇到某一条“正在执行的不幸指令”,而该指令便成了“背锅侠”。在它的指令PC 所在之处,程序便停止执行,并转而响应中断去执行中断服务程序。但是当程序重复执行时,却很难会出现同一条指令反复“背锅”的精确情形。

对于异步异常,根据其响应异常后的处理器状态,又可以分为两种:

(1)精确异步异常(Precise Asynchronous Exception):指响应异常后的处理器状态,能够精确反映为某一条指令的边界,即某一条指令执行完之后的处理器状态。

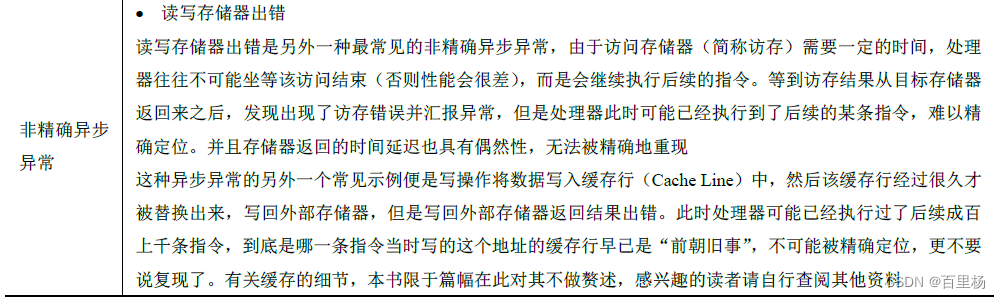

(2)非精确异步异常(Imprecise Asynchronous Exception):指响应异常后的处理器状态,无法精确反映为某一条指令的边界,即可能是某一条指令执行了一半然后被打断的结果,或者是其他模糊的状态。3.3 常见同步异常和异步异常

常见的典型同步异常和异步异常,如下表所示,此表可以帮助读者更加理解同步异常和异步异常的区别。

参考文档:

- 《手把手教你设计CPU.RISC-V处理器》

-

相关阅读:

IT66021FN: Single-port HDMI 1.4 Receiver with 3D Support

Android 扫码枪输入时屏蔽软键盘和顶部状态栏

轻量封装WebGPU渲染系统示例<36>- 广告板(Billboard)(WGSL源码)

【一起学Rust | 进阶篇 | Grid库】二维表数据结构——Grid

运动App如何实现端侧后台保活,让运动记录更完整?

山东菏泽家乡网页代码 html静态网页设计制作 dw静态网页成品模板素材网页 web前端网页设计与制作 div静态网页设计

突破编程_C++_设计模式(观察者模式)

NISP网络安全中渗透测试的流程是什么

家电软装记录

痛快SpringBoot终于禁掉了循环依赖

- 原文地址:https://blog.csdn.net/u011832525/article/details/136380030