-

csapp 第四章 读书笔记 part1

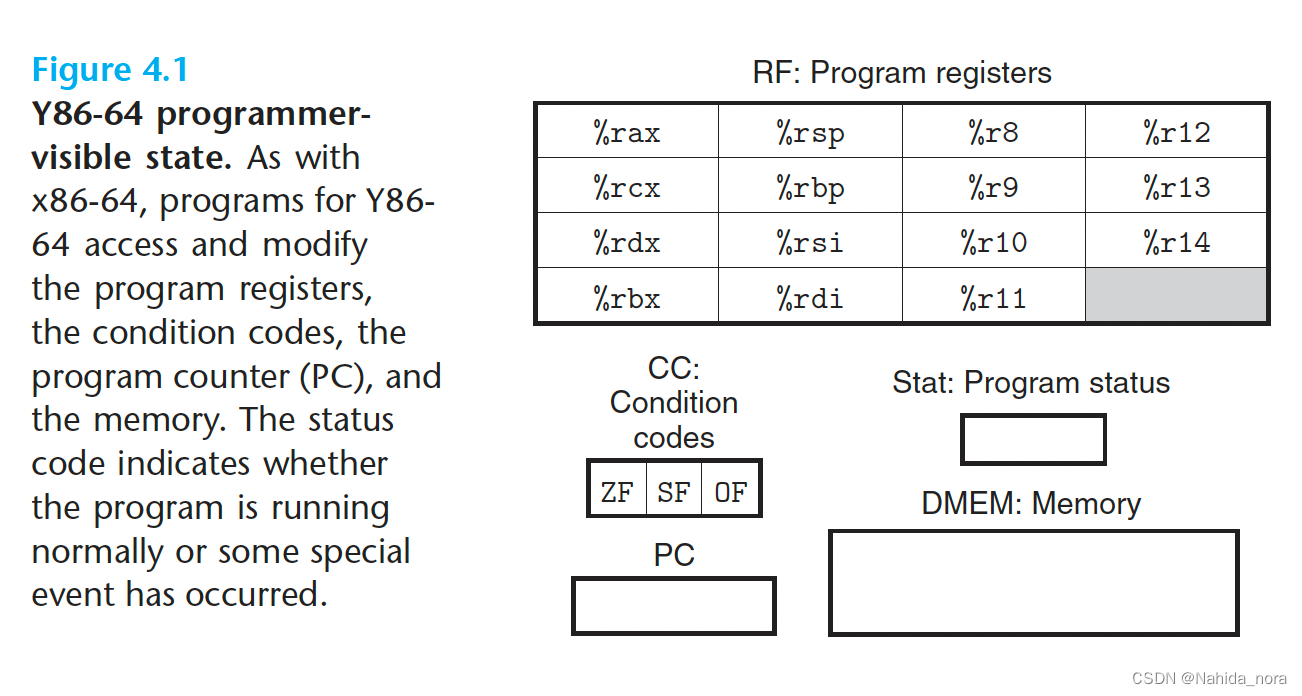

Programmer-Visible State

Y86-64 是一个教学用的指令集架构,用于教授计算机体系结构和汇编语言的课程。它是为了简化教学和理解而设计的,因此它的指令集和功能相对较少。而 x86-64 是一种常见的处理器架构,用于商业计算机系统和服务器。它是由英特尔和AMD等公司开发的,具有复杂的指令集和丰富的功能,可以执行各种复杂的任务和应用程序。

因此,Y86-64 和 x86-64 的主要区别在于它们的设计目的和使用范围。Y86-64 用于教学和学术研究,而 x86-64 用于商业和实际的计算机系统。

Y86-64 指令

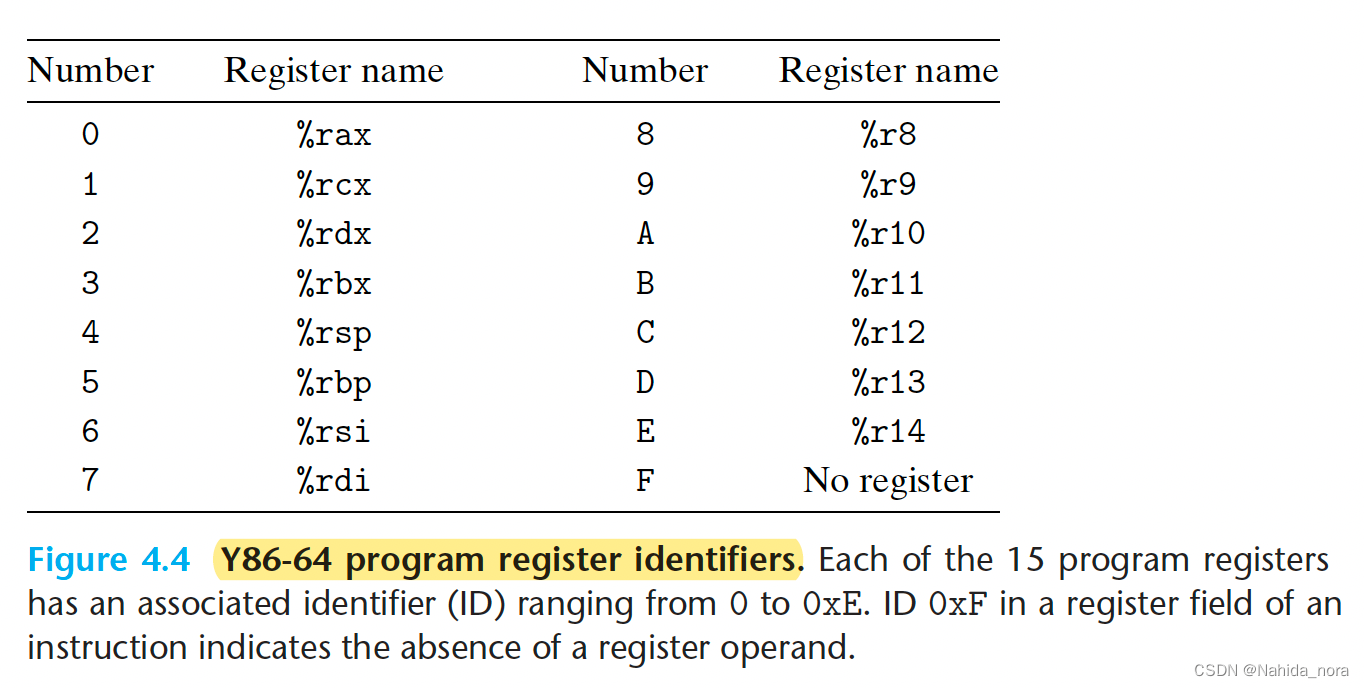

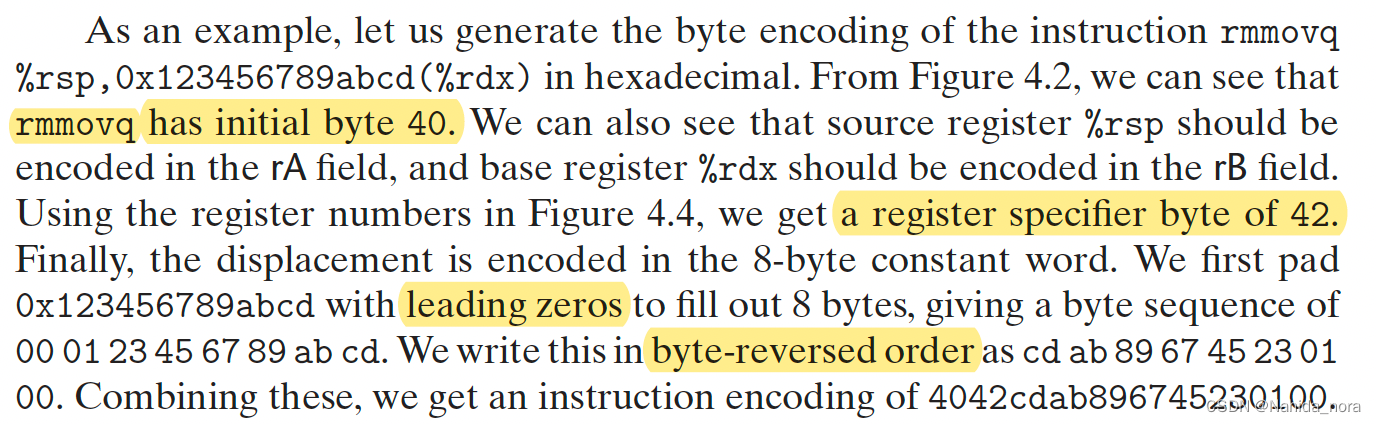

Instruction Encoding

Y86-64指令确保每个指令的编码是唯一的,通过initial byte 是不会重复的。RISC(精简指令集计算机)和 CISC(复杂指令集计算机)是两种不同的计算机处理器架构。它们在指令集和执行方式上有一些显著的区别。

RISC 指令集架构的特点包括:

- 简单的指令集:RISC 处理器的指令集通常非常简单,每条指令的执行时间都是相对较短的。

- 采用固定长度的指令格式:RISC 指令通常采用固定长度的格式,这样可以简化指令的解码和执行过程。

- 硬件优化:RISC 处理器的设计更注重硬件优化,通过更多的寄存器和流水线技术来提高指令执行的效率。

CISC 指令集架构的特点包括:

- 复杂的指令集:CISC 处理器的指令集比较复杂,一条指令可以执行多个操作,这样可以减少对内存的访问次数。

- 变长指令格式:CISC 指令通常采用变长的格式,这样可以容纳更多的功能和灵活性。

- 软件优化:CISC 处理器的设计更注重软件优化,通过复杂的指令来减少对内存的访问次数,从而提高性能。

总的来说,RISC 和 CISC 的主要区别在于指令集的复杂度和执行方式。RISC 更注重简化指令集和硬件优化,而 CISC 更注重复杂指令和软件优化。随着技术的发展,RISC 和 CISC 的差异在一定程度上已经变得模糊,因为现代处理器往往采用了混合的设计思想。

Y86-64指令集包含了CISC和RISC指令集的特征。在CISC方面,它具有条件码和可变长度指令,并且使用堆栈来存储返回地址。在RISC方面,它采用了加载/存储体系结构和常规指令编码,并且通过寄存器传递过程参数。可以将其视为采用CISC指令集(x86),并通过应用RISC原则来简化它。

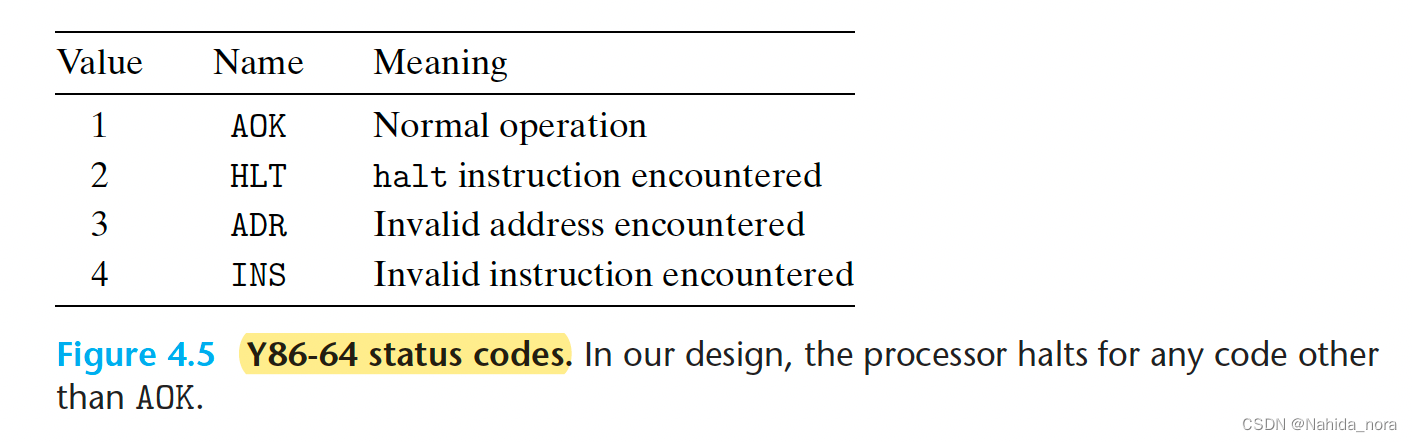

Y86-64 Exceptions

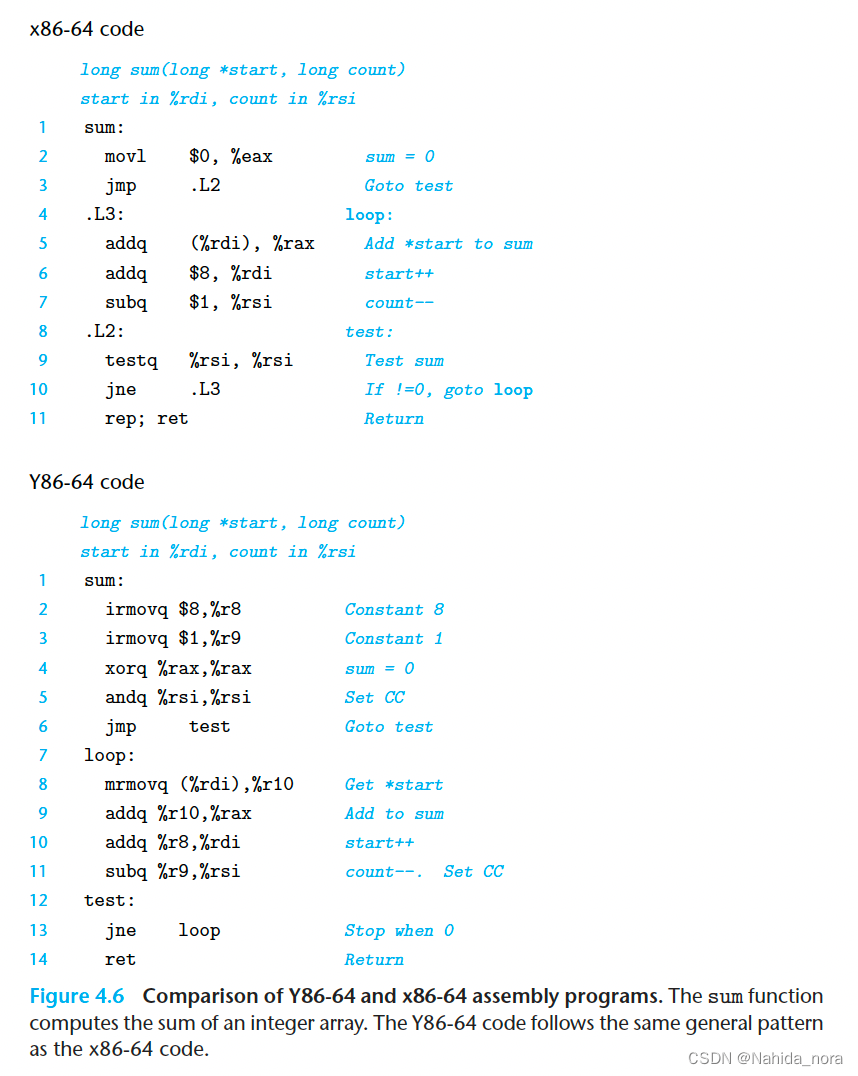

描述程序的状态。Y86-64 Programs

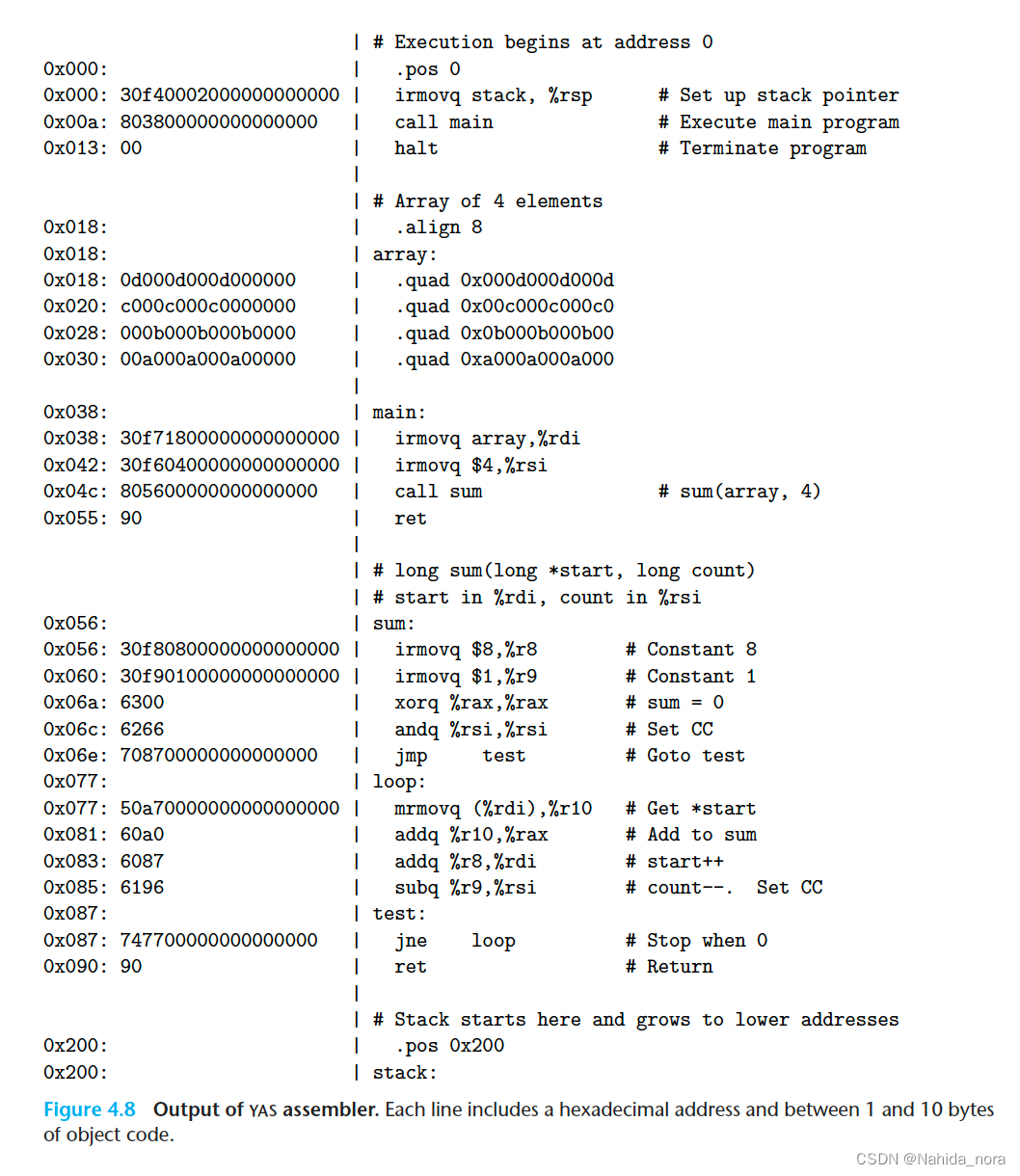

在这个程序中,以’.'开头的单词是汇编指令,告诉汇编器调整它生成代码的地址或插入一些数据。指令.pos 0(第2行)表示汇编器应该从地址0开始生成代码。这是所有Y86-64程序的起始地址。下一条指令(第3行)初始化了堆栈指针。我们可以看到标签stack声明在程序末尾(第40行),使用.pos指令(第39行)指示地址0x200。因此,我们的堆栈将从这个地址开始,并向较低的地址增长。我们必须确保堆栈不会增长得太大,以至于覆盖代码或其他程序数据。

图4.8显示了通过我们称为yas的汇编器汇编图4.7中显示的代码的结果。汇编器输出采用ASCII格式,以使其更易读。在包含指令或数据的汇编文件的行上,目标代码包含一个地址,后面跟着1到10个字节的值。

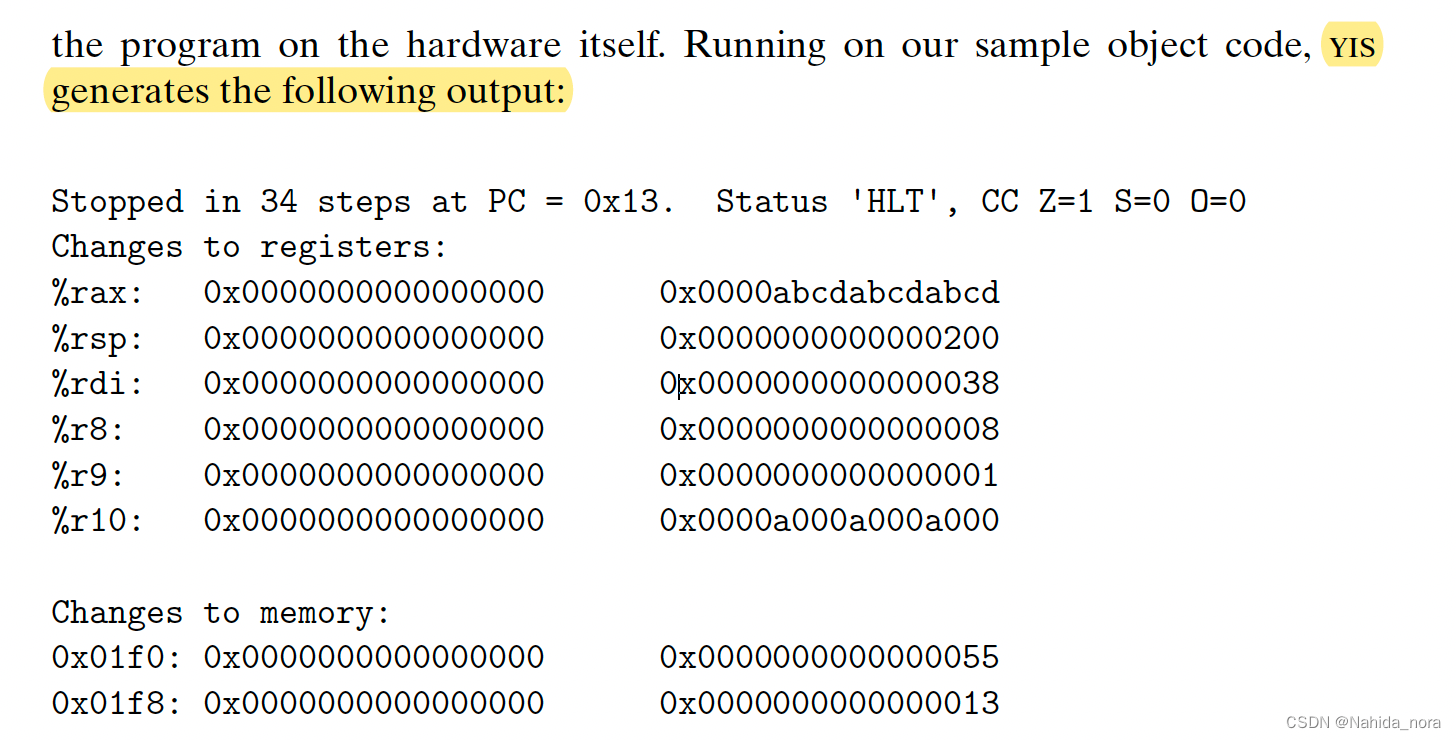

实现了一个称为yis的指令集模拟器,其目的是模拟执行Y86-64机器码程序,而不是试图模拟任何特定处理器实现的行为。

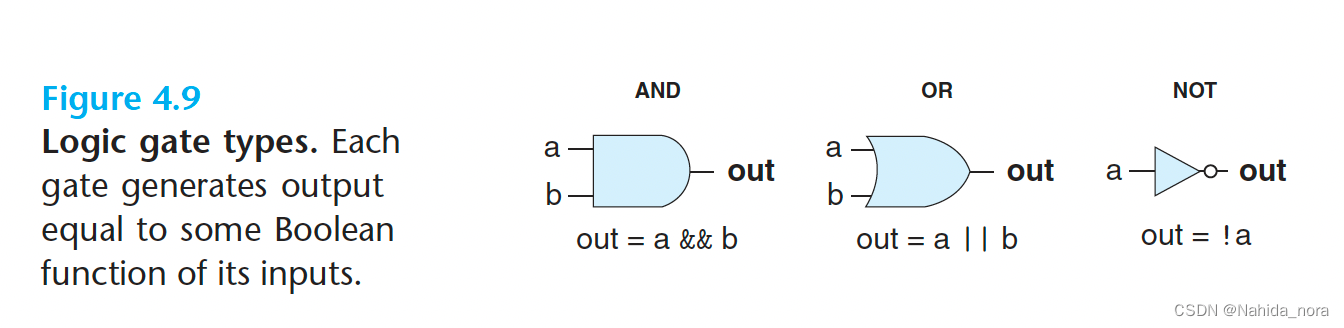

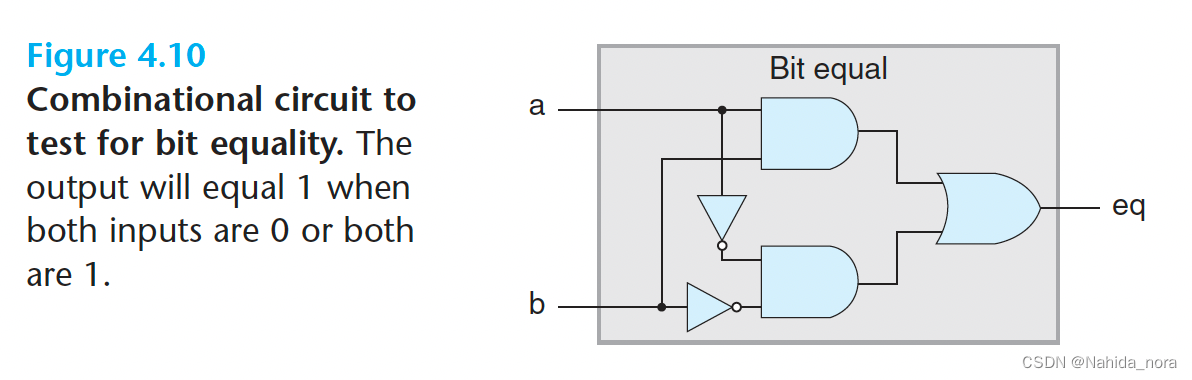

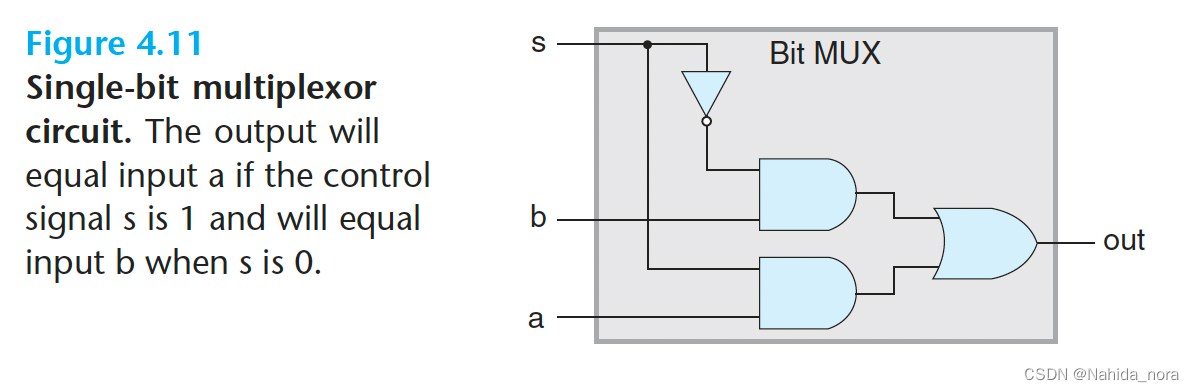

Logic Design and the Hardware Control Language HCL

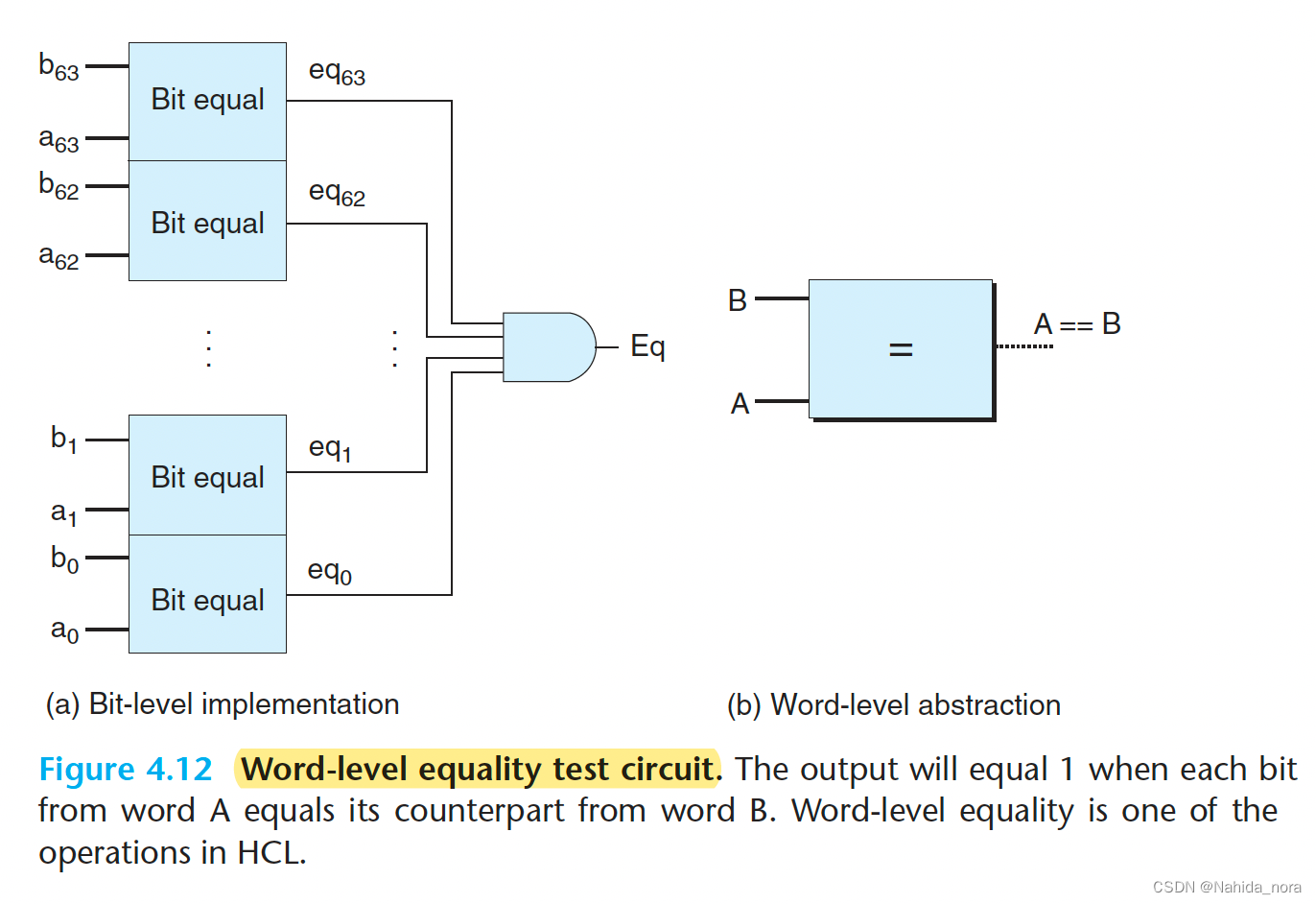

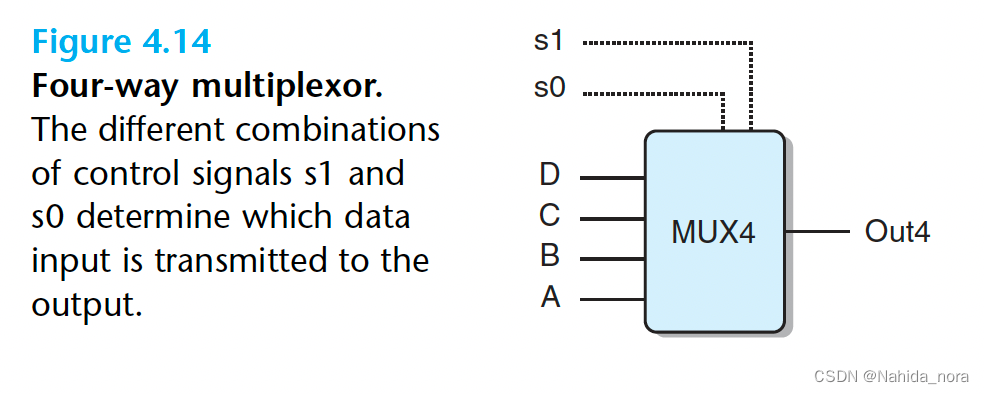

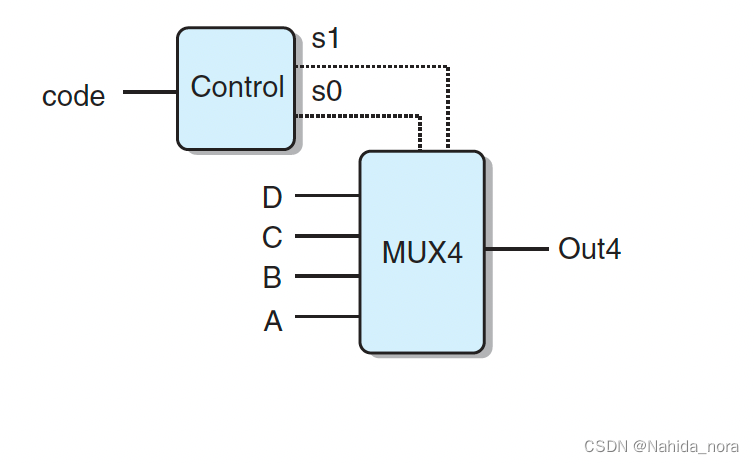

Word-Level Combinational Circuits and HCL Integer Expressions

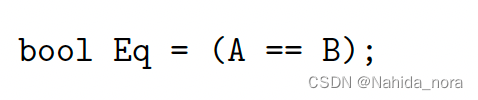

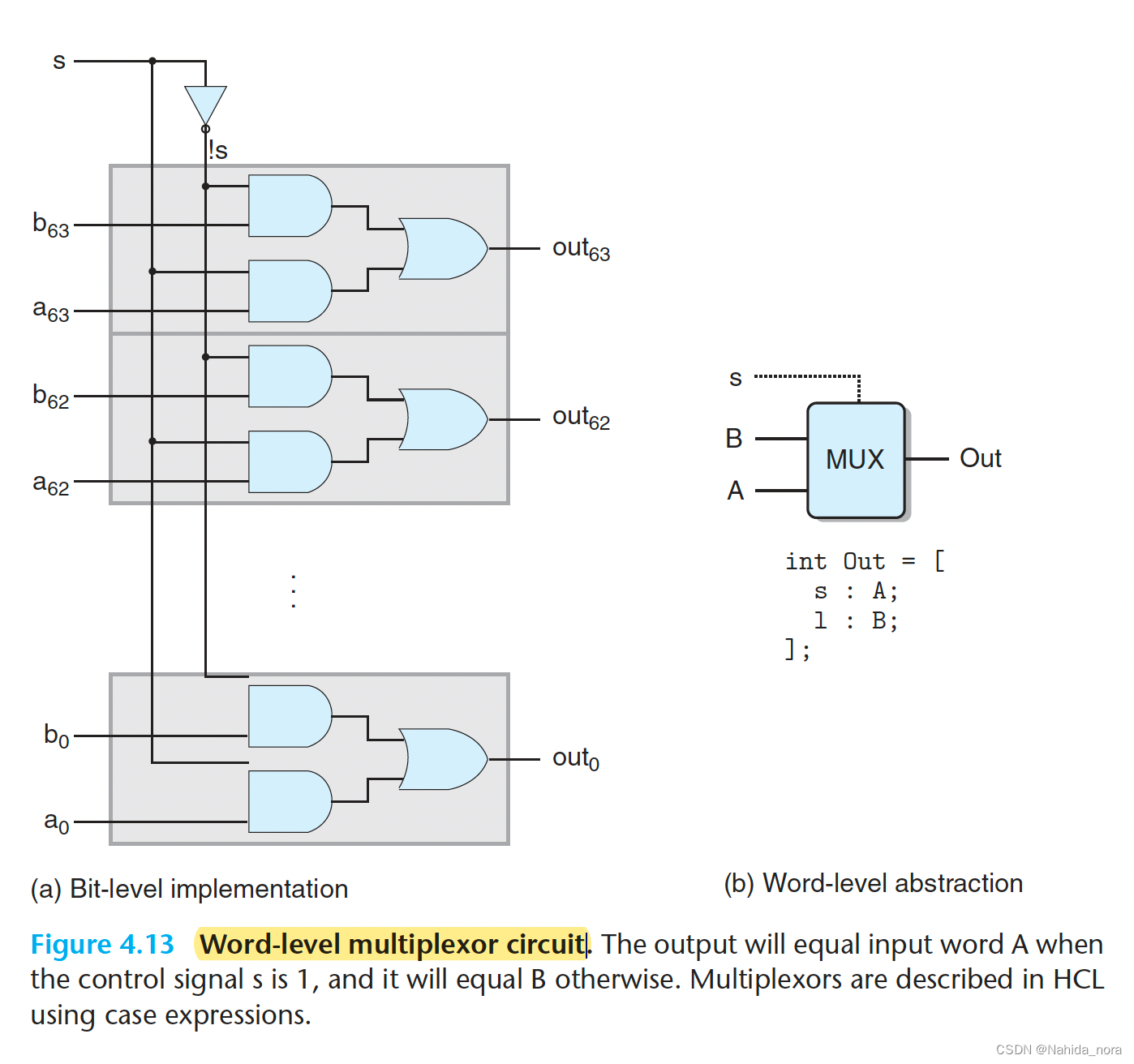

HCL 的 case expressions

Set Membership

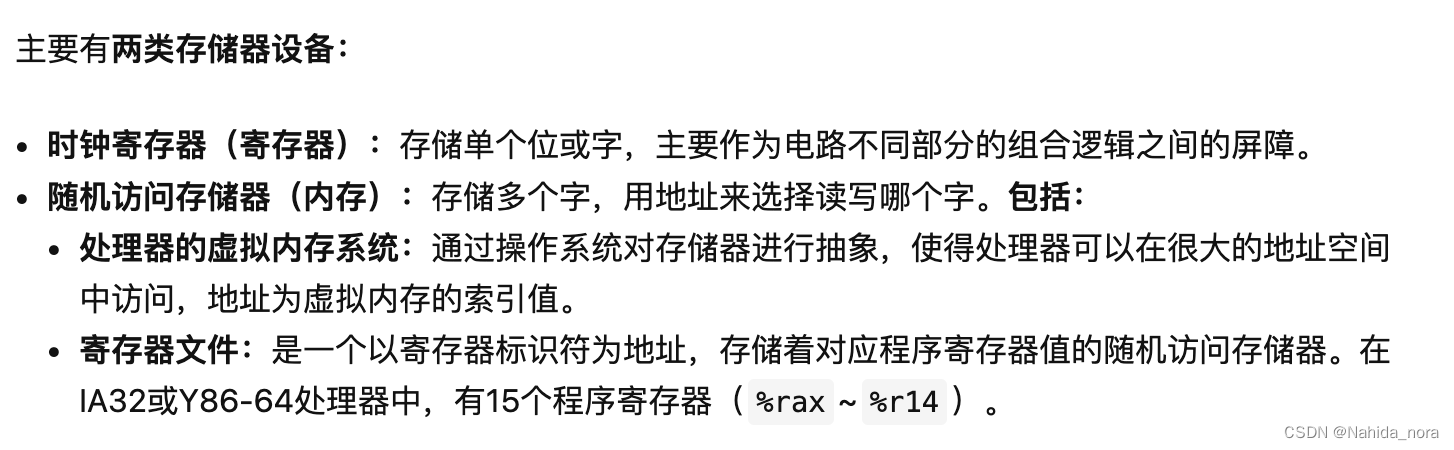

Memory and Clocking

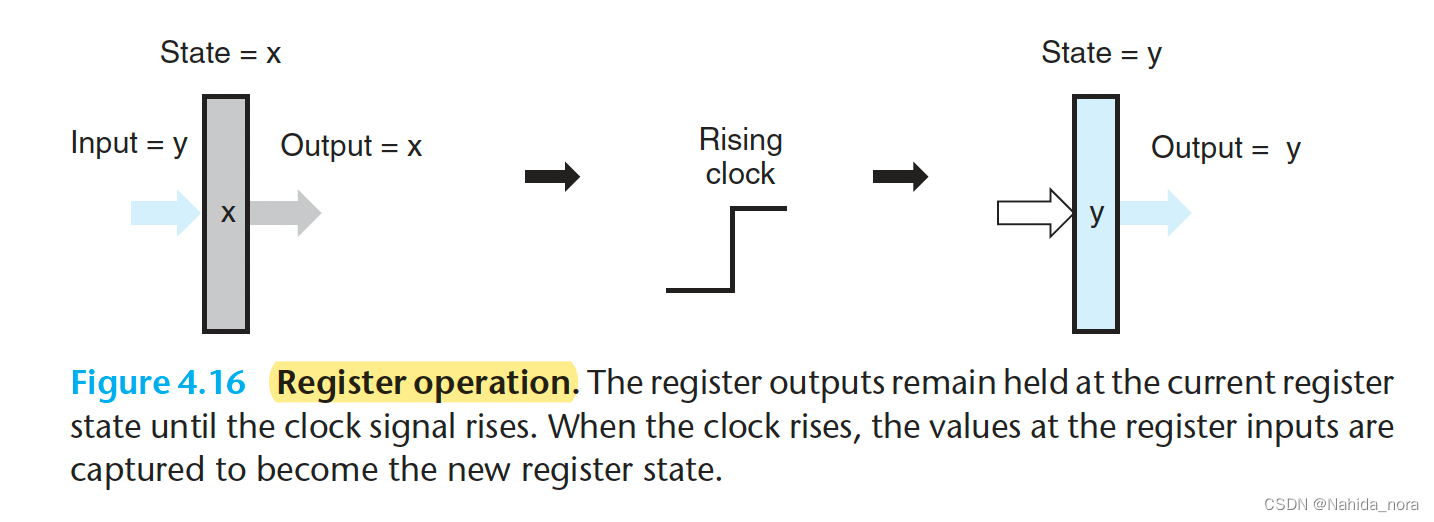

hardware registers

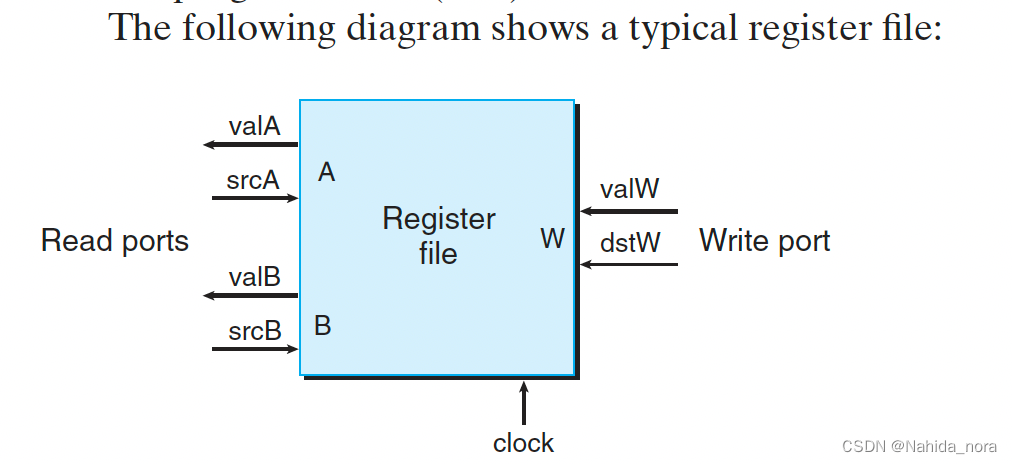

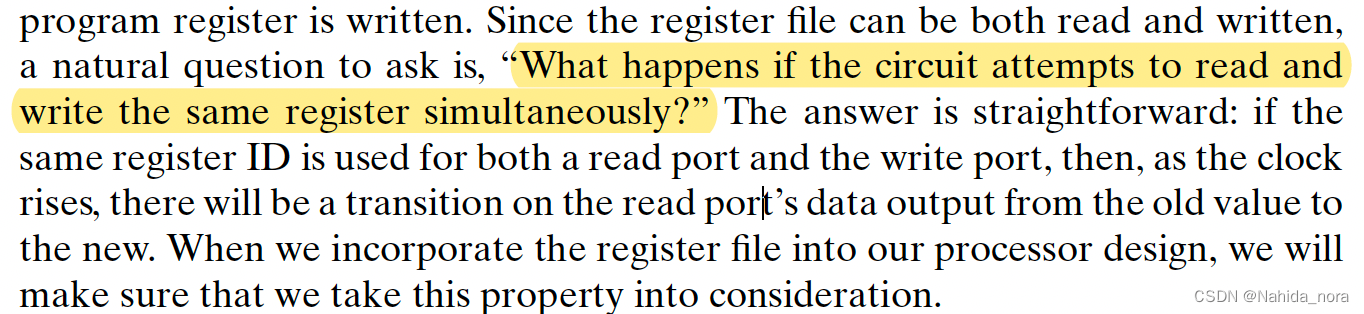

由于寄存器文件既可以读取又可以写入,一个自然的问题是:“如果电路尝试同时读取和写入同一个寄存器会发生什么?”答案很简单:如果相同的寄存器ID同时用于读取端口和写入端口,那么随着时钟上升,读取端口的数据输出将从旧值过渡到新值。当我们将寄存器文件纳入我们的处理器设计时,我们将确保考虑到这个特性。

Sequential Y86-64 Implementations

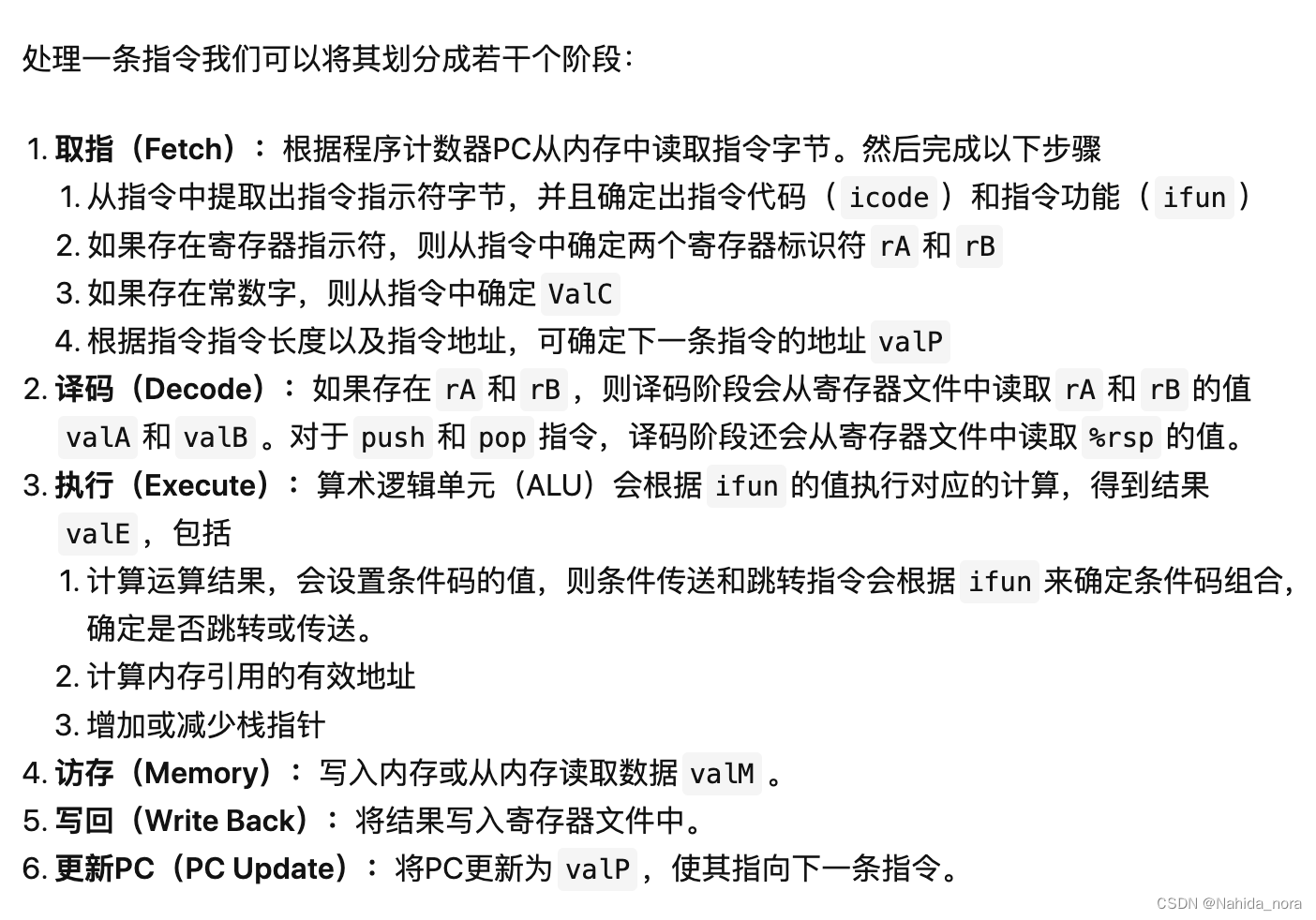

Organizing Processing into Stages

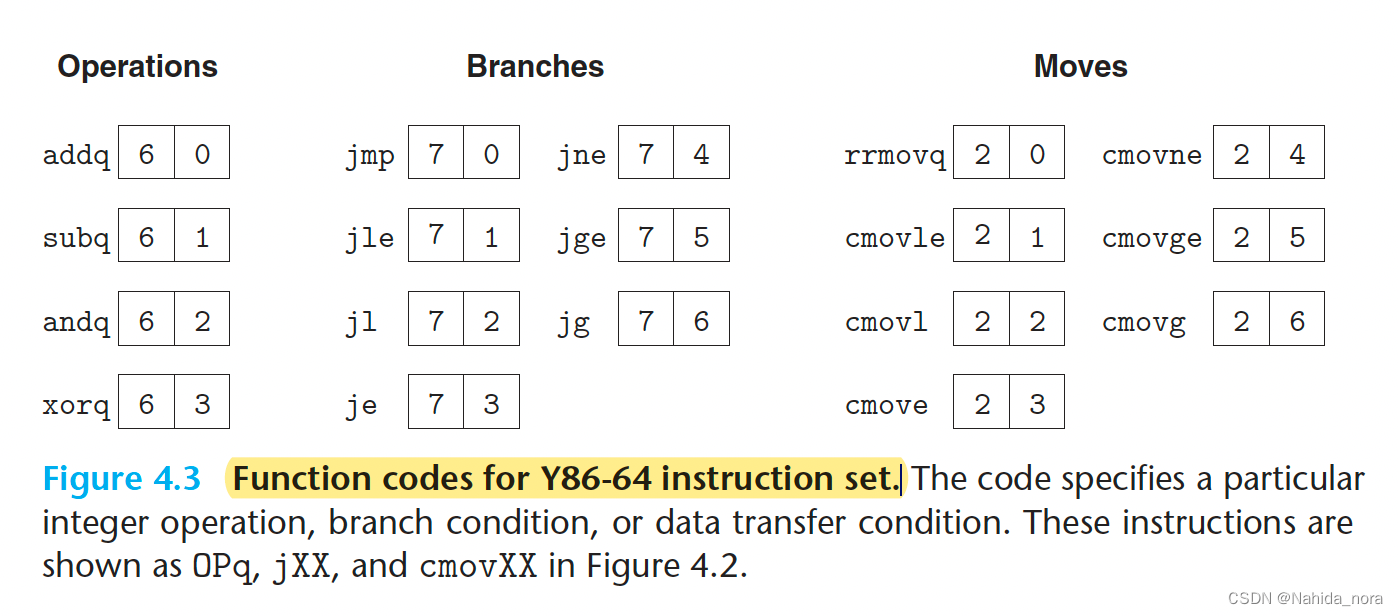

icode和ifun是与指令编码相关的两个字段。

-

icode: icode是指令编码字段,用于指示指令的类型。在处理器中,每个指令都有一个特定的编码,用于唯一标识该指令的类型。通过解码指令的icode字段,处理器可以确定要执行的操作类型,例如整数运算、逻辑运算、数据传输等。

-

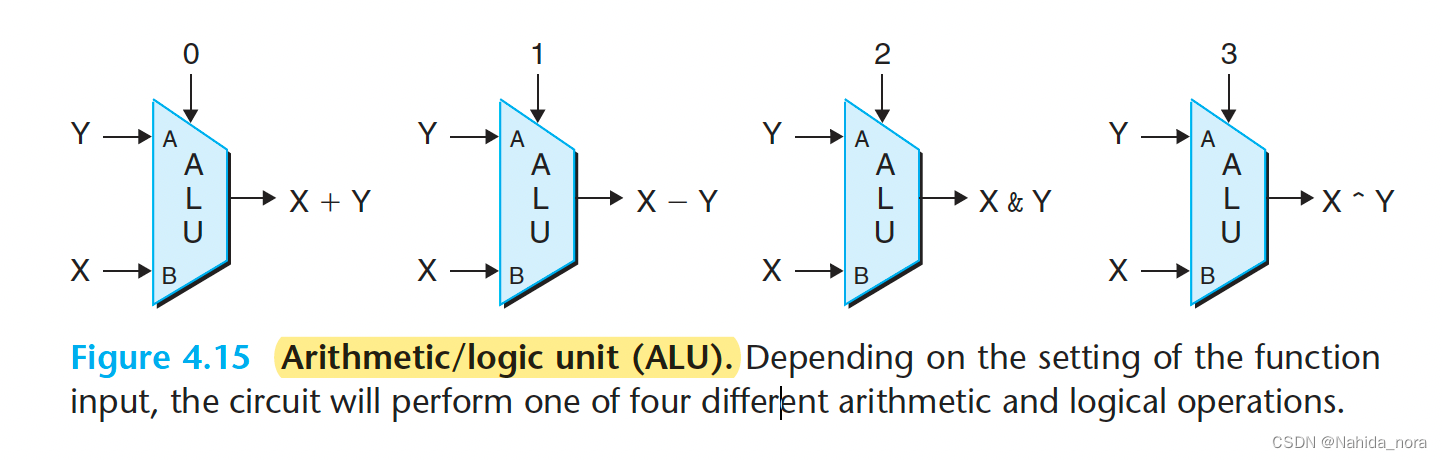

ifun: ifun是指令功能字段,用于指示指令的具体功能或操作。在处理器中,同一类型的指令可能有不同的具体操作,例如加法、减法、逻辑与、逻辑或等。通过解码指令的ifun字段,处理器可以确定要执行的具体操作,以便正确配置ALU或其他执行单元来执行指令所需的计算或操作。

这两个字段一起帮助处理器正确解析和执行指令,确保每条指令都能够按照其编码和功能进行正确的操作。

对于指令addq, subq, andq, 和 xorq:

它们的icode都是相同的,都是"OPq",表示整数和逻辑操作。

而它们的ifun分别对应不同的具体操作:

- addq的ifun是"0x0",表示加法操作。

- subq的ifun是"0x1",表示减法操作。

- andq的ifun是"0x2",表示与操作。

- xorq的ifun是"0x3",表示异或操作。

通过解析这些字段,处理器可以确定要执行的具体操作类型,以便正确配置ALU或其他执行单元来执行指令所需的计算或操作。

"the long instruction format"是指x86汇编语言中的一种指令格式,用于表示复杂的指令。在x86汇编语言中,指令可以采用不同的格式,其中长指令格式通常用于复杂的指令,包括多个操作数或需要更多的操作数前缀。

长指令格式通常由以下几个部分组成:

- 操作码(Opcode):指示要执行的操作类型,例如加法、减法、逻辑运算等。

- ModR/M字节:用于指定操作数的寻址方式和寄存器的选择。

- SIB字节(Scale Index Base):用于指定复杂的内存寻址方式,通常用于数组和结构体的访问。

- Displacement:用于指定内存地址的偏移量。

- 立即数(Immediate):用于指定指令的常数操作数。

长指令格式通常用于复杂的操作,例如对内存的操作、复杂的逻辑运算、条件分支等。它提供了更多的灵活性和功能,但也使得指令的编码和解析更加复杂。因此,长指令格式通常用于需要更多操作数或更复杂操作的情况下。

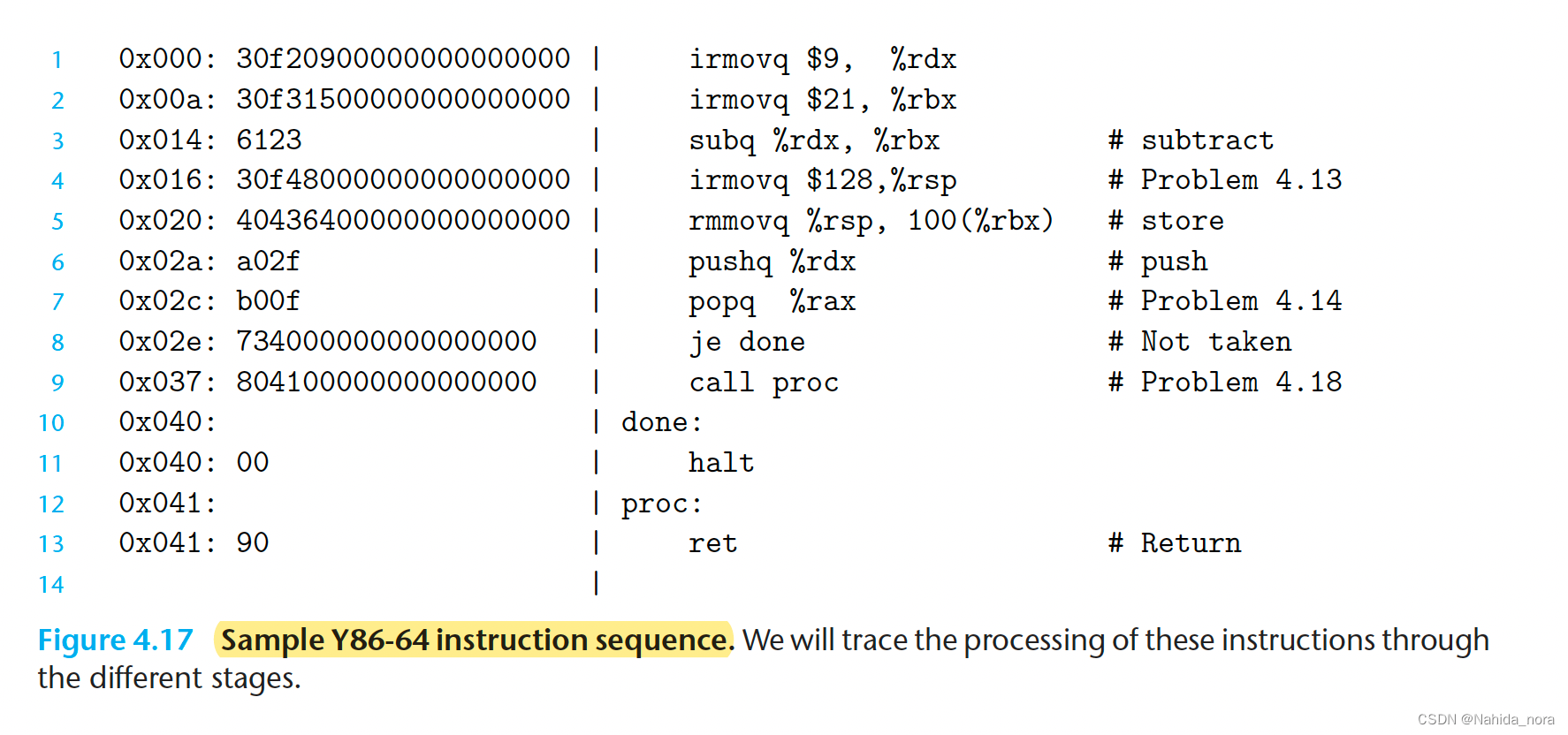

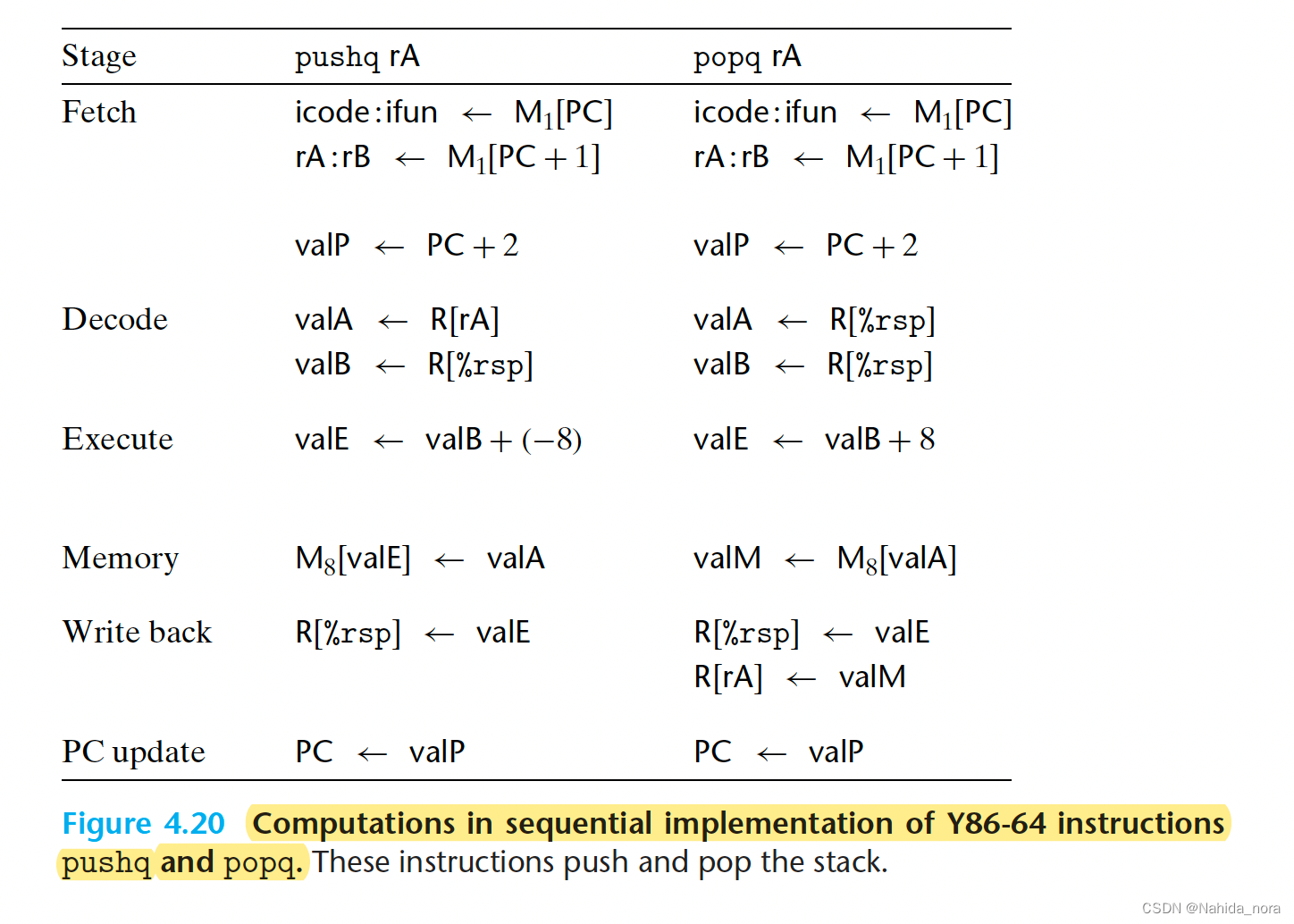

valM 对应的是%rsp 地址指向的虚拟地址的内容。

the instruction is located at address 0x02a and consists of 2 bytes having values 0xa0 and 0x2f.

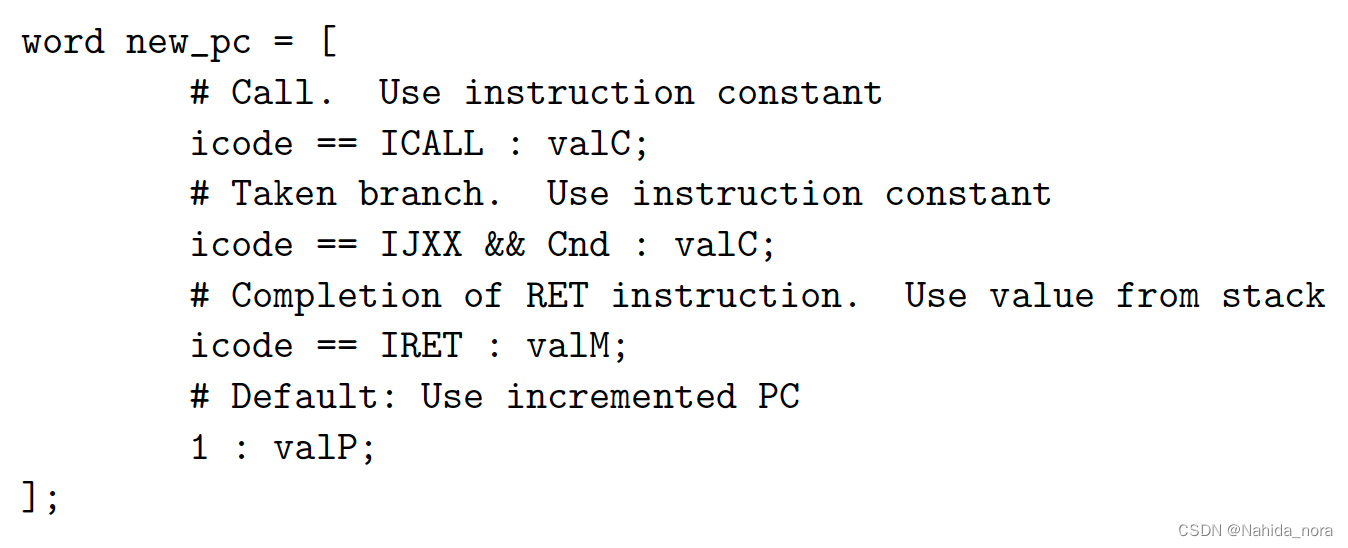

使用call指令时,我们会将valP(call指令后面的指令的地址)压入栈中。在PC更新阶段,我们将PC设置为valC(call的目的地址)。使用ret指令时,在PC更新阶段,我们将从栈中弹出的值valM赋给PC。

ret 之前 rsp 存储内存地址120, ret 之后 rsp存储内存地址128。栈帧的存储在内存中。

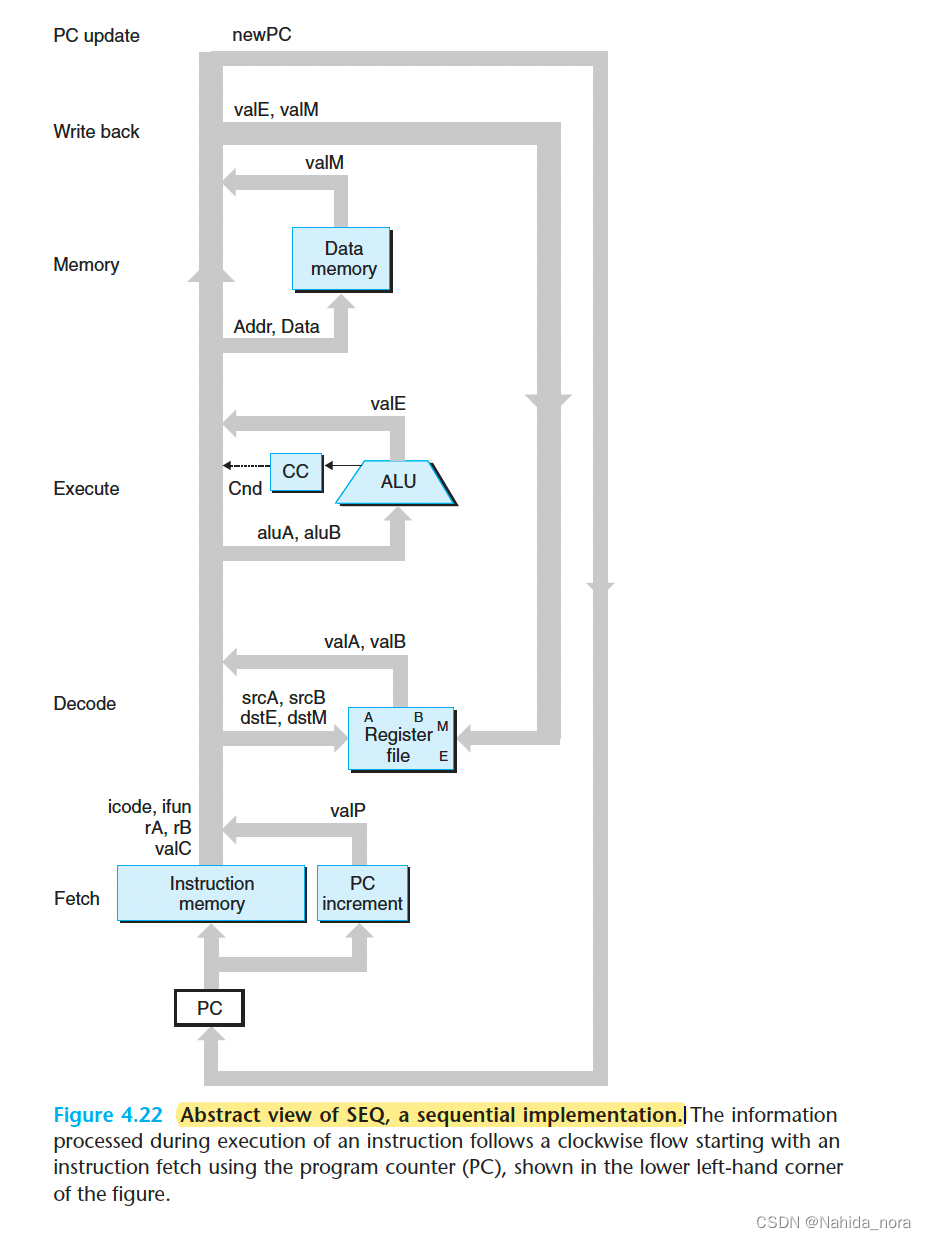

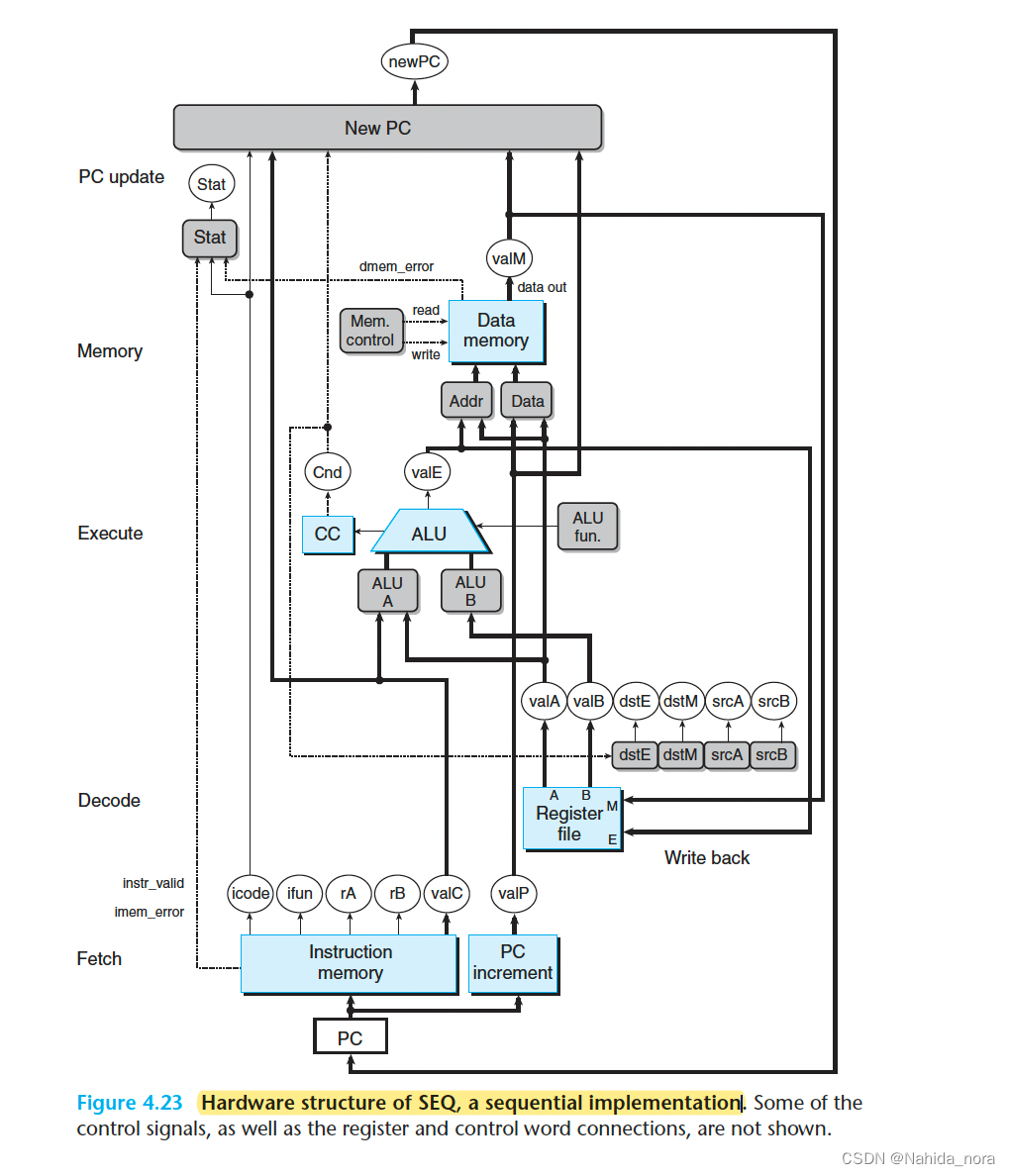

SEQ Hardware Structure

实线表示字级信号(8 字节和 4 字节),虚线表示布尔信号

SEQ Timing

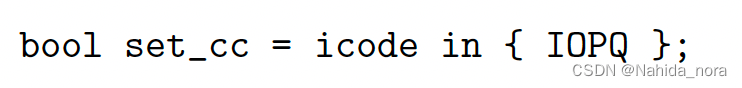

一些指令(整数操作)设置条件码,而另一些指令(条件移动和跳转指令)读取这些条件码,但没有指令必须既设置又读取条件码。即使条件码直到时钟上升开始下一个时钟周期才被设置,条件码将在任何指令尝试读取它们之前更新。

每当时钟从低电平转换到高电平时,处理器就开始执行新的指令。

SEQ Stage Implementations

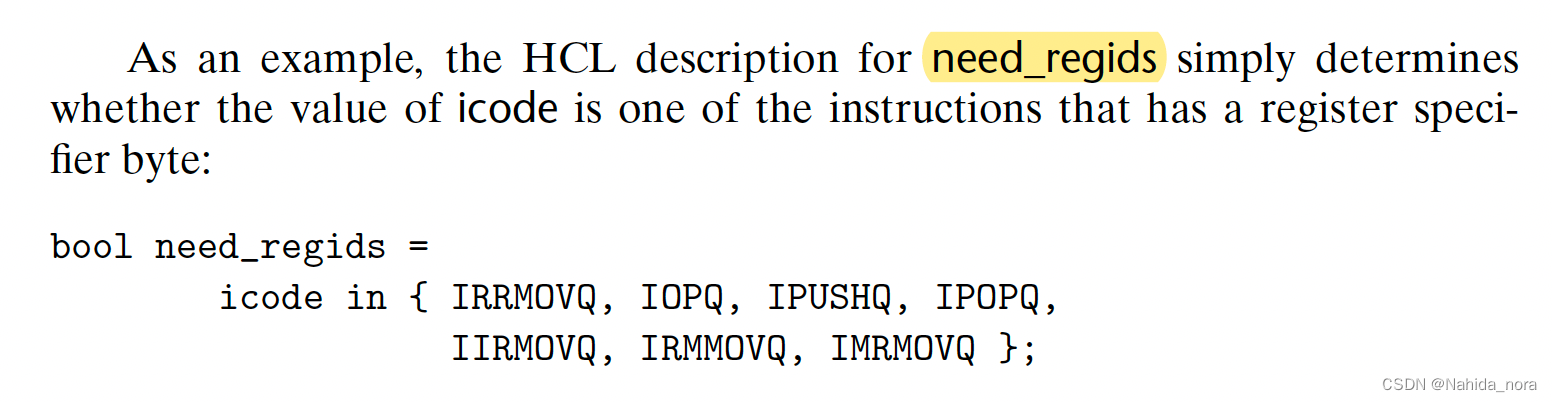

fetch stage

the remaining 9 bytes read from the instruction memory encode some combination of the register specifier byte and the constant word.

the signals rA and rB either encode registers we want to access or indicate that register access is not required.

The unit labeled “Align” also generates the constant word valC.

The PC incrementer hardware unit generates the signal valP, based on the current value of the PC, and the two signals need_regids and need_valC. For PC value p, need_regids value r, and need_valC value i, the incrementer generates the value p + 1+ r + 8i.

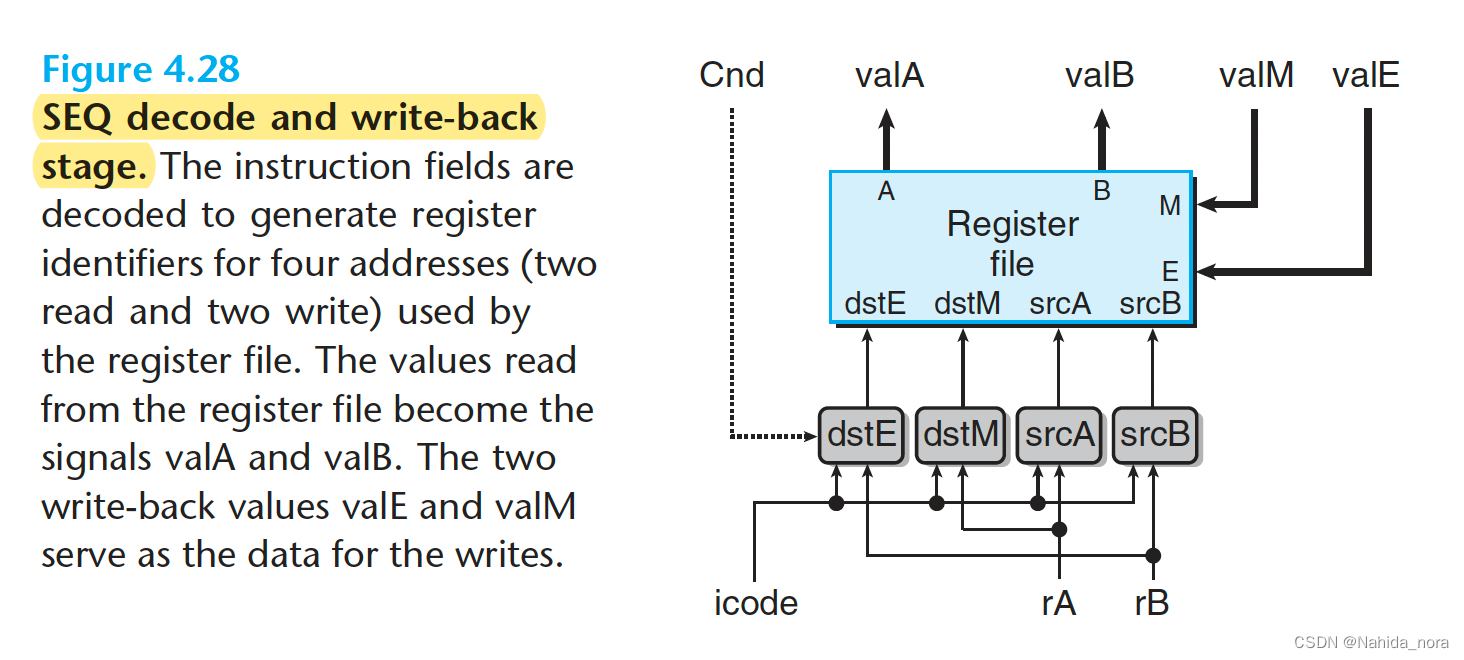

Decode and Write-Back Stages

The register file has four ports. It supports up to two simultaneous reads (on ports A and B) and two simultaneous writes (on ports E and M).

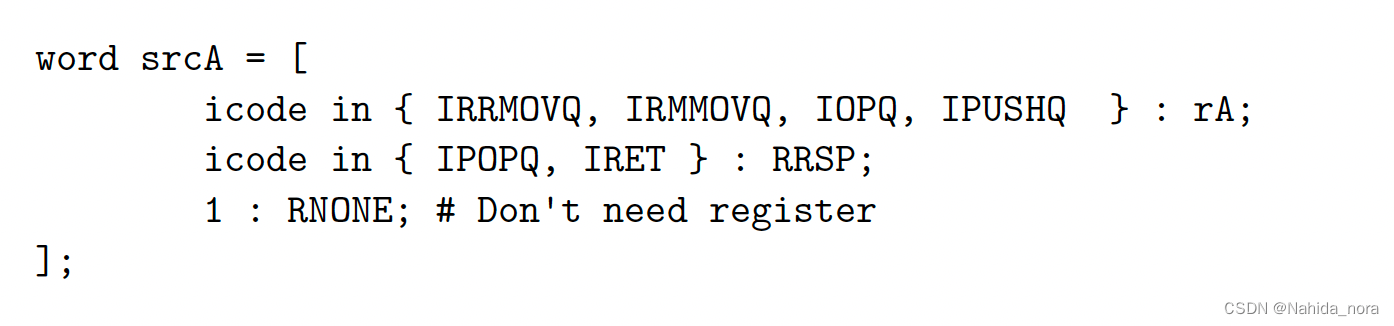

Each port has both an address connection and a data connection, where the address connection is a register ID, and the data connection is a set of 64 wires serving as either an output word (for a read port) or an input word (for a write port) of the register file.HCL描述srcA (decode stage):

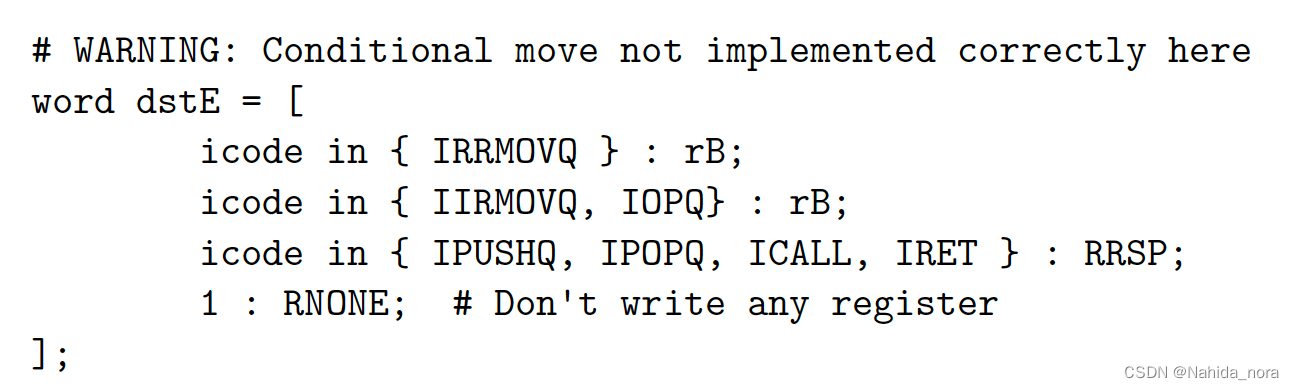

HCL描述dstE (write-back stage):

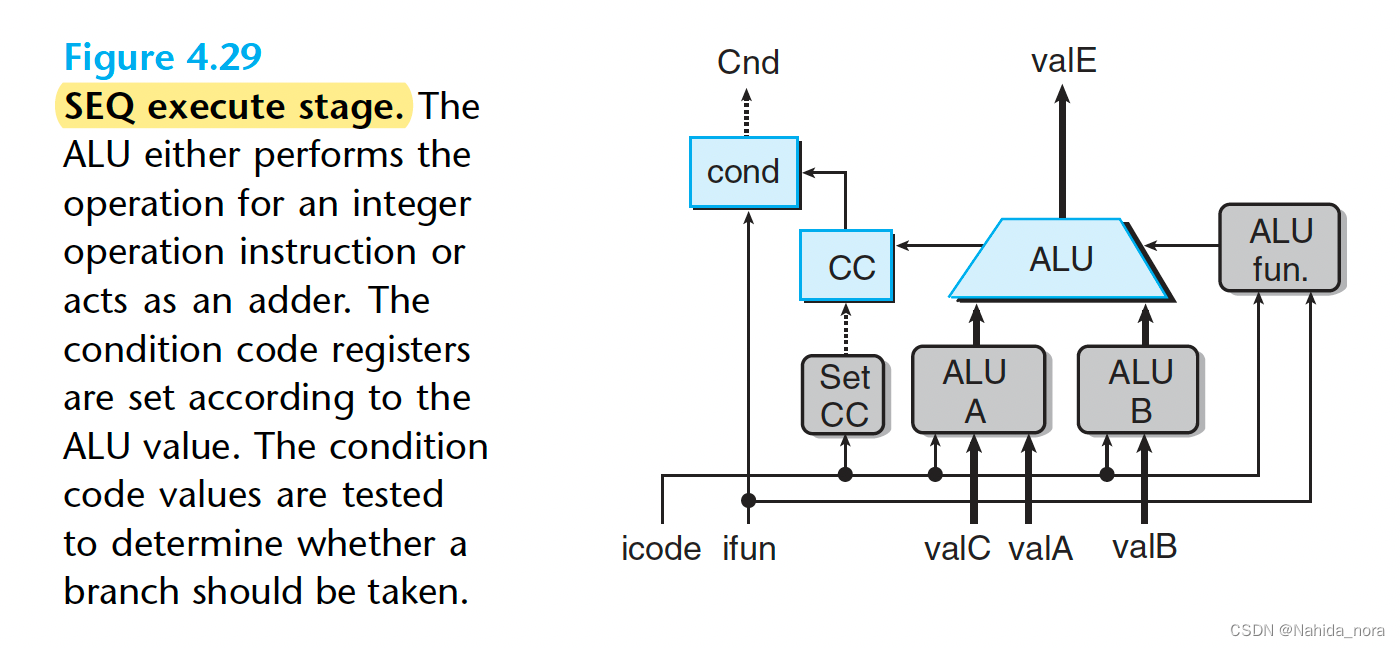

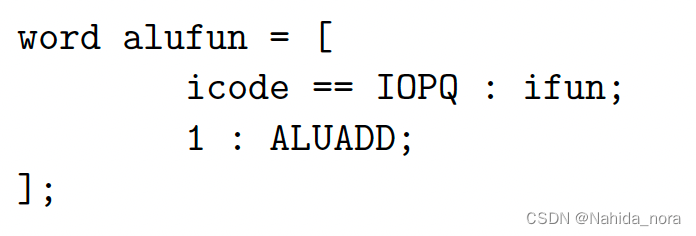

execute stage

the ALU computation for each instruction is shown as the first step in the execute stage.

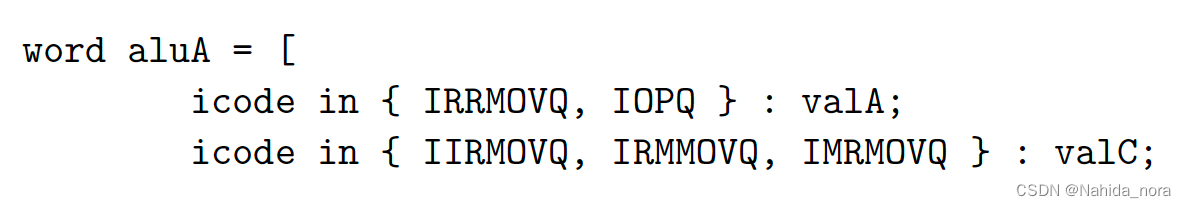

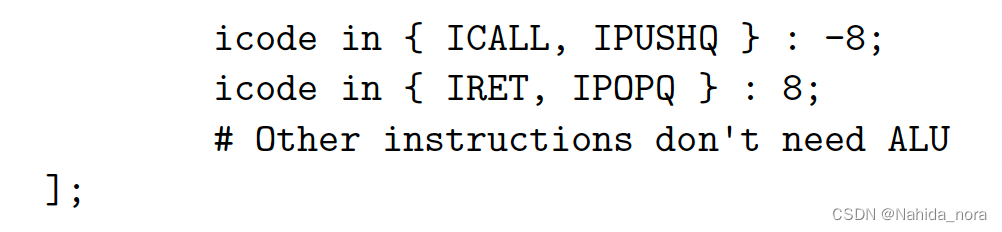

the value of aluA can be valA, valC, or either −8 or +8, depending on the instruction type.

HCL 描述 ALU control:

The execute stage also includes the condition code register.

The hardware unit labeled “cond” uses a combination of the condition codes and the function code to determine whether a conditional branch or data transfer should take place.

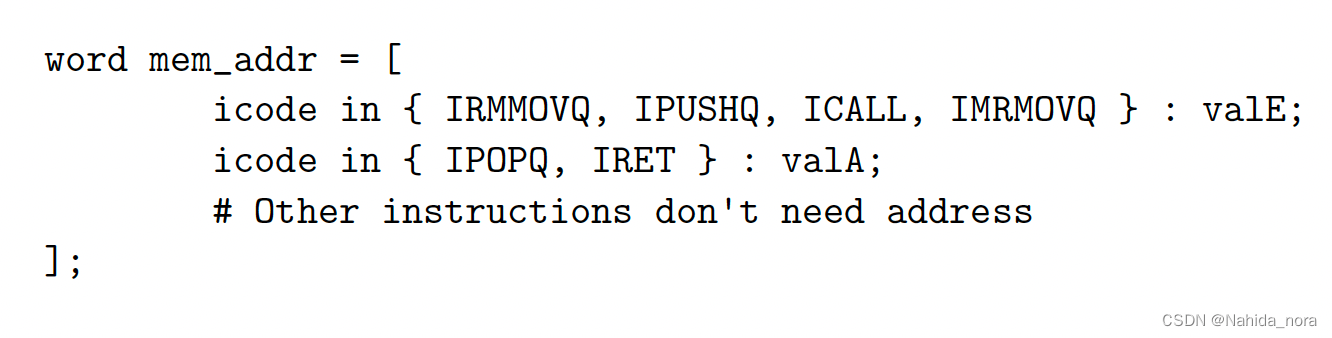

memory stage

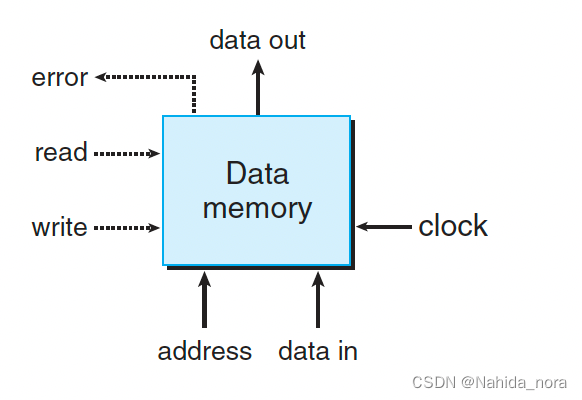

When a read operation is performed, the data memory generates the value valM.

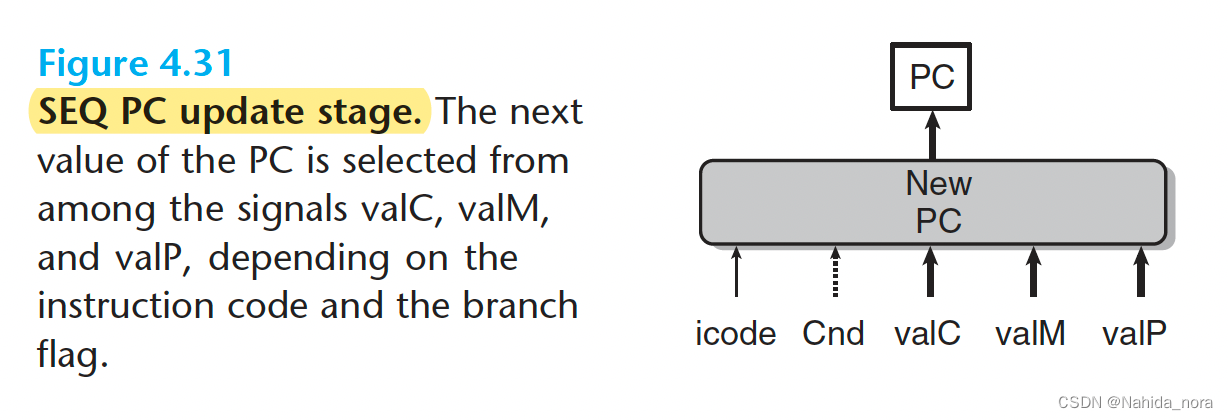

PC Update Stage

Surveying SEQ

The only problem with SEQ is that it is too slow.

links

https://zhuanlan.zhihu.com/p/107373092

https://zhuanlan.zhihu.com/p/107450834 -

相关阅读:

centos7篇---安装 rabbitmq详细教程

online schema change and create index

ubuntu设置开机自启服务脚本

Stream流中的 max()和 sorted()方法

一文带你快速入门【哈希表】

关于账号安全的一些思考

【leetcode42-----距离顺序排列矩阵单元格】

.Net-C#文件上传的常用几种方式

30分钟入门前端容器化

Qt调用工业相机之海康威视相机SDK【主动取流的使用】(完整版)

- 原文地址:https://blog.csdn.net/weixin_43876597/article/details/134467702