-

英飞凌TC3xx的LMU SRAM保护机制(一)

目录

1.基本概述

在英飞凌TC3xx中,每个CPU除了有自己的DLMU外,在SRI总线还挂着几块SRAM,这几块SRAM由LMU(Local Memory Unit)进行权限控制。

RAM的具体地址(上述9H用于cached访问,Bh用于非cached访问):

LMU除了本身硬件机制(如ecc)外,还提供了16个对SRAM区域的保护功能,这个机制主要是通过Master Tag ID的识别来限制对目标SRAM权限的访问。

要实现对RAM区域的保护,每个区域需要由6个寄存器定义,分别对应受保护SRAM区域的上下限、针对Mastr Tag ID的读权限(2个寄存器)、针对Mastr Tag ID的写权限(2个寄存器)。

与CPU的MPU相似,当定义的两块区域有交叉时, 是根据最高权限来进行分配的;

区域A:CPU0读写权限

区域B:CPU0只读权限

A\B交叉的区域:CPU0读写权限

2.理解Master Tag ID

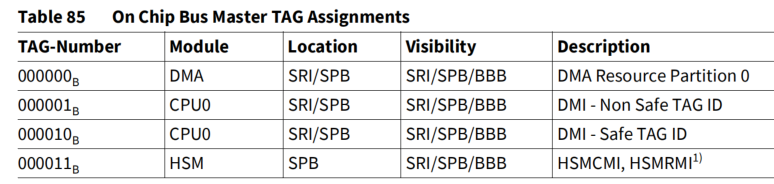

与Tricore的MPU不一样,LMU的memory保护是通过Master Tag ID来区分的,那么什么叫Master Tag ID。 根据TC3xx User Mannul章节4.10.7 ,在整个系统外设总线(SPB)或者SRI总线上,所有的Master接口都分配到了一个独立的ID,以便软件调试或者MCDS的时候辨别是哪个外设或者CPU执行了当前事务。以下图为例

如果CPU0想要访问LMU0中的资源,就需要CPU0使用MIF通过MCI发送请求给LMU0,那么不同的MIF就通过Tag ID来进行分辨。 如表格所示:

- SRI:Shared Resource Interconnect

- SPB:System Peripheral Bus

- BBB:Back Bone Bus

- DMI:Data memory interface

我们今天暂时先不管上面CPU0两个不同DMI对应的Tag ID为何不同,主要关注LMU的memory 保护机制。

3.LMU memory保护使能

有了Master Tag ID,那么接下里我们要看如何开始配置寄存器实现内存保护功能。

一个区域保护有如下6个寄存器:

- RGNLAx(x=0-15):定义受保护区域的下限

- RGNUAx(x=0-15):定义受保护区域的上限

- RGNACCENWAx(x=0-15):定义受保护区域的master(id= 0-31)的写访问

- RGNACCENWBx(x=0-15):定义受保护区域的master(id = 32-63)的写访问

- RGNACCENRAx(x=0-15):定义受保护区域的master(id= 0-31)的读访问

- RGNACCENRBx(x=0-15):定义受保护区域的master(id = 32-63)的读访问

4.小结

本章将LMU使能、master tag ID做了一个介绍,下一章将继续讲解使能和测试。

-

相关阅读:

PGSQL大小写敏感总结

Linux和Windows之间文件自动同步

十五管还原炉舟皿自动卸料单元

Callback详解

R语言使用nnet包的multinom函数构建无序多分类logistic回归模型、使用AIC函数比较两个模型的AIC值的差异(简单模型和复杂模型)

Unity Shader - 踩坑 - BRP 管线中的 depth texture 的精度问题(暂无解决方案,推荐换 URP)

【前端】从 0 到 1 实现一个网站框架(一、注册 [1] )

基于多传感器数据融合的全自动泊车系统研究与应用(文献综述)

Axios 的介绍(使用和作用)

如何在项目中使用kafka?

- 原文地址:https://blog.csdn.net/djkeyzx/article/details/134504326