-

【FPGA】Verilog:实现 RS 触发器 | Flip-Flop | 使用 NOR 的 RS 触发器 | 使用 NAND 的 RS 触发器

目录

0x00 RS 触发器(RS Flip-Flop)

触发器(Flip-Flop)是一种带有时钟的二进制存储设备,用于存储 0 和 1 的值。只有在时钟信号的边沿转换时,存储的 0 或 1 的值才会改变。

从 1 到 0 的转换称为下降沿触发,而从 0 到 1 的转换称为上升沿触发。触发器中存储的值在触发器的输入数据和先前存储的数据值的影响下完成这些转换。

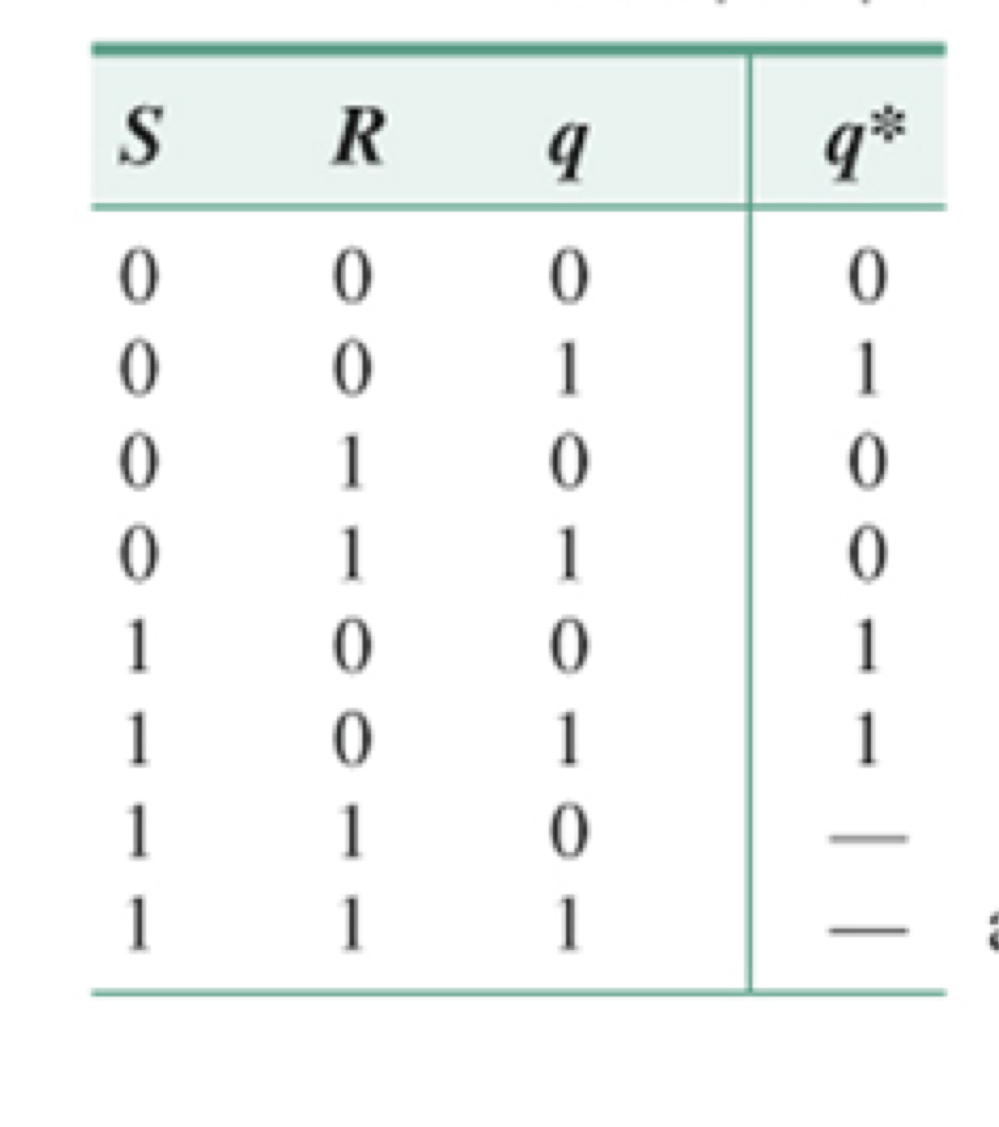

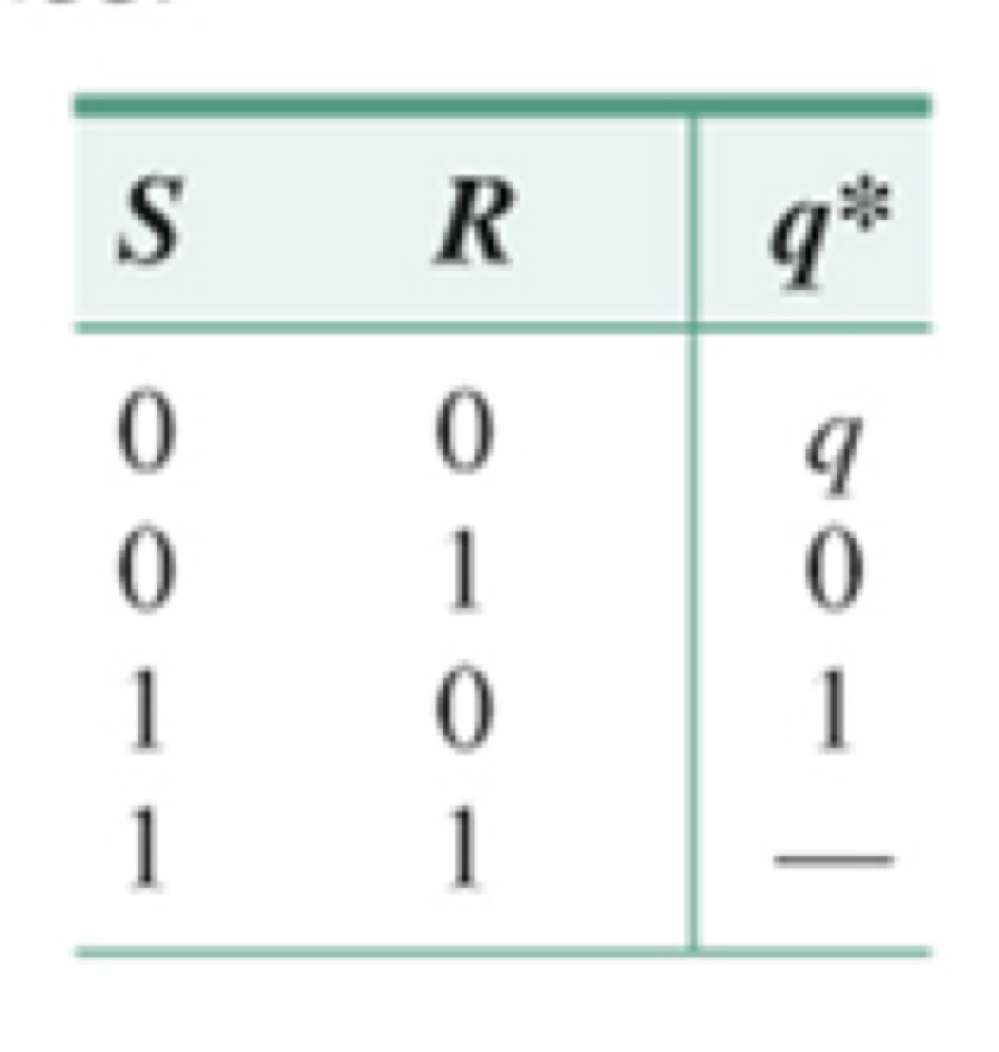

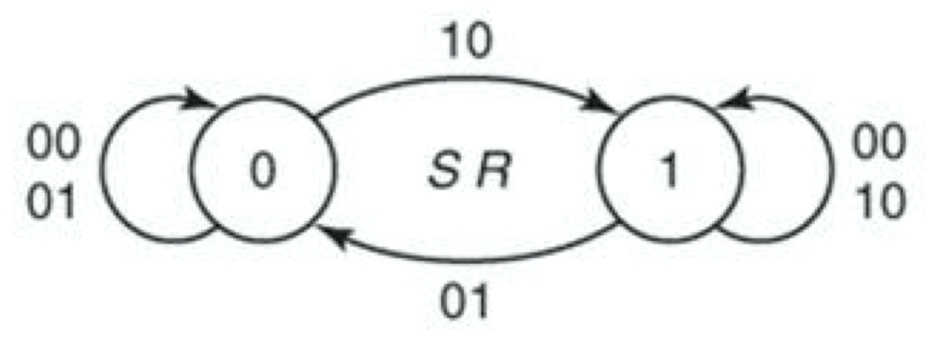

S(设置)输入会导致触发器在下一个有效时钟沿存储一个 1,而 R(复位)输入会导致触发器存储一个 0。如果 S 和 R 的值同时为 0,则触发器保持当前状态;如果两者同时为 1,则被视为非法输入。

行为表

状态图

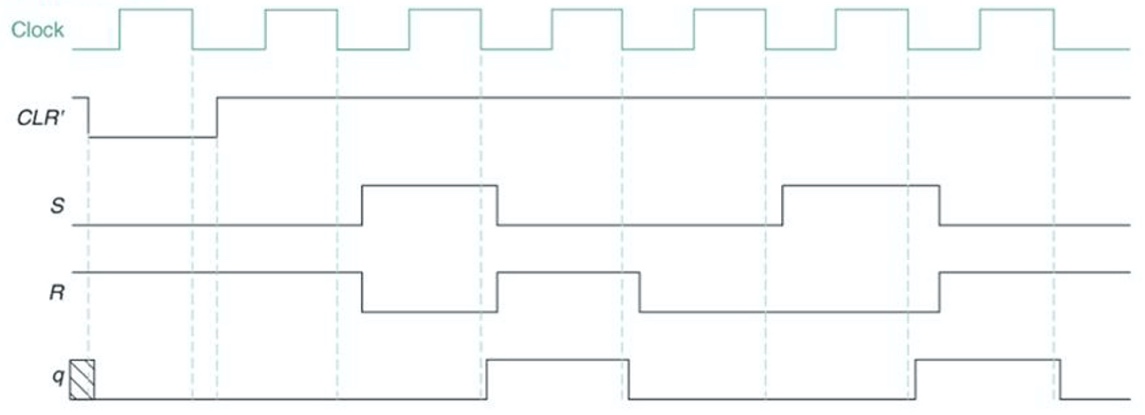

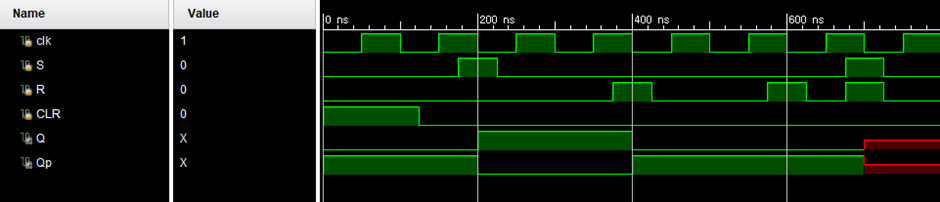

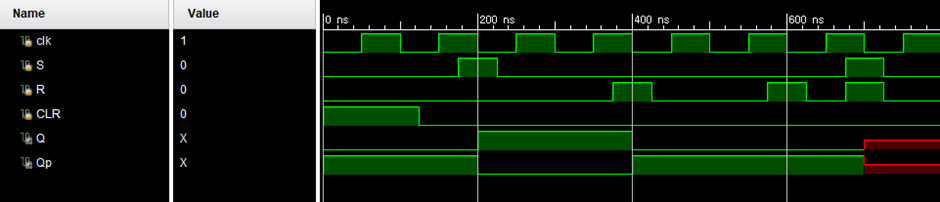

Timing Diagram

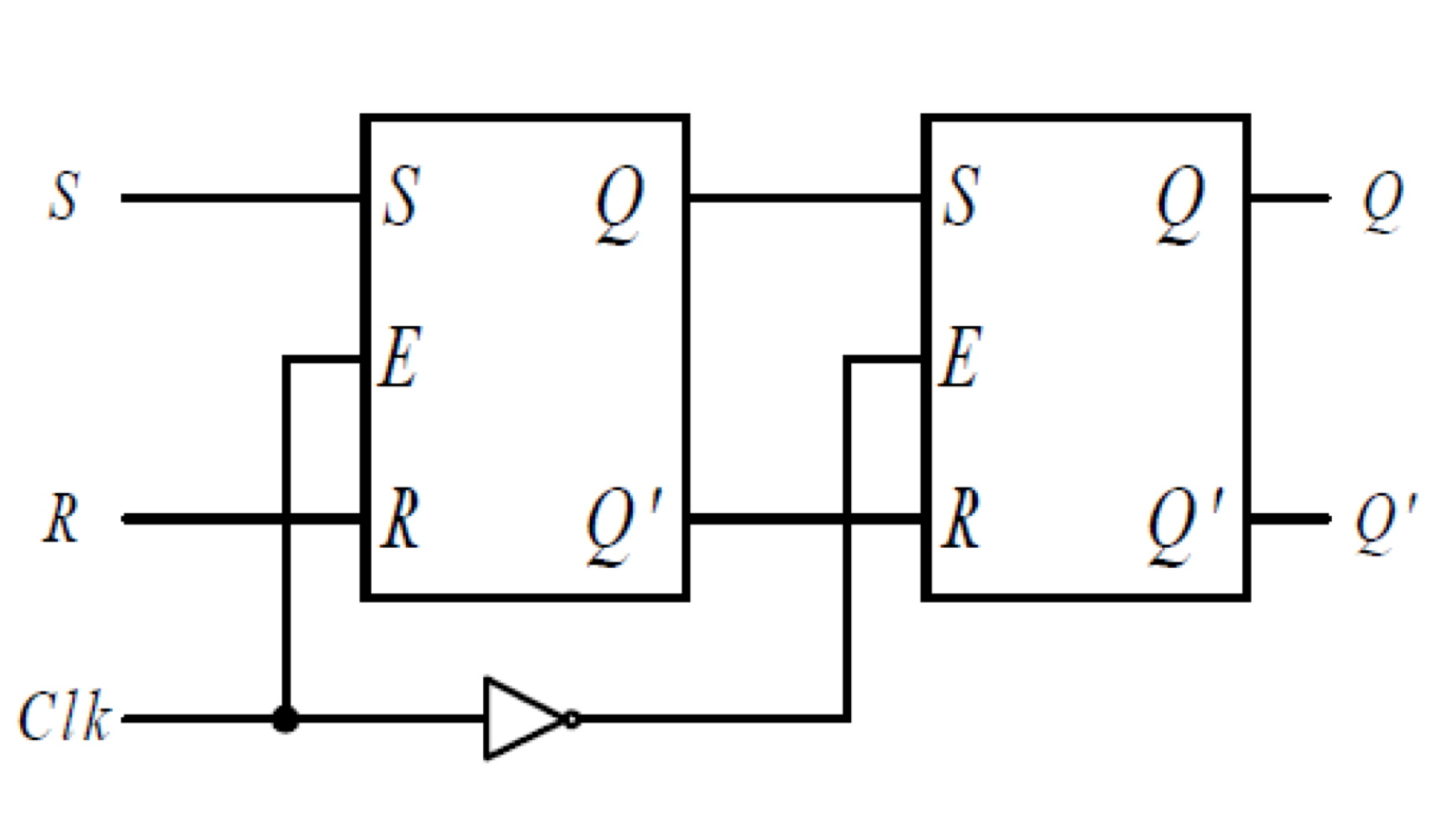

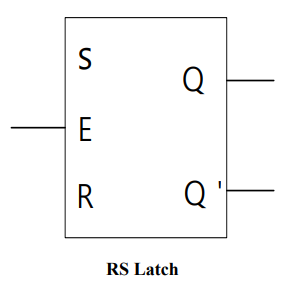

Circuit

0x01 实现 RS 触发器

真值表:

Input

Output

입력 순서

R

S

Q

~Q

1

0

1

1

0

2

0

0

1

0

3

1

0

0

1

4

0

0

0

1

5

1

0

0

1

6

1

1

X

X

0x02 使用 NOR 的 RS 触发器

💬 Design source:

- `timescale 1ns / 1ps

- module RSFF (

- input clk,

- input S,

- input R,

- input CLR,

- output Q,

- output Qp

- );

- reg Q;

- // falling edge triggered

- always @(posedge !clk) begin

- if(CLR) Q<=1'b0;

- else begin

- if ( (S == 1'b0) && (R == 1'b0) ) Q <= Q;

- else if ( (S == 1'b0) && (R == 1'b1)) Q <= 1'b0;

- else if ( (S == 1'b1) && (R == 1'b0)) Q <= 1'b1;

- else if ( (S == 1'b1) && (R == 1'b1)) Q <= 1'bx;

- end

- end

- assign Qp = ~Q;

- endmodule

💬 Testbench:

- `timescale 1ns / 1ps

- module RSFF_tb;

- reg clk, S, R, CLR;

- wire Q, Qp;

- RSFF u_RSFF(

- .clk(clk ),

- .S(S ),

- .R(R ),

- .CLR(CLR ),

- .Q(Q ),

- .Qp(Qp )

- );

- initial clk = 1'b0;

- initial CLR = 1'b1;

- initial S = 1'b0;

- initial R = 1'b0;

- always clk = #50 ~clk;

- always@(CLR) begin

- CLR = #125 ~CLR;

- end

- always@(S) begin

- S = #175 ~S;

- S = #50 ~S;

- end

- always@(R) begin

- R = #375 ~R;

- R = #50 ~R;

- end

- always@(R) begin

- R = #575 ~R;

- R = #50 ~R;

- end

- always@(S) begin

- S = #675 ~S;

- S = #50 ~S;

- end

- always@(R) begin

- R = #675 ~R;

- R = #50 ~R;

- end

- initial begin

- #800

- $finish;

- end

- endmodule

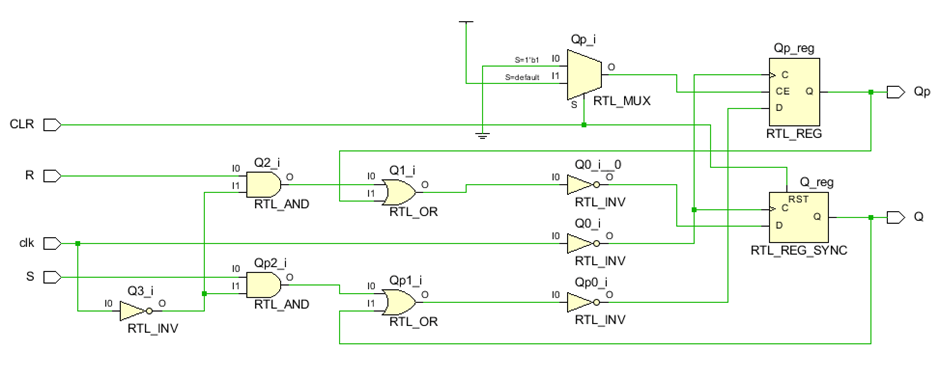

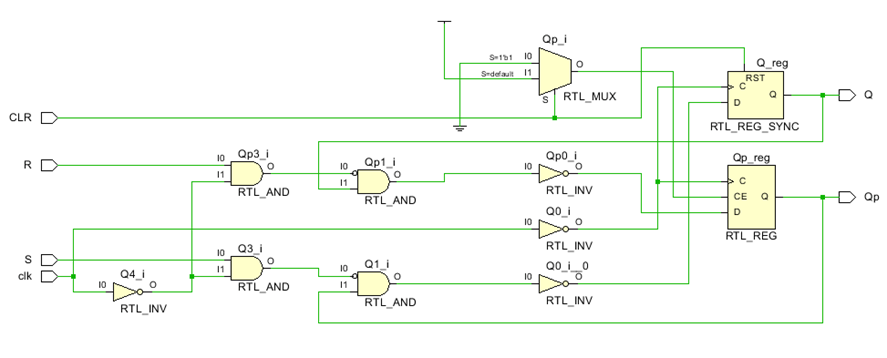

Schematic:

🚩 运行结果如下:

0x03 使用 NAND 的 RS 触发器

💬 Design source:

- `timescale 1ns / 1ps

- module RSFF (

- input clk,

- input S,

- input R,

- input CLR,

- output Q,

- output Qp

- );

- reg Q;

- // falling edge triggered

- always @(posedge !clk) begin

- if (CLR) Q << 1`b0;

- else begin

- Q <= ~(~(S & (~clk)) & Qp);

- Qp <= ~(~(R & (~cls)) & Q);

- end

- end

- assign Qp = ~Q;

- endmodule

Schematic:

🚩 运行结果如下:

- 📌 [ 笔者 ] 王亦优

- 📃 [ 更新 ] 2022.11.19

- ❌ [ 勘误 ] /* 暂无 */

- 📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,

- 本人也很想知道这些错误,恳望读者批评指正!

📜 参考资料

Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008

Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. .

百度百科[EB/OL]. []. https://baike.baidu.com/.

-

相关阅读:

Kubeadm搭建kubernetes集群

【概率论基础进阶】随机变量及其分布-随机变量函数的分布

UE5 C++ 斯坦福 1

基本if选择结构以及random

Ubuntu18.04运行gazebo的launch文件[model-4] process has died报错

Linux开发工具使用

语言模型的发展

通信原理 | 宽带:运营商的带宽和实际网速的关系

bert-base-cased问题

java刷题day 03

- 原文地址:https://blog.csdn.net/weixin_50502862/article/details/134493144