-

【紫光同创国产FPGA教程】【PGC1/2KG第七章】7.数字钟实验例程

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

适用于板卡型号:

紫光同创PGC1/2KG开发平台(盘古1K/2K)

一:盘古1K/2K开发板(紫光同创PGC2KG开发平台)简介

盘古1/2K 开发板是一套基于紫光 FPGA 的开发套件,以紫光 Compa 系列PGC1KG-LPG100 / PGC2KG-LPG100 器件为核心,预留丰富的扩展 IO 及数码管、按键、LED 灯,为用户提供基本的硬件环境。

二:实验目的

设计一个具有计时功能和校时功能的数字时钟

三:实验要求

数码管显示小时和分钟,秒钟用 LED 闪烁标识。

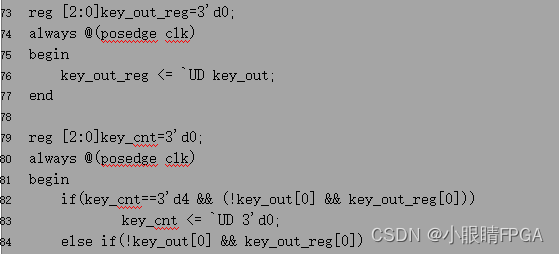

三个按键用于时钟校准。

K1 用于切换正常计时,校准小时和分钟

K2 用于时钟的“+”

K3 用于时钟的“-”

校准相应的刻度,该数码管闪烁。

四:实验原理

从上述的实验要求分析可得到此数字钟我们实现过程中要注意两个功能点:

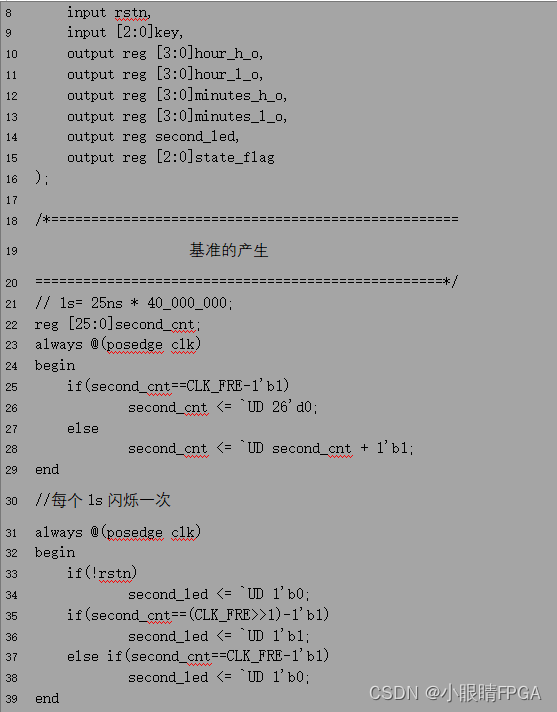

- 计时显示功能:LED闪烁显示秒钟读秒,数码管右侧两位显示分钟计时,数码管左侧两位显示时钟计时;

此功能的实现由两个细节功能实现:1S计时控制,与前面的实验中需要计时功能模块实现方式一致,注意此处计时的周期为1S即可;‚计时过程中进位控制;进位控制有四处需要进位:

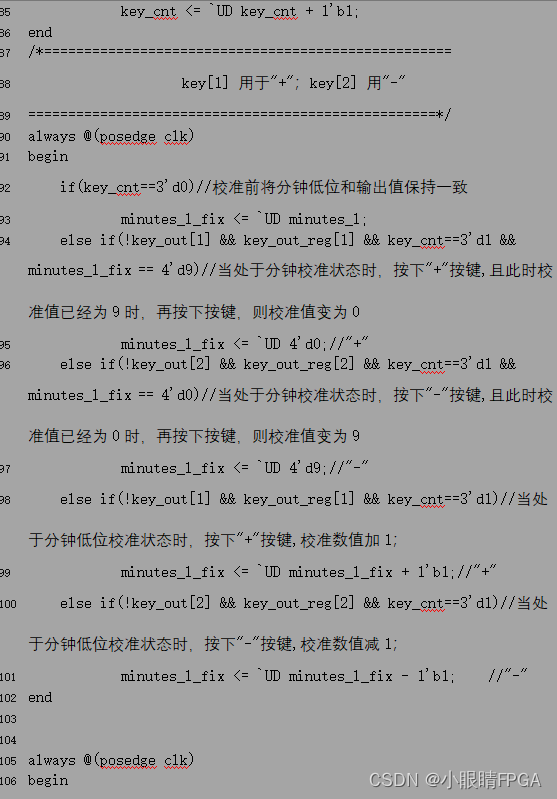

2.计时校准功能:通过对应按键控制调整分钟计时与时钟计时,调整的过程中对应位需要闪烁;

2.计时校准功能:通过对应按键控制调整分钟计时与时钟计时,调整的过程中对应位需要闪烁;此项功能中注意两点:调整对应位是,数码管该位进行闪烁;‚调整时注意进位;

基于上述分析我们将项目分成两个部分:

1. 时钟计时与控制。

2. 数码管显示控制。

五:实验源码(完整源码查看demo源文件)

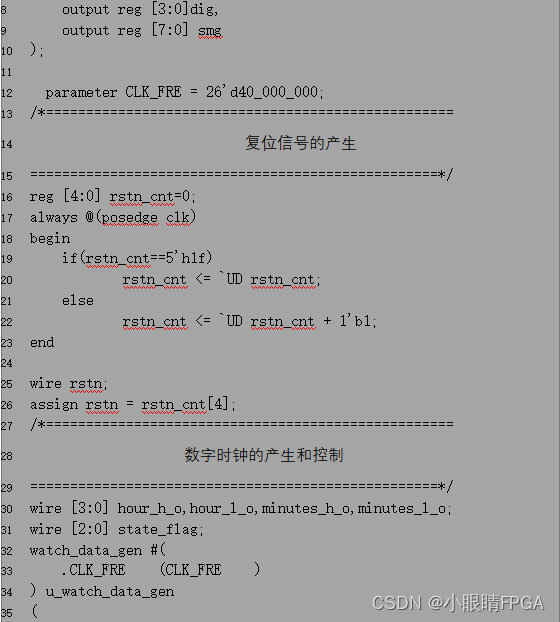

1.顶层设计

输入输出信号如下表:

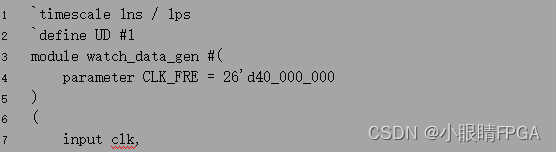

2.数字时钟产生与控制模块设计

在此模块中我们要实现前面描述的两个主要的功能点:计时与控制;

输入输出信号如下表:

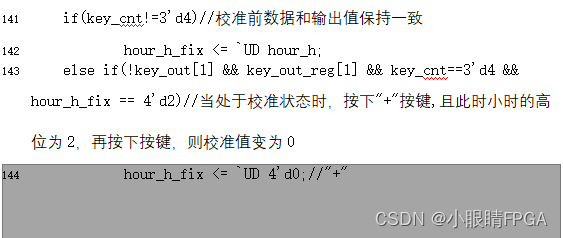

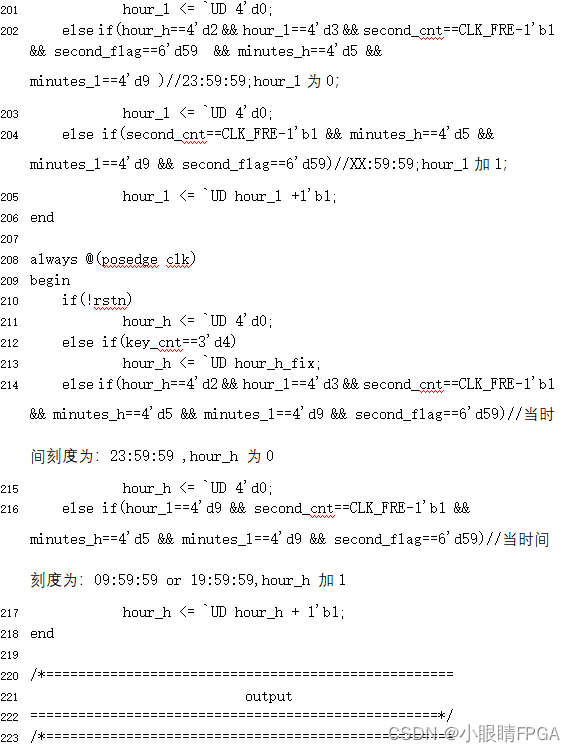

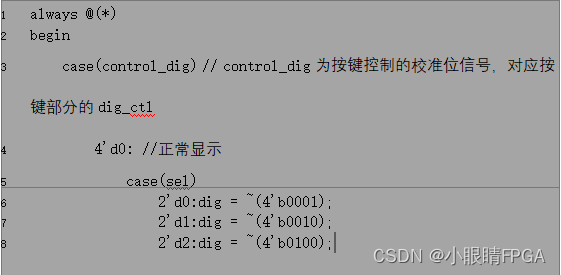

Module设计的关键点如下(完整module查看源文件):

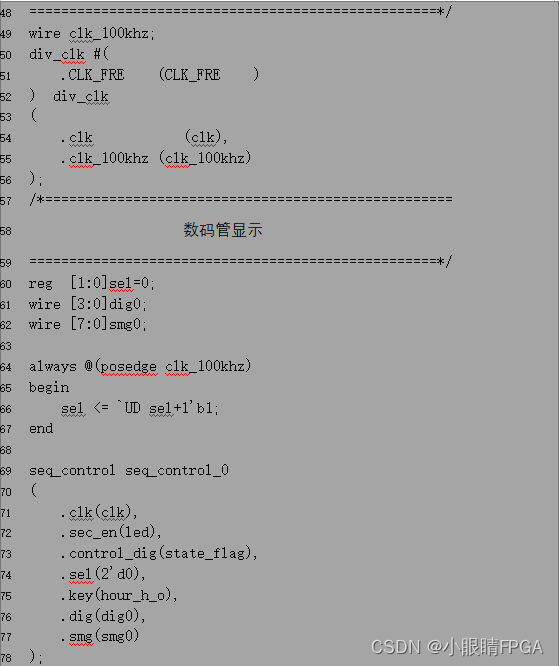

3.时钟分频模块

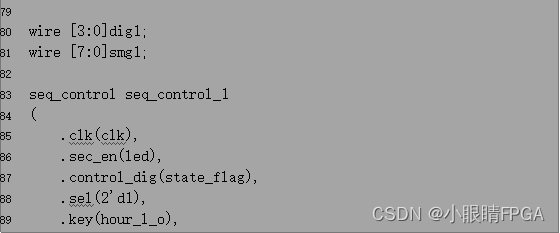

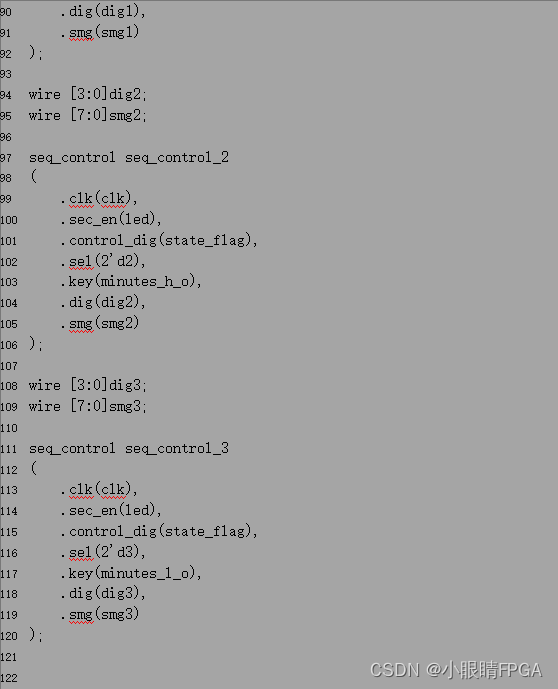

4.数码管显示模块设计

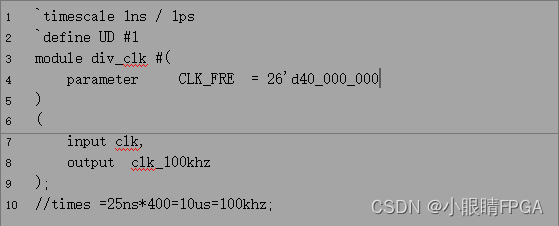

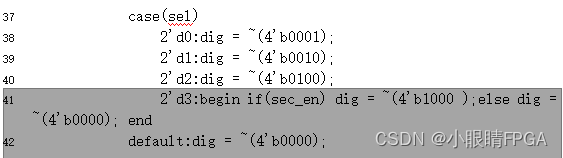

数码管显示模块相比前一个实验需要增加一个功能:当进入校准模式时数码管的校准位需要进行闪烁,故而引入一个1S的周期信号,在1S时间内0.5s正常点亮,0.5s不点亮使得数码管闪烁;闪烁对应位需要引入按键控制输出的dig_ctl信号(前面代码中有描述);

闪烁控制的模块设计如下:

六:实验现象

加载后的显示结果为:数码管显示从00:00开始,LED1闪烁(1次/s);

按轻触按键KEY1,进入校准模式,第一次按下KEY1,进入分钟低位计数校准调节,之后再次按下KEY1,校准位将会往左移动1位,直到校准位为时钟计数高位时,按下KEY1将推出校准模式,进入正常计数模式;

在校准模式中按下轻触按键KEY2一次,对应校准位加1,在可计数的最大值时会归0;

在校准模式中按下轻触按键KEY3一次,对应校准位减1,在减到0时会置位为可计数的最大值;

-

相关阅读:

稳定版正式发布 | 用 Flutter 构建 Windows 桌面应用程序

Redis的集群方案

一起来看流星雨啦,哈哈哈哈

AndroidT(13) -- logger_write 库实现解析(四)

晚上没事干又想利用时间赚钱,那就做副业,不要再懒了

TestDeploy v3.0构思

Qt5开发从入门到精通——第六篇一节( 图像与图片——位置相关函数 )

光栅投影三维重建

使用dumuz工具实现淘宝收藏的宝贝批量下载(批量导出)

饮酒后回家途中死亡,同饮者是否担责?

- 原文地址:https://blog.csdn.net/MYMINIEYE/article/details/134294554