-

【【萌新的FPGA学习之FIFO的介绍】】

萌新的FPGA学习之FIFO的介绍

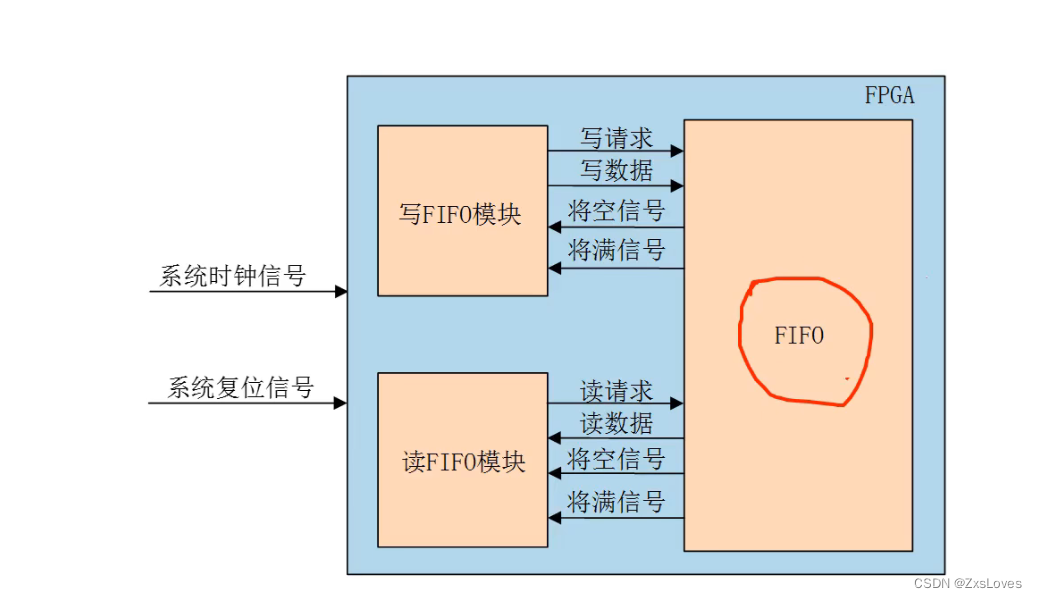

FIFO first in first out FIFO 的作用更多的是 缓冲与缓存

或者FIFO 也常被用来使用为

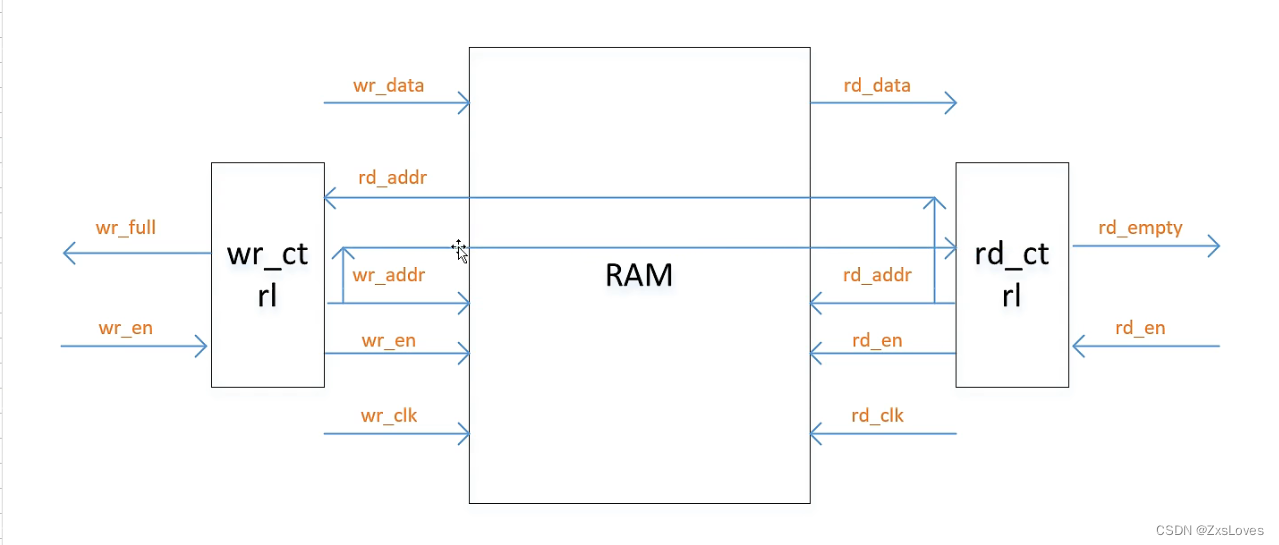

FIFO 本质上是由 RAM 加读写控制逻辑构成的一种先进先出的数据缓冲器,其与普通存储器 RAM 的

区别在于 FIFO 没有外部读写地址线,使用起来非常简单,但 FIFO 只能顺序写入数据,并按顺序读出数据,

其数据地址由内部读写指针自动加 1 完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定

的地址,不过也正是因为这个特性,使得 FIFO 在使用时并不存在像 RAM 那样的读写冲突问题。先入先出 从这里写进去的第一个数据一定会先读出

FIFO 虽然本质上是RAM 但是也分为 BRAM 和 DRAM BRAM 支持 读写位宽不同

它在设计的时候 留下了两个 almost_full 和almost_empty 空余了一个时钟周期的量 交给了 读写端 让读写端有反应时间

这里的prog_full 设置为可编程的拉高或拉低FIFO 并不需要提供地址 相对于 RAM 而言

它是一种先进先出的概念

进制 :

独热码假设是4bit : 0001, 0010, 0100 , 1000 ; 在做仲裁的时候 使用

格雷码 : 每个相邻的数之间,只有一个bit在变化为什么还要用格雷码呢?

主要用来处理跨时钟域的问题 ,在跨时钟域时数据很容易出现亚稳态。我们先来 分析一下 整个的 写控制模块

如果en 拉高一次 , 地址就增加一次 , 再把增加的地址转成格雷码 , 再从这个口传输给我们的RAM

控制模块最关键的是 这个 gary_com 格雷码比较模块FIFO 满情况 :

因为转了一圈 读写的地址都是一样的

读地址追上了写地址 就是空

写地址追上了读地址 就是满判断满的情况是 : 写指针和读指针 相比 最高位不相等 ,剩下的位数全相等

判断空的情况是 : 读和写指针 最高位相等 ,剩下的位数全相等 -

相关阅读:

Python | 快速获取某一列数组中前 N 个最大值/最小值的索引 | 三种方法总结

cnpm安装步骤

Kafka在美团数据平台的实践

[晕事]今天做了件晕事22;寻找99-sysctl.conf; systemd

Java进阶(十一)缓冲流

Git基本指令

idea反编译

2022年秋季PAT线上考试总结

Spring知识点总结-DX的笔记

美团加大了对AI大模型领域的投入!

- 原文地址:https://blog.csdn.net/weixin_50965981/article/details/134062458