-

AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (三)

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成(一)

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (二)

参考资料:

UltraScale Architecture GTH Transceivers User Guide UG576Generic JESD204B block designs

前言

结合之前两讲内容,梳理 AD9371官方 demo 时钟,理解采样率和各个时钟之间的关系

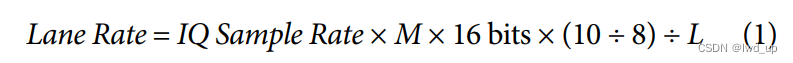

一、AD9371官方例程 LineRate

AD9528 输出的OUT1 时钟 通过FMC 连接到FPGA,差分时钟信号通过 IBUFDS_GTE4 得到 ref_clk1 ,ref_clk1 连接到 block design 的 rx_ref_clk_0 、rx_ref_clk_2 和 tx_ref_clk_0 。

.rx_ref_clk_0 (ref_clk1), .rx_ref_clk_2 (ref_clk1), ... .tx_ref_clk_0 (ref_clk1),- 1

- 2

- 3

- 4

tx_ref_clk_0 ——> util_ad9371_xcvr ip 的 qpll_ref_clk_0

rx_ref_clk_0 ——> util_ad9371_xcvr ip 的 cpll_ref_clk_0 和 cpll_ref_clk_1

rx_ref_clk_2 ——> util_ad9371_xcvr ip 的 cpll_ref_clk_2 和 cpll_ref_clk_3

qpll_ref_clk_0 连接到 QPLL0 和 QPLL1 的参考时钟

.GTREFCLK00 (qpll_ref_clk), .GTREFCLK01 (qpll_ref_clk), .GTREFCLK10 (1'd0), .GTREFCLK11 (1'd0),- 1

- 2

- 3

- 4

所以 demo 中使用的这个 Quad 里的 QPLL0/1 和 4个Channel 里的每个CPLL的参考时钟都是ref_clk1 提供的

再通过 裸机C程序中的adxcvr_clk_set_rate 设置 lane_rate(根据采样率求出),ref_rate_khz 即为 ref_clk1 的122.88MHz ,根据ref_clk1 提供的122.88MHz 参考时钟,由QPLL0/1或者CPLL生成 对应LineRate所需的PLL _CLK,再由上升沿和下降沿有效得到LineRate

adxcvr_clk_set_rate(xcvr, xcvr->lane_rate_khz, xcvr->ref_rate_khz); tx_lane_rate_khz = mykDevice.tx->txProfile->iqRate_kHz * mykDevice.tx->deframer->M * (20 / no_os_hweight8(mykDevice.tx->deframer->deserializerLanesEnabled));- 1

- 2

- 3

- 4

- 5

- 6

tx_lane_rate 和 采样率之间的关系

M是有几个转换器,每个采样数据是16 bit,经过8B/10B编码到 20bit , L是有几个LANE传数据demo中 2T2R,M=4(1发 需要IQ 两路转换器), L=4的情况下 ,根据IQ rate(122.88M) 可以求得所需的TxLineRate(2457.6 MHz)

IQRate = T x L i n e R a t e 20 \text {IQRate }=\frac{{TxLineRate} }{20} IQRate =20TxLineRate二、AD9371官方例程 TXOUTCLK、 TXUSRCLK 和 TXUSRCLK2

例程中 TXUSRCLK 和 TXUSRCLK2时钟 由 TXOUTCLK 经过BUFG_GT后生成,TXOUTCLK 选择的 TXPLLREFCLK_DIV1 ,又选择的 QPLL0 的参考时钟(QPLL0/1 和CPLL 同一个参考时钟),即ref_clk1

BUFG_GT i_tx_bufg ( .CE (1'b1), .CEMASK (1'b0), .CLR (1'b0), .CLRMASK (1'b0), .DIV (3'd0), .I (tx_out_clk_s), .O (tx_out_clk));- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

TXOUTCLK 经过BUFG_GT后连接到每个Channel 的 tx_out_clk_< N >,例程使用的tx_out_clk_0,输入到axi_ad9371_tx_clkgen,产生TXUSRCLK、 TXUSRCLK2和Link rate(上一讲知道 TXOUTCLK、 TXUSRCLK2和Link rate 速率都是 LineRate/40, 即IQ rate/2=61.44 )

tx_clk_0、tx_clk_1、tx_clk_2、tx_clk_3 接入每个Channel 的 TXUSRCLK 和 TXUSRCLK2.TXUSRCLK (tx_clk), .TXUSRCLK2 (tx_clk));- 1

- 2

生成的 link clk 为 链路层 和 传输层 提供 61.44MHz 时钟

三、JESD204B应用层给传输层数据的格式配置

上述可知 AD9371 官方 demo 2T2R 中 IQ 采样率= 2 * LINK rate ,JESD204B 应用层 如何 给传输层数据 ?

在物理层GTH收发器 配置为32bit模式,链路层每个LINK CLK 需要给物理层每个 LANE 32bit数据

引入 SPC :每个数据时钟周期,每个转换器,需要提供/采集几个采样点

每个 LANE需要 32bit数据,下述约束必须满足

L × 32 = M × N P × S P C L \times 32=M \times N P \times S P C L×32=M×NP×SPC

2T2R demo 中 JESD TX参数配置为 L=4; M=4; S=1; F=2; NP=16; SPC=2

S P C = L ∗ 32 / ( M ∗ N P ) \mathrm{SPC}=\mathrm{L}^{*} 32 /(\mathrm{M} * \mathrm{NP}) SPC=L∗32/(M∗NP)每个转换器提供 SPC=2个 16Bbit 采样数据 Frame0 和 Frame1拼在一起 ,每帧 F=2 ,两帧凑成 2 * 2 * 8=32bit

MmSn 表示 第m个转换器的第n个采样数据, AD9371 2T2R 中 M=4,n=SPC=2 ;[ M3S1, M3S0, M2S1, M2S0, M1S1, M1S0, M0S1, M0S0]

每个Lane 数据排列如下图所示

TX=1时,M=2,L=4,F=1,S=1, IQ 采样率= 4* LINK rate= line rate/10 ,SPC=4

数据送给官方传输层 排布如下 [ M1S3, M1S2, M1S1, M1S0, M0S3, M0S2, M0S1, M0S0]

具体数据重新映射代码见 tx_ad9371_tpl_core/tpl_core

注意 :

AD9371芯片 的 TX和RX lane rate 有速率限制(UG992),lane rate 都最低614.4MHz

当2T2R 时,M=4, L=4, IQ采样率 最低为30.72MHz,lane rate = 30.72 x 20= 614.4 MHz

当1T1R 时,M=2, L=4, IQ采样率 最低为61.44MHz,lane rate = 61.44 x 10= 614.4 MHz

而 由于在FPGA的GTH中, QPLL0/1 和CPLL的 VCO 对工作频率有要求,在当前官方例程中,TX选择的QPLL0,其最低频率为 9.8G,求最低采样率? 选择CPLL后,最低采样率?

QPLL

当 QPLL0 VCO 锁定频率 9.8304G (尽可能小),VCO 输出先过2分频 得到QPLL OUT, 再过分频器D取最大 =16,line rate (尽可能小)=(9.8304/(2*16))*2(上升沿和下降沿采样)=614.4MHz

当2T2R 时,M=4, L=4, line rate = (IQ采样率 最低为30.72MHz x 20) =614.4MHz,

当1T1R 时,M=2, L=4, line rate = (IQ采样率 最低为61.44MHz x 10) =614.4MHz,

如果TX选择 CPLL,PLL 频率 2 到 6.25 GHz,

当 CPLL VCO 锁定频率 2.4576G (尽可能小),CPLL输出过分频器D,D取最大 =8(CPLL不支持16)line rate (尽可能小)=(2457.6/8)*2(上升沿和下降沿采样)=614.4MHz

当2T2R 时,M=4, L=4, line rate = (IQ采样率 最低为30.72 MHz x 20) =614.4MHz,

当1T1R 时,M=2, L=4, line rate = (IQ采样率 最低为61.44 MHz x 10) =614.4MHz

所以 对于TX,2T2R,ZCU106(GTH)和 AD9371 都支持最低传输数据 采样率 为30.72MHz

同理, RX 和 RX_OS 见 AD9371 官方例程HDL详解之JESD204B RX侧时钟生成

-

相关阅读:

手工架设安装教程:

前端菜鸟一般不知道css可以这样命名

还在纠结笔记工具的选择么? 各种笔记工具帮你总结了

待办事项是什么意思,怎么用?

SAP UI5 应用中 MockServer 的实例化方法

C# 拨号面板 高亮显示

12-Go语言接口interface

【NoSQL】Redis介绍、安装、性能优化

【AI 编程助手】DevChat 解析:深入了解、快速配置与实际操作案例的完整指南

Redis常用数据类型及其应用场景

- 原文地址:https://blog.csdn.net/weixin_44630490/article/details/133990806