-

FPGA的64点FFT代码及报告,verilog快速傅里叶变换

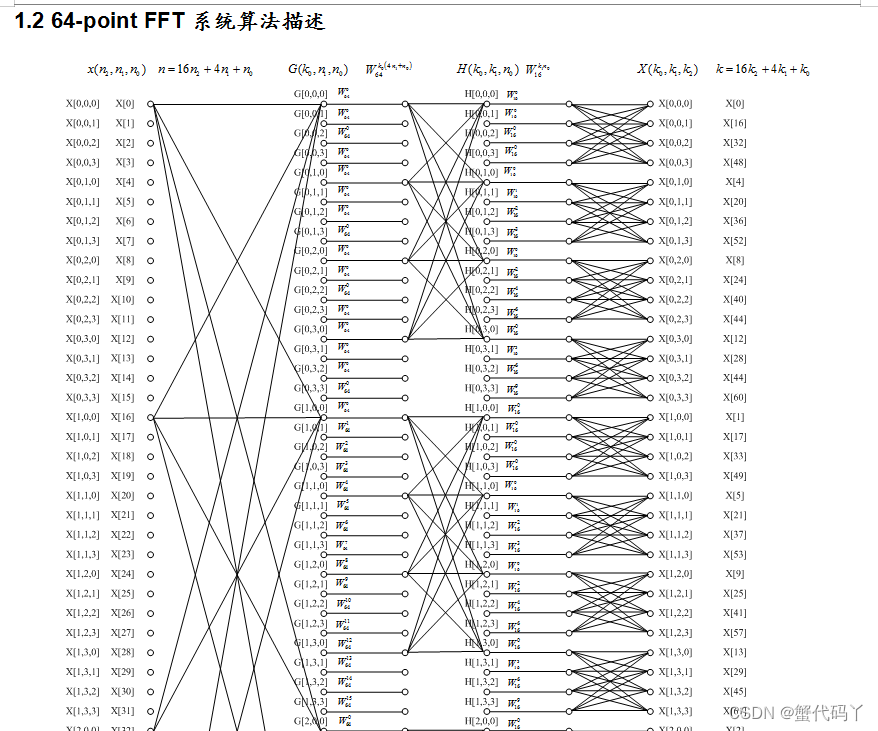

名称:64点FFT快速傅里叶变换Radix4

软件:Quartus

语言:Verilog

代码功能:

使用verilog实现64-point Pipeline FFT处理器

FPGA代码资源下载网:hdlcode.com

代码下载:

部分代码展示

module fft64_top( //input clk , rst_n , data_in_valid , data_in_re , data_in_im , //output data_out_valid, data_out_re , data_out_im , out_index ); parameter DATAWIDTH = 10 ; input clk ; input rst_n ; input data_in_valid ; input [DATAWIDTH-1:0] data_in_re ; input [DATAWIDTH-1:0] data_in_im ; output data_out_valid ; output [DATAWIDTH-1:0] data_out_re ; output [DATAWIDTH-1:0] data_out_im ; output [5:0] out_index ; reg data_out_valid ; reg [DATAWIDTH-1:0] data_out_re ; reg [DATAWIDTH-1:0] data_out_im ; reg [5:0] out_index ; wire data_out_valid_tmp ; wire [DATAWIDTH-1:0] data_out_re_tmp ; wire [DATAWIDTH-1:0] data_out_im_tmp ; wire [5:0] out_index_tmp ; wire data_out_valid_st1 ; wire [DATAWIDTH-1:0] data_out_re_st1 ; wire [DATAWIDTH-1:0] data_out_im_st1 ; wire data_out_valid_st2 ; wire [DATAWIDTH-1:0] data_out_re_st2 ; wire [DATAWIDTH-1:0] data_out_im_st2 ; always @(posedge clk or negedge rst_n) if (!rst_n) data_out_valid <= 1'b0 ; else data_out_valid <= data_out_valid_tmp ; always @(posedge clk or negedge rst_n) if (!rst_n) data_out_re <= {DATAWIDTH{1'b0}} ; else data_out_re <= data_out_re_tmp ; always @(posedge clk or negedge rst_n) if (!rst_n) data_out_im <= {DATAWIDTH{1'b0}} ; else data_out_im <= data_out_im_tmp ; always @(posedge clk or negedge rst_n) if (!rst_n) out_index <= 6'b0 ; else out_index <= out_index_tmp ; fft4_st1 u_fft4_st1_top( //input .clk(clk), .rst_n(rst_n), .data_in_valid(data_in_valid), .data_in_re(data_in_re), .data_in_im(data_in_im), //output .data_out_valid_st1(data_out_valid_st1), .data_out_re_st1(data_out_re_st1), .data_out_im_st1(data_out_im_st1) ); fft4_st2 u_fft4_st2_top( //input .clk (clk) , .rst_n (rst_n) , .data_in_valid(data_out_valid_st1) , .data_in_re (data_out_re_st1) , .data_in_im (data_out_im_st1) , //output .data_out_valid_st2(data_out_valid_st2) , .data_out_re_st2 (data_out_re_st2) , .data_out_im_st2 (data_out_im_st2) ); bu4_st3 u_bu4_st3_top( //input .clk (clk) , .rst_n (rst_n) , .data_in_valid (data_out_valid_st2) , .data_in_re (data_out_re_st2) , .data_in_im (data_out_im_st2) , //output .data_out_valid (data_out_valid_tmp) , .data_out_re (data_out_re_tmp ) , .data_out_im (data_out_im_tmp ) ); out_index u_out_index_top( //input .clk (clk) , .rst_n (rst_n) , .start (data_out_valid_tmp) , //output .out_index (out_index_tmp) ); endmodule设计报告(可下载):

-

相关阅读:

终于辞职了,全职ue了

tensorflow安装踩坑总结

celery apply_async定时任务重复执行问题

Python学习之四 数据输入与输出

Python爬虫大作业+数据可视化分析(抓取python职位)

Qwt开发笔记(一):Qwt简介、下载以及基础demo工程模板

Webfunny前端监控如何接入飞书单点登录(SSO)

Redis笔记

【代码源每日一题Div1】平方计数「nlogn巧妙枚举倍数优化」

【java毕业设计源码】基于SSM的疫情社区物资配送系统

- 原文地址:https://blog.csdn.net/diaojiangxue/article/details/133967357

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=209

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=209