-

FFT64点傅里叶变换verilog蝶形运算,代码和视频

名称:FFT64点verilog傅里叶变换

软件:Quartus

语言:Verilog

代码功能:

使用verilog代码实现64点FFT变换,使用蝶形运算实现傅里叶变换

演示视频:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=208

FPGA代码资源下载网:hdlcode.com

代码下载:

部分代码展示

`timescale 1ns / 1ps //64点FFT module top(input clk, input rst, input [7:0] data_in_r, input [7:0] data_in_i, input data_in_ready, output [19:0] data_out_r, output [19:0] data_out_i, output reg data_out_ready ); wire working; reg [5:0] count; reg [5:0] count_out; reg flag; reg working_flag_0; reg working_flag_1; reg working_flag_2; reg working_flag_3; reg working_flag_4; reg working_flag_5; reg working_flag_6; reg working_flag_7; assign working = data_in_ready || working_flag_1; always @(posedge clk) begin if(rst) begin count<=6'd0; end else begin if(!data_in_ready) count<=6'd0; else begin if(count < 6'd63) count<=count+6'b1; else count <= count; end end end always@(posedge clk) begin if(rst) working_flag_0 <= 0; else if(working && working_flag_1 == 0) working_flag_0 <= 1; else working_flag_0 <= 0; end always@(posedge clk) begin if(rst) flag <= 0; else if(count == 6'd62 && flag == 0) flag <= 1; else flag <= 0; end always@(posedge clk) begin if(rst) working_flag_1 <= 0; else if(count == 6'd63 && flag == 1) working_flag_1 <= 1; else working_flag_1 <= 0; end always@(posedge clk) begin if(rst) working_flag_2 <= 0; else if(working_flag_1) working_flag_2 <= 1; else working_flag_2 <= 0; end always@(posedge clk) begin if(rst) working_flag_3 <= 0; else if(working_flag_2) working_flag_3 <= 1; else working_flag_3 <= 0; end always@(posedge clk) begin if(rst) working_flag_4 <= 0; else if(working_flag_3) working_flag_4 <= 1; else working_flag_4 <= 0; end always@(posedge clk) begin if(rst) working_flag_5 <= 0; else if(working_flag_4) working_flag_5 <= 1; else working_flag_5 <= 0; end always@(posedge clk) begin if(rst) working_flag_6 <= 0; else if(working_flag_5) working_flag_6 <= 1; else working_flag_6 <= 0; end always@(posedge clk) begin if(rst) working_flag_7 <= 0; else if(working_flag_6) working_flag_7 <= 1; else if(count_out < 6'd63 && working_flag_7 == 1) working_flag_7 <= 1; else working_flag_7 <= 0; end always@(posedge clk) begin if(rst) count_out <= 0; else if(working_flag_6) count_out <= 0; else if(count_out < 6'd63) count_out <= count_out + 1; else count_out <= 0; end always@(posedge clk) begin if(rst) data_out_ready <= 0; else if(working_flag_7 == 1 && data_out_ready == 0) data_out_ready <= 1; else if(count_out < 6'd63) data_out_ready <= data_out_ready; else data_out_ready <= 6'b0; end wire [15:0] data_in_r_15; wire [15:0] data_in_i_15; assign data_in_r_15={data_in_r[7],data_in_r[7],data_in_r[7],data_in_r[7],data_in_r[7],data_in_r[7],data_in_r[7],data_in_r[7],data_in_r}; assign data_in_i_15={data_in_i[7],data_in_i[7],data_in_i[7],data_in_i[7],data_in_i[7],data_in_i[7],data_in_i[7],data_in_i[7],data_in_i}; butterfly butterfly(.clk(clk), .rst(rst), .data_in_r(data_in_r_15), .data_in_i(data_in_i_15), .count(count), .count_out(count_out), .working_flag_0(working_flag_0), .working_flag_1(working_flag_1), .working_flag_2(working_flag_2), .working_flag_3(working_flag_3), .working_flag_4(working_flag_4), .working_flag_5(working_flag_5), .working_flag_6(working_flag_6), .working_flag_7(working_flag_7), .data_out_r(data_out_r), .data_out_i(data_out_i) ); endmodule设计文档:

1.工程文件

2. 程序文件

3.Testbench

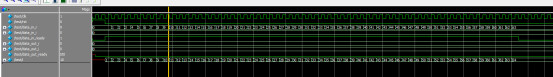

4.modelsim仿真图

-

相关阅读:

Java基于SpringBoot的闲一品交易平台

2022年最全教程:如何做大数据的采集数据及数据分析?

【Swift学习路线讲解】

全国双非院校考研信息汇总整理 Part.7

[附源码]Python计算机毕业设计Django健身生活系统论文

字符串转换整数 (atoi)

耗时7天,整理了3百多个python面试题!

基于CUBEMX的STM32F4 Hal库,配置LVGL(无操作系统版)

关于公司后端技术团队的建设

网工内推 | 国企专场,网络运维工程师,华为/思科认证优先

- 原文地址:https://blog.csdn.net/diaojiangxue/article/details/133967123

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=208

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=208