-

好的FPGA编码风格(1)--尽量避免组合逻辑环路(Combinational Loops)

什么是组合逻辑环路?

组合逻辑环路(Combinational Loops):指组合逻辑的输出信号不经过任何时序逻辑电路(FF等),而直接反馈到输入节点,从而构成的电路环路。

此外,如果直接将寄存器的输出端通过组合逻辑反馈到该寄存器的异步端口(异步复位或异步置位),也会形成组合逻辑环路。

为什么要避免组合逻辑环路?

在FPGA设计中,绝大多数的应用场景都不需要使用组合逻辑环路,我暂时能想到的例外只有随机数发生器(评论区可以补充一下)。

在实践中,避免使用组合逻辑环路主要是因为它的特性所导致的危害:

- 组合逻辑环路违反了同步设计原则,容易振荡,从而导致整个设计不稳定和不可靠。

- 组合逻辑环路的行为功能取决于该环路上的延迟(逻辑延迟和布线延迟),一旦延迟发生变化,整个设计的行为功能将变得无法预测。

- 组合逻辑环路的振荡将导致EDA软件做无穷无尽的计算。为了完成这种计算,EDA软件将会切割环路。不同的EDA软件的切割方式不尽相同,这可能会与设计者的设计目的相违背,从而导致逻辑功能错误。

- 组合逻辑环路无法进行静态时序分析(STA),可能会出现时序违例,或者导致STA过程时间过长。

什么情况会导致组合逻辑环路?

情况1:组合逻辑的输出信号仅经过组合逻辑电路后又反馈到了输入节点。比如下面的代码:

- module test(

- input in,

- output out

- );

- wire temp;

- assign out = temp;

- assign temp = ~ (temp & in);

- endmodule

这样的设计在Vivado中不会报错,但会报严重警告(Critical warning)。

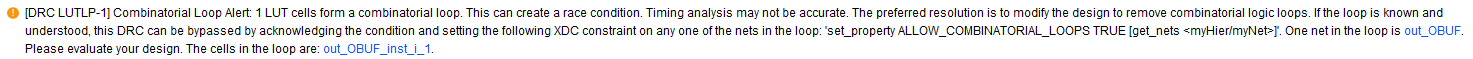

组合逻辑环路警告:1个LUT单元形成了组合循环环路。这可能会造成竞争条件。时序分析可能会不准确。推荐的解决方案是修改设计以去除组合逻辑环路。如果组合逻辑环路是已知的预期设计,则可以通过确认条件并在循环中的任何一个网络上设置以下XDC约束来绕过此DRC:“set_property ALLOW_COMBINATORIAL_LOOPS TRUE[get_nets

]”。 情况2:寄存器的输出端通过组合逻辑直接反馈到该寄存器的异步端口(异步复位或异步置位)。 比如下面的代码:

- module test(

- input in,

- input clk,

- output reg out

- );

- wire rst_n;

- always@(posedge clk or negedge rst_n)begin

- if(~rst_n)

- out <= 1'b0;

- else

- out <= in;

- end

- assign rst_n = ~ out;

- endmodule

这种情况所导致的组合逻辑环路在实践中还是比较少出现的,因为一般情况下,寄存器的异步端口都是直接由模块外部连接的信号所驱动。

如何处理组合逻辑环路?

最重要的一点:一定要坚决避免组合逻辑环路!现在的EDA工具基本上都可以把组合逻辑环路识别出来,并报错或者报警告。写完RTL代码后请一定要记得看EDA工具的报告的错误和警告信息Message!

组合逻辑环路的避免首先应该通过良好的编码习惯来避免。上述的两种示例代码就是典型的错误,请不要在设计中使用类似的代码。

如果出现了组合逻辑环路且当前设计修改困难,那么请修改你的RTL代码--通过添加寄存器的方式来切断反馈回路。就像这样:

如果组合逻辑环路的出现是符合预期设计目的的(比如随机数发生器),想将其保留该如何操作? 只要在XDC约束文件中添加这一句即可:

set_property ALLOW_COMBINATORIAL_LOOPS TRUE[get_nets

] 表示反馈回路上的一个节点,一般EDA工具都会指出这个节点,设计者只要复制替换就好了。 这条约束语句的是用来告诉EDA工具的:这条组合逻辑反馈环路是在我设计预期内的,你可以不用对其进行分析了,更不要发警告来烦我!

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

-

相关阅读:

MyBatis与Spring框架整合实现对数据库的增删改查

Qt扫盲-QPen 理论使用总结

《C和指针》笔记6

基于5G智慧园区的车联网系统应用示范

【登录扫码】--集成企业微信

【cocos源码学习】模板示例工程的目录说明

5.vue3项目(五):实现顶部导航栏功能:导航栏静态搭建,菜单折叠功能实现,面包屑动态展示路径,刷新页面功能,全屏功能

【设计模式】【第四章】【订单状态流转】【状态模式 + 享元模式+模板方法模式】

基于SpringBoot的大型商场应急预案管理系统

风口浪尖上的低代码工具革命

- 原文地址:https://blog.csdn.net/wuzhikaidetb/article/details/133893612