-

高速电路设计----第三章

一、数字信号需要上拉的情况

1、 一般信号上拉接多大的电阻要看对于芯片的电流要求。看芯片datasheet的I(BHLO)和I(BHHO)两个参数。平时的话:

3.3V的上拉为1K~3.3k即可

5V的上拉电阻为4.7K到10K即可。2、数字信号的逻辑控制,控制不好,输出端可能会有震荡。主要有三种情况:

①、开关时,信号不是马上变低和高。中间会有个过程,叫做非稳态。

解决方法: 接上拉电阻。

②、多个驱动源都能控制一个输出。解决方法: 理清逻辑,通过总线的方式。避免出现同时控制的情况。

③、引脚直接浮空

解决方法:通过接到MCU使其无效输出。 例如高电平有效就通过STM32拉低到地。使其无效。

电阻越小,上升的时间越短。但是电阻上消耗的功率越大。P=I²R。 电阻小,电流大。

上拉电阻的计算公式:

Rp= 上升的速率要求 / 2.2 * 引脚的寄生电容 * 这个信号上并联器件的数目,

引脚寄生电容的大小datasheet中应该有写。书中给的是20pF。

二、TTL、CMOS、LVTTL、LVCMOS电平。

TTL、CMOS高电平为5V.

LVTTL、LVCMOS高电平为3.3V。

如果需要把TTL电平转换为LVTTL电平:

1、用电平转换芯片 5V转3.3V

2、通过MOS管。3.5转5V

3、通过串接一个50-300Ω的电阻实现降压。(高电平换低电平)3.3转2.5V。

三、逻辑器件

逻辑器件分为三类: Bipolar(双极型)、CMOS(互补金属氧化物)、BiCMOS。

① Bipolar: 速度快、驱动能力强。但功耗大。

② CMOS:功耗低、集成度高、速度和驱动能力比 Bipolar差

③BiCMOS:以CMOS为主。集成了BiCMOS和CMOS的优点。功耗低、集成度高、速度快、驱动能力强。

逻辑器件受温度影响大。

①通常定义流入电流为正,流出器件的电流为负。

输出是高电平时,电流方向为负。为拉电流。

输出是低电平时,电流的方向为正。为灌电流。

四、器件的驱动能力

是指对负载输出信号维持能力。即负载变化大时,输出的指标依然不怎么变化的能力。

驱动能力过强会时电压过冲。所以一般选择驱动能力强的芯片。最好选里面有串接电阻,实现阻抗匹配。芯片一般是20欧左右。一般串接是33欧电阻。没有就得外接。

器件的极限参数表:

1、元器件上电和下电时,电源电压的过冲要小于极限值

2、 正常工作时,电源电压和纹波要小于极限值。Iik为输入钳位电流。 Iok为输出钳位电流。

数字电路:3.3V、5V、GND钳位一般用二极管钳位。

***输入高电平一般最小为2V。输入低电平一般最大为0.8V

***输入电容CI,在电路设计时可看作是衡量器件驱动能力的指标五、电平翻转参数

上述图片是逻辑器件电平翻转时的各项电流指标,便于器件工作不正常的时候排查。

六、信号传输特性参数

①传输延迟 tpd :强调的是输入到输出的延迟。

②输出偏移失真:强调的是不同输出引脚之间的偏移量

③脉冲失真:强调的衡量占空比失真造成的时序问题。这个在DDE和SDRA等双边沿采样的应用中尤为关键。

④封装失真:一般是不可避免的。

这些参数通常都是只有几ns,但是在高速电路中就是会有影响。

逻辑器件功耗计算:

一般资料会给一个最大功耗参数,这个参数仅能提供最恶劣情况下的功耗估算值。

如果单板功耗的裕量充足时,可直接参考这个值。但是在单板复杂度提高,高功耗器件不断增加时,功耗的分配就会越来越紧张。此时就不实用。

所以在设计中,有必要将器件的静态功耗和动态功耗区分开。便于实际评估。

静态功耗Ps

1、制造工艺不同,静态功耗差别很大。

2、当电路电平不满足打开引脚的阈值,但本身存在电压。此时也会产生功耗。

动态功耗PD

瞬变功耗PT + 容性负载功耗PL

① 瞬变功耗PT 电平转换时产生的功耗

②容性负载功耗PL

②容性负载功耗PL

举例子:

七、热插拔功能介绍

要满足在线热插拔需要要求接口支持 Ioff、PU3S、BIAS Vcc特性。

1、Ioff

如果芯片支持Ioff,则会在芯片手册中有相关描述。没有描述则表示不支持。

2、PU3S

原理就是通过R1、R2构成分压。如果VCC缓慢上升的话。节点1 的电压也是缓慢上升的。这个过程PU3S呈现高阻态。上升到节点1为高电平时才会导通,此时VCC的电压比节点1更高。能有效避免器件损坏。

3、BIAS Vcc

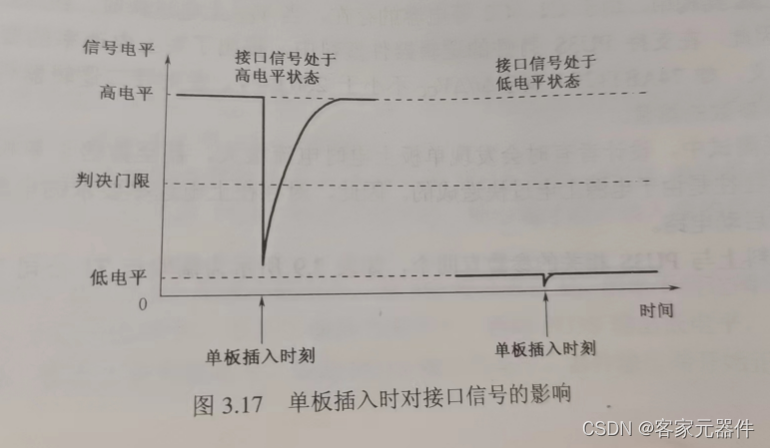

Ioff和PU3S都是实现对接口器件的硬件保护。并不能保护接口总线上正在传输的数据。

BIAS Vcc其实就是在输出端加一个预充电电路。

正常接口器件的引脚存在一定的容性,而电容就是阻碍信号电平的变化。,单板插入时,单板上接口器件的引脚倾向于将信号电平拉低,待电容充电完毕后,电平才得以恢复。

加了预充电电路 BISA Vcc后:

1、预充电电路的电源应该比Vcc先上电。

2、Icc:指预充电电路的电流,一般很小,几mA。

3、为实现热插拔,应选用长短针式信号连接器。

八、总结

1、根据需要去选型,不建议盲目的去选择性能最好的器件。盲目选择驱动能力最强的器件,一方面可能造成辐射增大,产生EMI问题。另一方面,可能会时信号输出过冲太大,超出器件所能承受的电压范围,从而损坏器件。

2、时序设计中不能依赖逻辑器件的延时,逻辑器件都具有片内传输延时,但是该参数的器件间差异性较大。不能在设计中被利用。

3、使用具有总线保持功能的器件时,需要加上下拉电阻,电阻值不能太大。阻值太大会使驱动能力变弱。

4、未用的输入端口电平为CMOS是,需做上、下拉处理。

5、电源上电的速率、输入信号边沿速率应满足器件资料中对应参数的要求。

6、在热插拔接口器件中,为防止冲击,输出端一般串接50欧姆的电阻。输入端一般应串接100~200欧姆的电阻。此时,应确认串联电阻不会对信号电平产生分压影响,以致输入端电平不能满足要求。

7、当存在热插拔要求时,应根据热插拔的级别去选择对应器件。

-

相关阅读:

【C++】vector的模拟实现

HCIP第十一天笔记

golang中的字符串

简单了解ARP协议

GPM 模型剖析【Golang】

探秘Nutch:揭秘开源搜索引擎的工作原理与无限应用可能(二)

界面组件Kendo UI for React R3 2022新版,让Web应用更酷炫

SprignCloud Alibaba集成Nacos实现服务注册、服务发现、服务调用详细代码案例

数据结构学习系列之顺序表的查找与排序以及去重

测试修改和删除用户功能、测试查询功能

- 原文地址:https://blog.csdn.net/weixin_42304393/article/details/133254046