-

基于FPGA的图像高斯滤波实现,包括tb测试文件和MATLAB辅助验证

目录

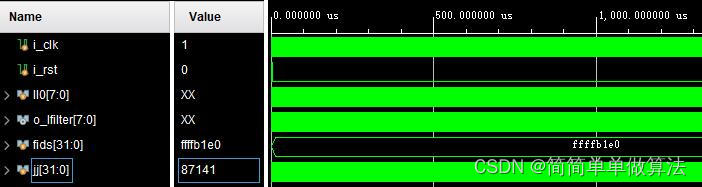

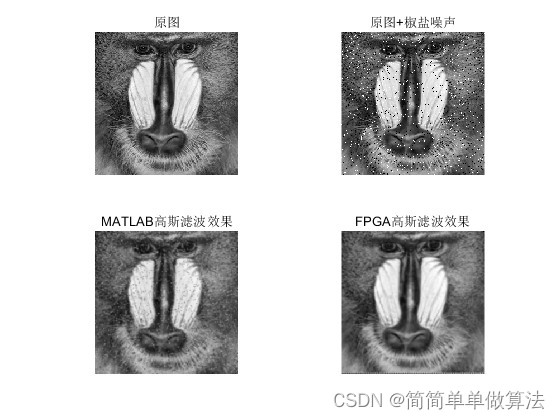

1.算法运行效果图预览

2.算法运行软件版本

vivado2019.2

3.部分核心程序

- `timescale 1ns / 1ps

- //

- // Company:

- // Engineer:

- //

- // Create Date: 2022/07/28 01:51:45

- // Design Name:

- // Module Name: test_image

- // Project Name:

- // Target Devices:

- // Tool Versions:

- // Description:

- //

- // Dependencies:

- //

- // Revision:

- // Revision 0.01 - File Created

- // Additional Comments:

- //

- //

- module test_image;

- reg i_clk;

- reg i_rst;

- reg [7:0] image_buff [0:100000];

- reg [7:0] II0;

- wire [7:0] o_Ifilter;

- integer fids,jj=0,dat;

- //D:\FPGA_Proj\FPGAtest\codepz

- initial

- begin

- fids = $fopen("D:\\FPGA_Proj\\FPGAtest\\codepz\\data.bmp","rb");

- dat = $fread(image_buff,fids);

- $fclose(fids);

- end

- initial

- begin

- i_clk=1;

- i_rst=1;

- #2000;

- i_rst=0;

- end

- always #10 i_clk=~i_clk;

- always@(posedge i_clk)

- begin

- II0<=image_buff[jj];

- jj<=jj+1;

- end

- tops tops_u(

- .i_clk (i_clk),

- .i_rst (i_rst),

- .i_I0 (II0),

- .o_Ifilter (o_Ifilter)

- );

- integer fout1;

- initial begin

- fout1 = $fopen("o_Ifilter.txt","w");

- end

- always @ (posedge i_clk)

- begin

- if(jj<=66617)

- $fwrite(fout1,"%d\n",o_Ifilter);

- else

- $fwrite(fout1,"%d\n",0);

- end

- endmodule

- 0X_016m

4.算法理论概述

基于FPGA的图像高斯滤波实现是一种利用FPGA硬件平台对图像进行高斯滤波处理的方法。下面将详细介绍这种方法的原理和数学公式。

一、原理

高斯滤波是一种线性平滑滤波,适用于消除高斯噪声,广泛应用于图像处理的减噪过程。具体来说,高斯滤波就是对整幅图像进行加权平均的过程,每一个像素点的值,都由其本身和邻域内的其他像素值经过加权平均后得到。高斯滤波的具体操作是:用一个模板(或称卷积、掩模)扫描图像中的每一个像素,用模板确定的邻域内像素的加权平均灰度值去替代模板中心像素点的值。

基于FPGA的图像高斯滤波实现,是利用FPGA并行计算的优势,对图像进行高斯滤波处理。通过FPGA硬件平台,可以实现高斯滤波算法的快速、高效运算,提高图像处理的速度和效率。

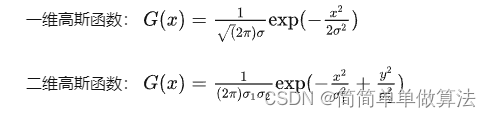

二、数学公式

高斯滤波的数学公式主要涉及到高斯函数的计算和卷积运算。具体公式如下:

高斯函数:

其中,(x,y)表示像素坐标,σ表示高斯函数的标准差,控制高斯函数的形状。

卷积运算:

设原始图像为f(x,y),高斯滤波后的图像为g(x,y),则高斯滤波的数学公式可以表示为:

g(x,y)=f(x,y)×G(x,y)g(x, y) = f(x, y) \times G(x, y)g(x,y)=f(x,y)×G(x,y)

其中,×表示卷积运算。

综上所述,基于FPGA的图像高斯滤波实现是通过利用FPGA并行计算的优势,实现高斯滤波算法的快速、高效运算,从而提高图像处理的速度和效率。具体实现过程中需要涉及到高斯函数的计算和卷积运算等数学公式。

5.算法完整程序工程

OOOOO

OOO

O

-

相关阅读:

国产大模型各自优势如何?大家都怎么选?

【Redis】Redis的应用场景

「运维有小邓」自助AD更新

JVM-Java虚拟机内存区域

[云原生] K8S 日志收集方案

逻辑漏洞——验证机制问题

Day19_8 Java学习之打印流、属性集、类加载器与反射

VS编程技巧——写好枚举后自动补全switch

JavaScript中数组方法总结(全)

Kafka 安装教程和基本操作

- 原文地址:https://blog.csdn.net/aycd1234/article/details/133864988