-

【【萌新的SOC学习之绪论】】

萌新的SOC学习之绪论

Vitis 统一软件平台的前身为 Xilinx SDK,从 Vivado 2019.2 版本开始,Xilinx SDK 开发环境已统一整合

到全功能一体化的 Vitis 中。Vitis 开发平台除了启动方式、软件界面、使用方法与 SDK 开发平台略有区别,

其他操作几乎一模一样。Vitis 可以采用 C、C++或 Python 开发以嵌入式处理器为核心的嵌入式系统,可实

现在 Xilinx 异构平台(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。它可为边缘、云

和混合计算应用加速提供统一编程模型。Vitis 可以利用与高层次框架的集成,通过加速库采用 C、C++或

Python 进行开发,或者使用基于 RTL 的加速器和低层次运行时 API 对实现方案进行粒度更精确的控制。Vitis

是应用 IDE(集成开发环境),可实现真正的同构及异构多处理器设计、调试和性能分析。

Vitis 统一软件平台是一种新增工具,用于将赛灵思软件开发的方方面面全部组合到统一的环境内。

Vitis 软件平台支持 Vitis 嵌入式软件开发流程以满足希望迁移至下一代技术的赛灵思软件开发套件

(SDK) 用户的使用需求,也支持 Vitis 应用加速开发流程,以满足希望使用基于赛灵思 FPGA 的最新软件加

速功能的软件开发者的需求。

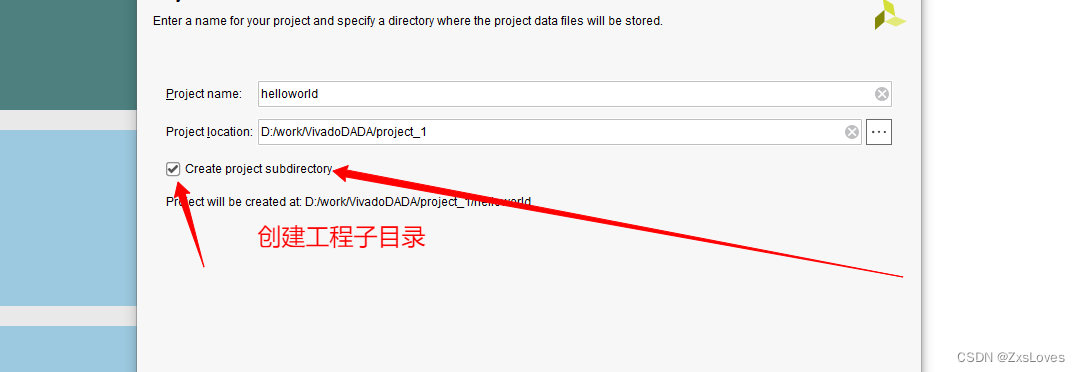

第一步:创建 Vivado 工程,创建方法和《ZYNQ 之 FPGA 开发指南》中描述的步骤一致。

第二步:使用 IP 集成器创建嵌入式处理系统,包括配置 Processing System IP、其他需要的 IP 核以及外

围设备。

第三步:对已经验证好的 Block Design 设计生成顶层 HDL。

第四步:与普通的 FPGA 开发一样,进行综合、实现并生成 Bitstream 文件和 XSA 文件,将生成的硬

件设计文件导出到 Vitis 开发平台下。

第五步:启动 Vitis,创建硬件平台工程和应用工程并完成相关程序的编写、调试、编译。

第六步:进行软硬件联调、完成功能的验证。[“Hello World!”是各种编程语言中最简单,同时也是最经典的入门实验。因此,我们将串口打印“Hello

World”作为 ZYNQ 嵌入式系统的开篇实验,这也是我们步入 ZYNQ 的 PS 部分的始发点。

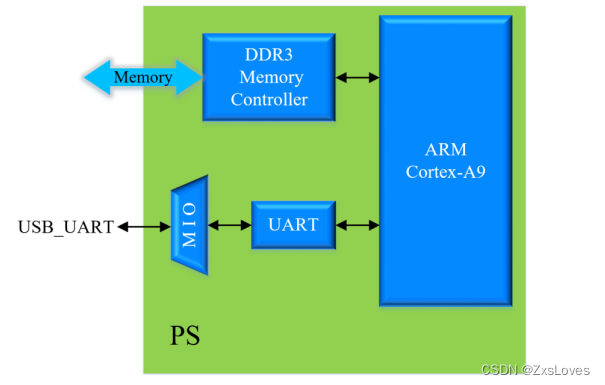

ZYNQ 是以 ARM 处理器为核心的系统,所以最小系统中应包含“ARM Cortex-A9”功能单元;系统的

运行需要存储器的支持,一般选择使用外挂的 DDR3 芯片,因此需要用到 PS 中的 DDR3 控制器;最后本次

实验通过串口打印“Hello Word”字符串,因此系统中应包含 UART 控制器,并通过 MIO 引出至端口。由

此得出本次实验的 ZYNQ 嵌入式最小系统,如下图所示。

以 ARM Cortex-A9 为核心、DDR3 为内存,加上传输信息使用的 UART 串口就构成了 ZYNQ嵌入式最小系统。

添加完成后,ZYNQ7 Processing System 模块出现在 Diagram 中

在 Zynq Block Design 页面,显示了 Zynq 处理系统(PS)的各种可配置块,其中灰色部分是固定的,绿色部分是可配置的,按工程实际需求配置。可以直接单击各种可配置块(以绿色突出显示)进入相应的

配置页面进行配置,也可以选择左侧的页导航面板进行系统配置。

PS-PL Configuration 页面能够配置 PS-PL 接口,包括 AXI、HP 和 ACP 总线接口。

Peripheral IO Pins 页面可以为不同的 I/O 外设选择对应的 MIO/EMIO 引脚。

MIO Configuration 页面可以为不同的 I/O 外设具体配置 MIO/EMIO 引脚,例如电平标准等。

Clock Configuration 页面用来配置 PS 输入时钟、外设时钟,以及 DDR 和 CPU 时钟等。

DDR Configuration 页面用于设置 DDR 控制器配置信息。

SMC Timing Calculation 页面用于执行 SMC 时序计算。

Interrupts 页面用于配置 PS-PL 中断端口。 -

相关阅读:

Python学习笔记(四)

深度学习-第二章-Window下Yolov5训练打电话

2. 处理脚本命令行参数

变分自编码器 (Variational Autoencoders, VAEs)

现代修谱有4个事情尽量不要做,避免掉坑

教你解决msvcp140.dll丢失方法,全面分析msvcp140.dll丢失原因

No URLs will be polled as dynamic configuration sources警告处理

Spring Security三更草堂课程截图

rust声明式宏

logback--基础--05--配置--encoder

- 原文地址:https://blog.csdn.net/weixin_50965981/article/details/133275893