-

Quartus乒乓球游戏控制器VHDL

名称:乒乓球游戏控制器VHDL

软件:Quartus

语言:VHDL

要求:

综合实验乒乓球游戏设计要求

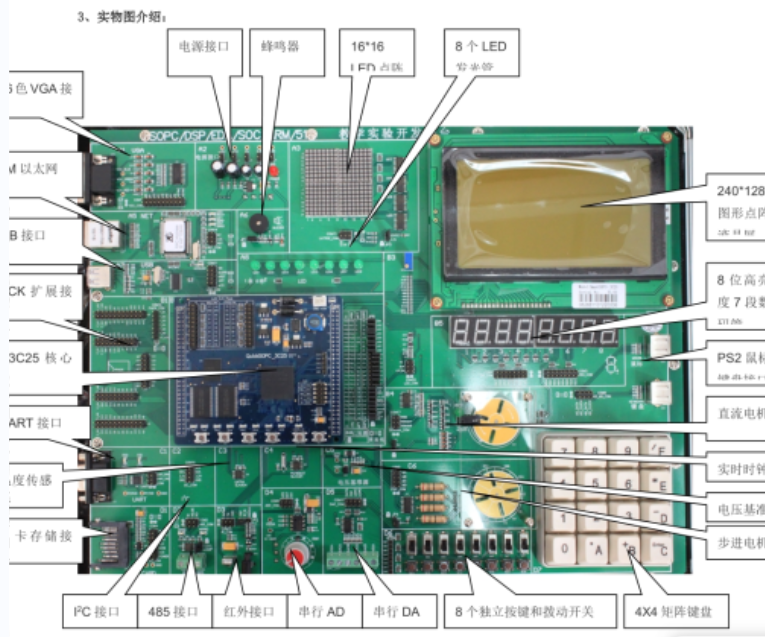

两人的乒乓球游戏机是由8个 LED 表示球台,8个 LED 灯的编号为1~8,两名选手分别是 A 和 B ,当 A 选手准备开球时,led1亮,当 A 选手按下击球键, led 灯从1开始往8号以流水灯形式流动表示乒乓球的移动,当灯超过5号灯(包含5号灯) B 选手可以击球,当灯在5号8号之间都表示 B 击球有效,击球后灯返回移动,超过4号灯之后, A 选手可以击球,当灯在4号~1号灯之间表示 A 击球有效。周而复始。

本代码已在实验箱验证:

代码下载:乒乓球游戏控制器VHDL_Verilog/VHDL资源下载

代码网:hdlcode.com

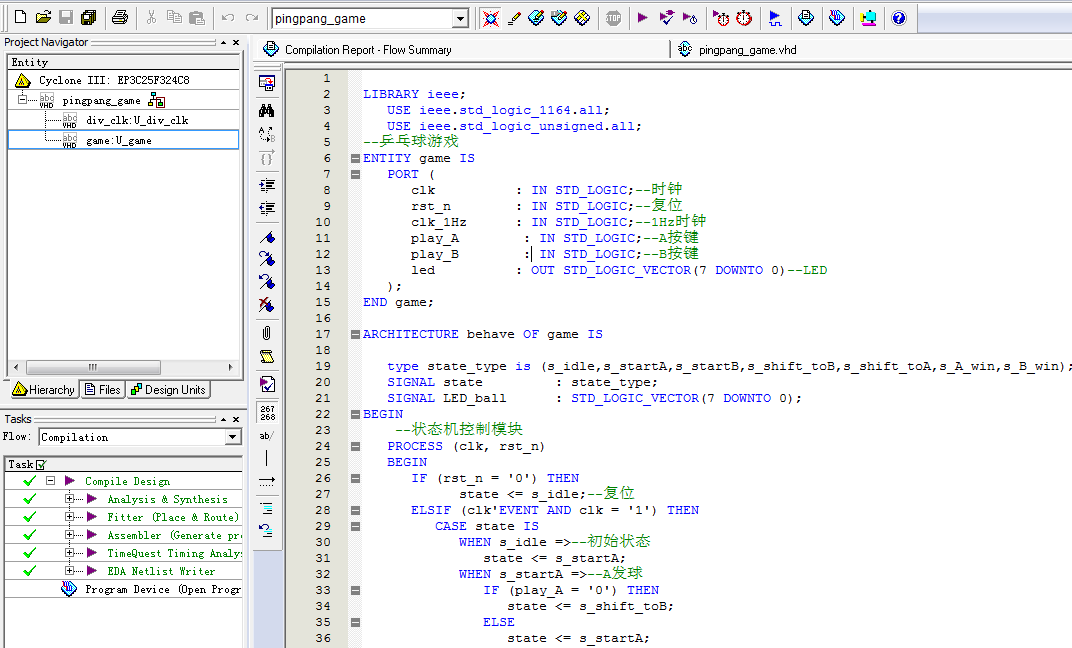

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --乒乓球游戏 ENTITY pingpang_game IS PORT ( clk : IN STD_LOGIC;--时钟 rst_n : IN STD_LOGIC;--复位 play_A : IN STD_LOGIC;--A按键 play_B : IN STD_LOGIC;--B按键 led : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--LED ); END pingpang_game; ARCHITECTURE behave OF pingpang_game IS --分频模块 component div_clk IS PORT ( clk : IN STD_LOGIC;--时钟 rst_n : IN STD_LOGIC;--复位 clk_1Hz : OUT STD_LOGIC--1Hz ); END component; --乒乓球游戏 component game IS PORT ( clk : IN STD_LOGIC;--时钟 rst_n : IN STD_LOGIC;--复位 clk_1Hz : IN STD_LOGIC;--1Hz时钟 play_A : IN STD_LOGIC;--A按键 play_B : IN STD_LOGIC;--B按键 led : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--LED ); END component; SIGNAL clk_1Hz : STD_LOGIC; BEGIN --分频模块 U_div_clk: div_clk PORT MAP( clk =>clk,--时钟 rst_n =>rst_n,--复位 clk_1Hz =>clk_1Hz--1Hz ); --乒乓球游戏 U_game: game PORT MAP( clk =>clk,--时钟 rst_n =>rst_n,--复位 clk_1Hz =>clk_1Hz,--1Hz时钟 play_A =>play_A,--A按键 play_B =>play_B,--B按键 led =>led--LED ); END behave;

设计文档(文档点击可下载):

1. 工程文件

2. 程序文件

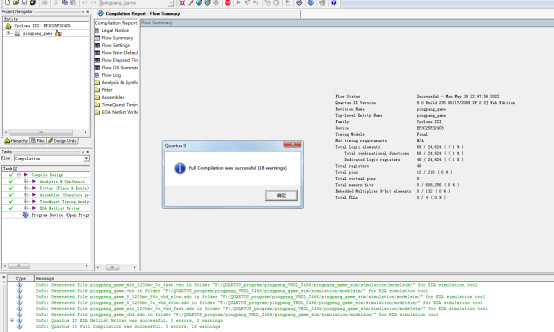

3. 程序编译

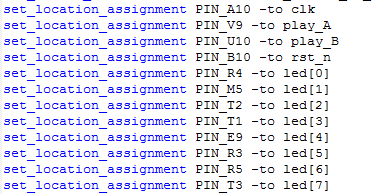

4. 管脚分配

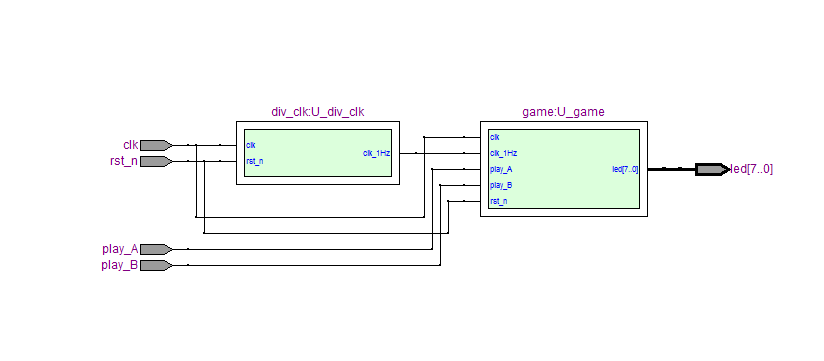

5. RTL图

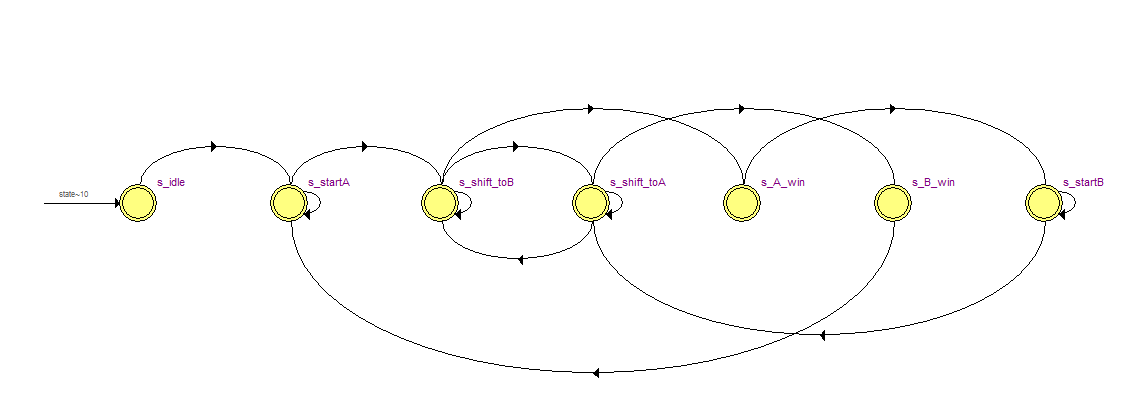

状态图

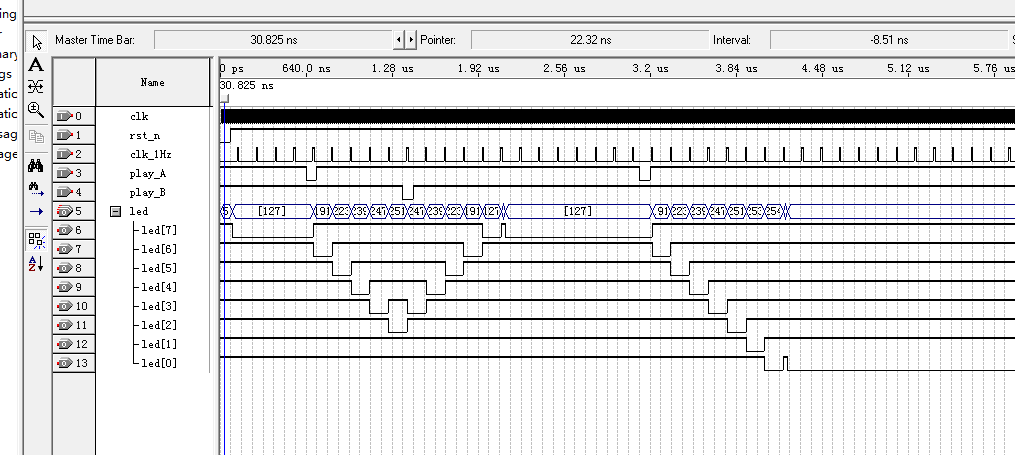

6. 仿真图

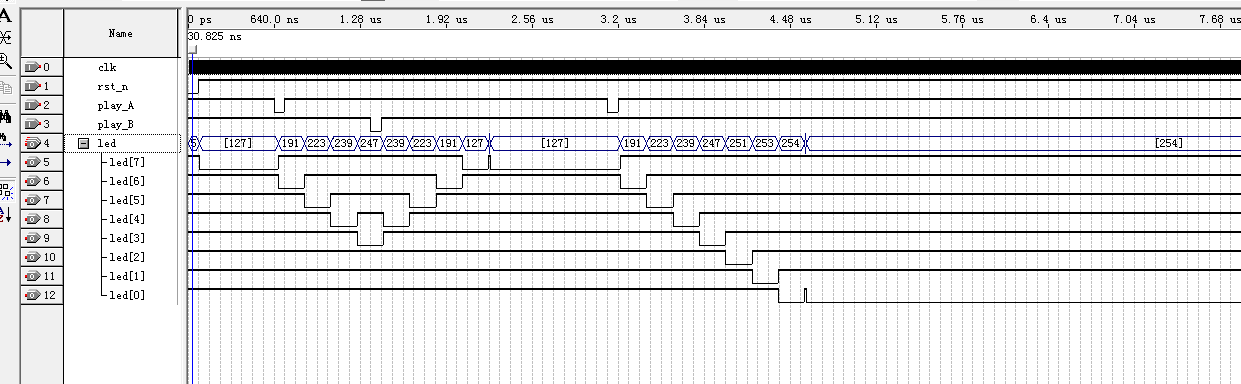

整体仿真图

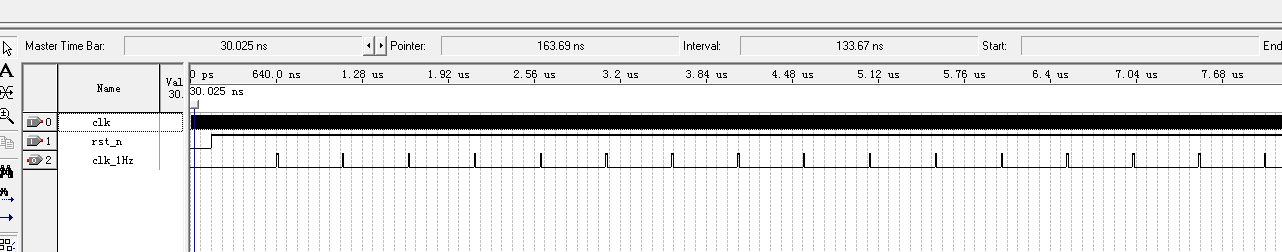

分频模块仿真图

控制模块仿真图

-

相关阅读:

交易凭什么取胜?

C/C++调用Python

ES6基础5

计算机毕业设计Java京津冀畅游网设计(源码+系统+mysql数据库+lw文档)

初始Java

VS+CUDA环境配置

多功能频率计周期/脉宽/占空比/频率测量verilog,视频/代码

ESXI存储设备已经分区,无法创建数据存储。

腾讯云助力港华能源上线“碳汭星云2.0”,推动能源行业绿色低碳转型

【LeetCode】55. 跳跃游戏

- 原文地址:https://blog.csdn.net/diaojiangxue/article/details/133281089