-

Verilog 不同编码风格对综合电路的影响

Verilog是一种硬件描述语言(HDL),用于设计数字电路和系统。统一、良好的代码编写风格,可以提高代码的可维护性和可读性。

同样的功能,不同的Verilog 编码风格也会对综合过程产生重大影响,在综合的过程中,Verilog 代码被转换为门级电路,不同的代码风格,综合出的电路可能是不同的,对应资源的占用和功耗也会有差异。

下面以一个模3计数器为例,演示3种不同写法对综合后电路的影响。

示例 #1

module cntr_mod3 ( //Inputs input clk, input rstn, //Outputs output reg [1:0] out, ); always @(posedge clk) begin if ((!rstn) | (out[1] & out[0])) out <= 0; else out <= out + 1; end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

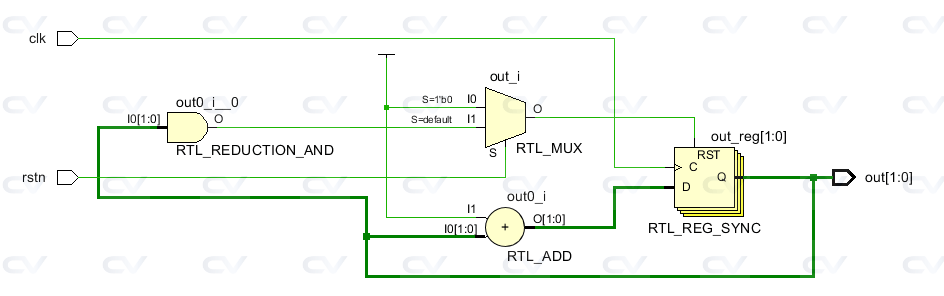

综合出的电路如下图所示,三个基本的门电路:

示例 #2

module cntr_mod3( //Inputs input clk, input rstn, //Outputs output reg [1:0] out ); always @(posedge clk) begin if (!rstn) out <= 0; else begin if (out == 3) out <= 0; else out <= out + 1; end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

综合出了两个选择器和一个加法器,相比于前一种写法将会占用更多的资源。

示例 #3

module cntr_mod3( //Inputs input clk, input rstn, //Outputs output reg [1:0] out ); always @(posedge clk) begin if (!rstn) out <= 0; else begin if (&out) out <= 0; else out <= out + 1; end end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

相比于上一个写法,少了一个选择器。

-

相关阅读:

l8-d13 UNIX域套接字

Elasticsearch从入门到精通-04ES高级语法

leetcode 剑指 Offer 21. 调整数组顺序使奇数位于偶数前面

客服快捷回复语

MySQL数据库管理基本操作(一)

ipad协议超稳定

linux U盘无法使用,提示“Partition table entries are not in disk order“

php+JavaScript实现callback跨域请求jsonp数据

回归测试怎么做?回归测试什么时候做?

ES 查询时提示:all shards failed [type=search_phase_execution_exception]

- 原文地址:https://blog.csdn.net/whik1194/article/details/133217095