-

2023年第三届HiPChips解读

The 3rd International Workshop on High Performance Chiplet and Interconnect Architectures (HiPChips)

主题

Architecture

- Chiplet-enabled architectures with emerging technologies (e.g., in-memory computing, optical computing, quantum computing, etc)

- Hardware software co-designs for chiplet architecture

- High performance computing architectures enabled by fast interconnect

- Power and performance modeling for chiplet architectures

Interconnect

- Interconnect technologies for coherent and non-coherent data sharing

- Emerging on-chip interconnect for large-scale heterogeneous computing

- Novel software optimizations and scheduling with inter-chiplet network

芯片架构议题

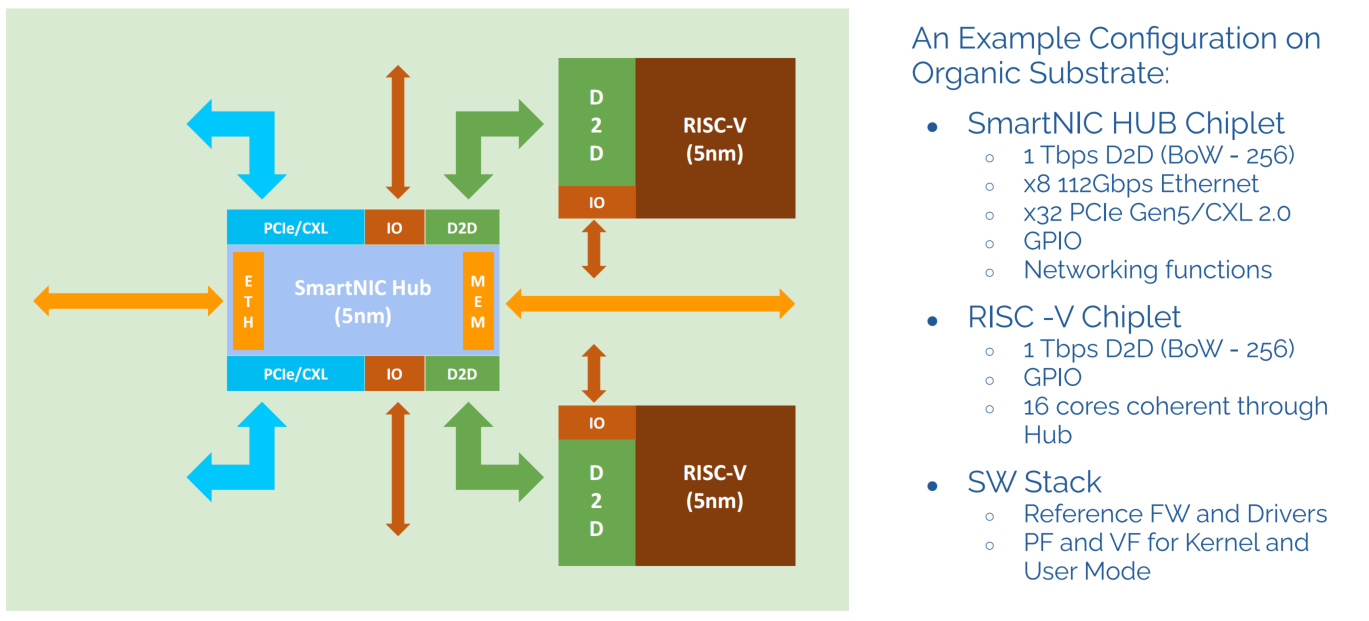

* A chiplet based SmartNIC Platform using BoW

- Speaker: Suresh Subramaniam (@ Apex semiconductor)

SmartNIC平台组件架构

以SmartNIC Hub为中心的芯片架构。

Hub chiplet将是SiP的核心

架构的优势:可规模化和扩展化

- 评

使用BoW的chiplet技术的SmartNIC平台。该报告提出了以后的chiplet芯片将会以Hub die为通信核心,并简单介绍了BoW技术,其热分布、信号质量等特性可很好的满足目标系统的需求。

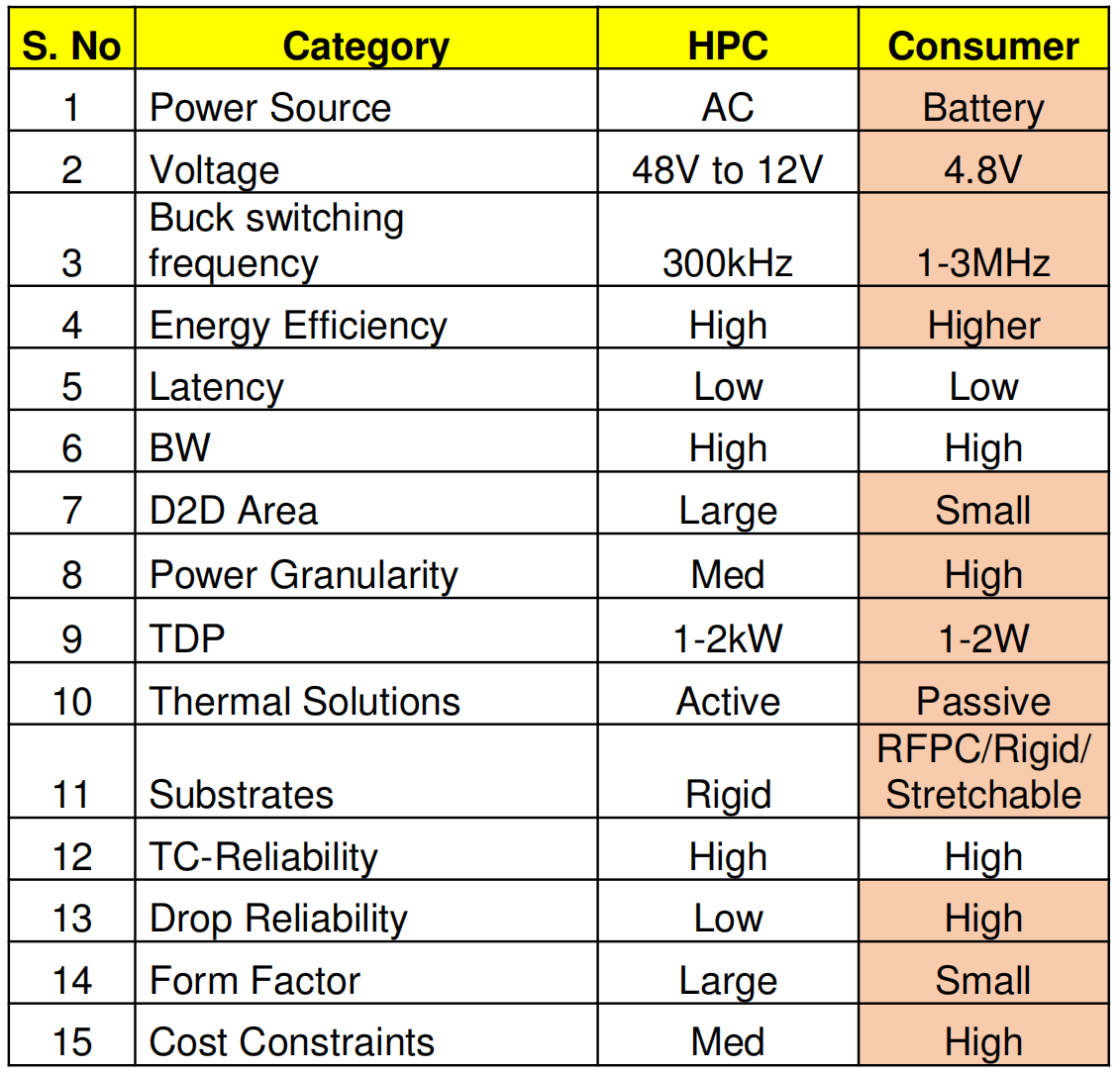

Chiplet Use Cases in Consumer Electronics (AR/VR): Opportunities and Challenges

Speaker: Sunil Gupta (Meta Confidential and Proprietary)

HPC和消费电子领域的应用区别

- HPC专注于单颗die的SoC的复杂度,以及如何使用chiplet克服光刻掩膜面积限制的硅面积

- 消费电子的chiplet应用通常是被产品外形因素驱动,以及通过改变当前组件降低成本。

AR眼镜由于外形约束采用了芯粒堆叠的封装以减小空间

封装方式: FO-PoPoP (Fan-Out PKG-on-PKG-on-PKG)

VR设备由于上市时间的需求使用了OTS SoC

OST SoC, 即 off-The-Shelf SoC,半现成的SoC。采用标准的UCIe接口的第三方或定制IP与自主设计的SoC互联,这种方法极大的缩减了芯片开发周期,减少了产品上市时间。

可穿戴设备由于高度首先使用2D/2.5D封装

- 评:

消费电子领域(AR/VR)的Chiplet使用案例:机会与挑战。该报告揭示了消费电子领域的芯片chiplet技术应用状况,根据不同产品的特征,Meta主要使用了不同封装方式将die集成,同时Meta还呼吁加快UCIe的生态建设以促进chiplet技术的应用。

Chiplets for Composable Polymorphic AI Architectures

Speaker: Weifeng Zhang (Chief Architect & VP of Software Lightelligence)

多模态的空间和时间可伸缩性

空间可伸缩性:跨领域的现有的和新兴的AI算法的发散

时间可伸缩性:跨代际的计算架构和算法进化

多模态架构的目标在于:实现与专门构建的DSA加速器相同的性能水平多模态的层次架构

关键的要素包括:异构+可组成性+可变换性

由不同颗粒度的要素组成的异构chiplet架构,这些要素包括chiplet、memory、compute unit、compute node;动态的可重配置互联包括chiplet间、chiplet内、加速器间等。

计算驱动的运行时可变换性

高并行化和高使用率的计算任务划分和映射

- 评

可组装的多模态的AI chiplet架构。

Large Scale Generative Inference Acceleration with Chiplets and In-Memory Compute

Speaker: J. Balachandran ( d-Matrix )

AI推理对计算系统的需求

用于生成式推理chiplet架构

每个chiplet的架构如图所示:

Chiplets通过BoW互联

通过BoW技术,该芯片实现了较好的可测性、较高质量的眼图。

- 评

通过Chiplets和存内计算的大规模生成式推理加速。针对AI加速的推理阶段提出了自家的chiplet芯片架构(并未详述),并展示了该芯片流片后的性能。

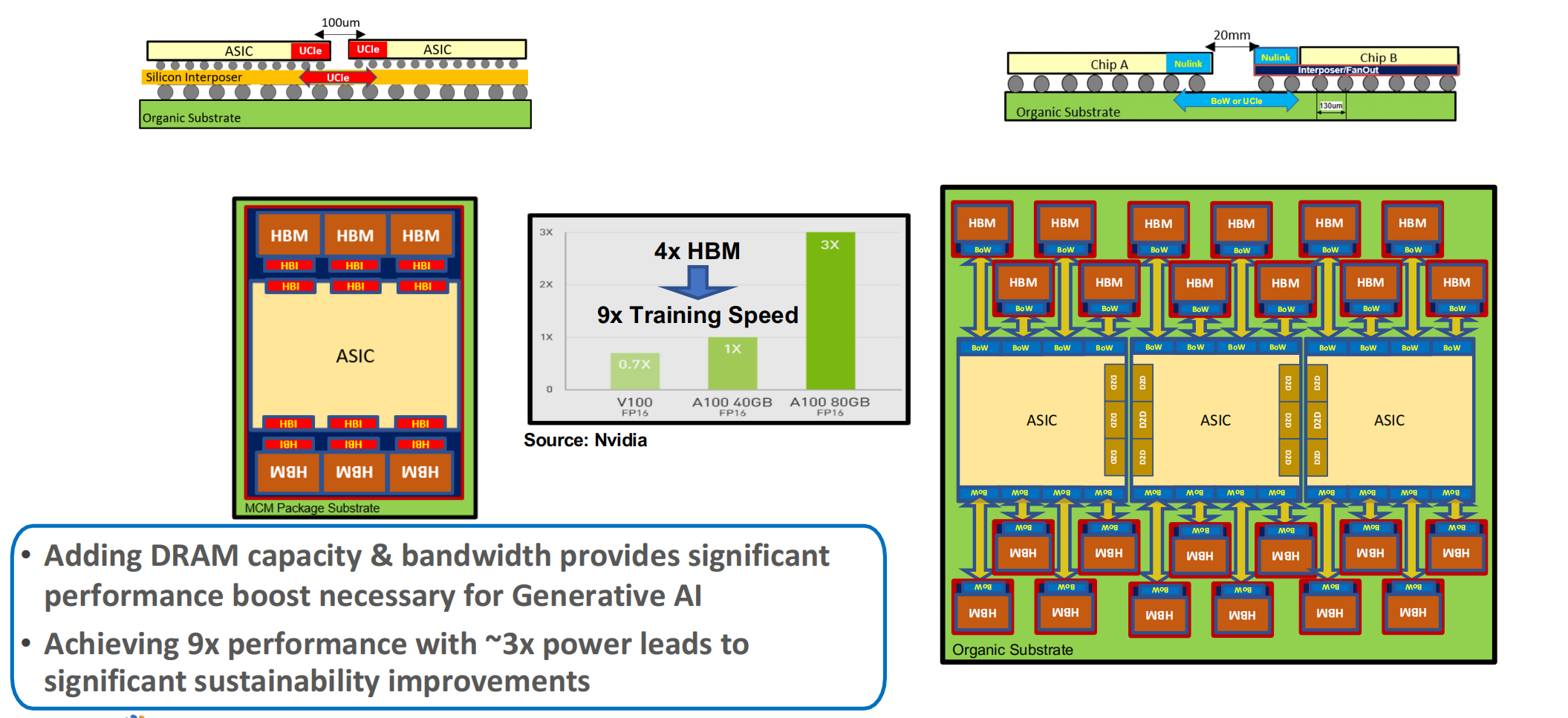

Enabling High Performance Chiplets

Speaker: Syrus Ziai, Co-Founder & VP Engineering, Eliyan

计算性能需求和限制:内存

现代高性能计算的算力需求和芯片技术的提升不匹配,面临着内存墙和带宽的限制。

构建最理想的Chiplet架构

可优化的性能,可持续性维护

每个ASIC的外部总带宽的提升

支持长线距的D2D PHY可以使能更多的ASIC的die连接接口。

构建终极的Chiplet系统

- 评

使能高性能Chiplets系统。该报告揭示了现在AI计算的对内存带宽的强大需求,而异步架构的chiplet系统可以缓解该问题,并提出了对理想chiplet架构的畅想。

CHiplet接口协议议题

Universal Chiplet Interconnect Express (UCIe)TM : An open standard approach for constructing future SoCs

- Speaker: Dr. Debendra Das Sharma (@ UCIe)

- 评

UCIe:一种用于构建未来SoC的开放标准方法。UCIe标准组织秘书长的宣传报告,讲了UCIe的基本特征和使用场景,技术细节较少。

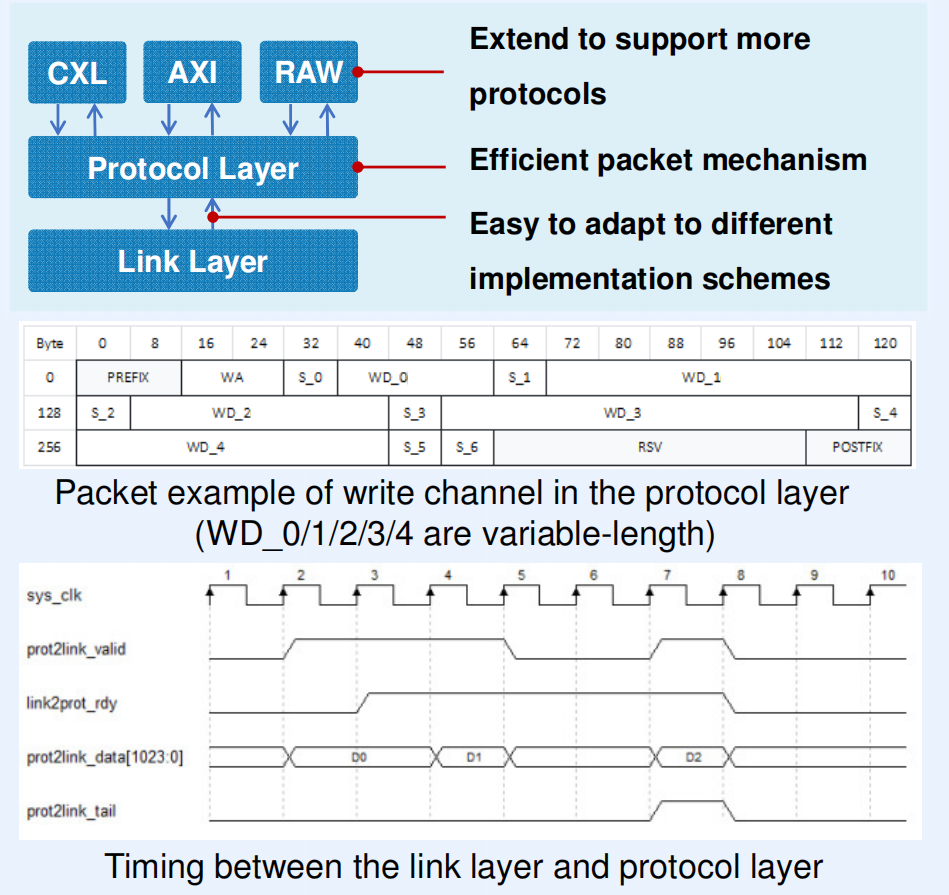

Introducing ACC 1.0: Advanced Cost-driven Chiplet Interface Standard

Speaker: Kaisheng Ma (Institute for Interdisciplinary Information Sciences, Tsinghua University)

chiplet芯片构建的挑战:划分、集成、封装

ACC1.0接口特征

- 高数据传输率

- 低延迟

- 高可靠性

- 封装友好

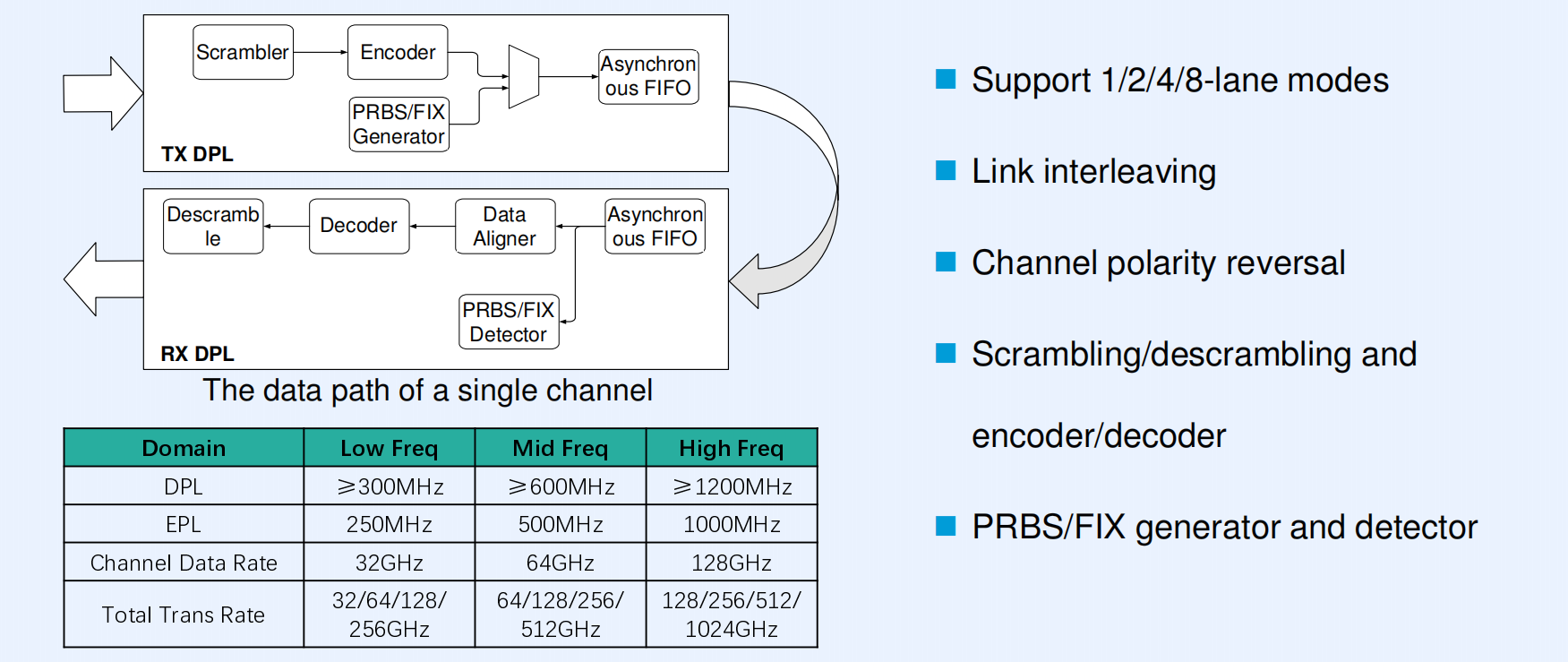

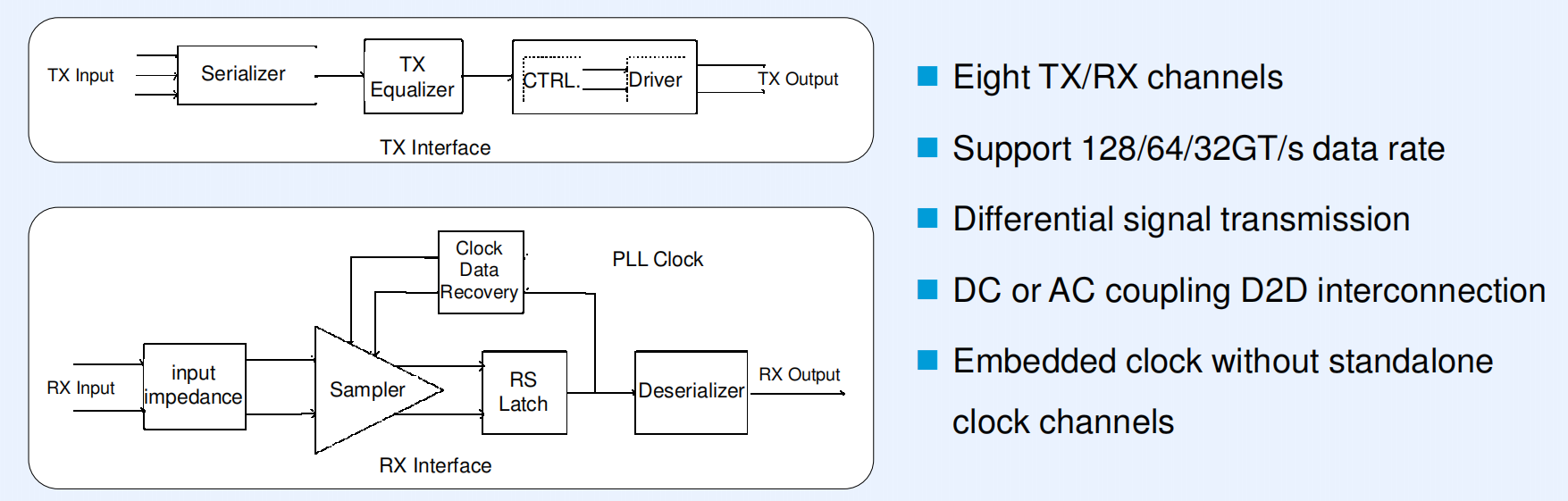

ACC1.0分层架构

协议层

- 可扩展性:支持AMBA4.0、CXL3.0 256B Flit mode和Native mode

- 灵活性:灵活的报文机制,写通道支持数据压缩

- 可兼容性:能在不同的环境场景下运行

链路层

- 可靠性: 支持CRC和ACK/NCK机制

- 易于扩展更多信息类型:数据流类型可以通过控制字符或数据字符进行编码

- 多数据传输速率:支持x1/x2/x4/x8通道模式

逻辑物理层

电气物理层

边带数据通路

- 用于寄存器读写访问

- 有数据和时钟2根信号

- 报文格式:写:64b 读:72b

支持数据安全性

不同应用场景下数据一致性维护

- 评

ACC 1.0介绍:先进的成本驱动的chiplet接口标准。该报告介绍了chiplet技术相对于monolithic的优势。

芯片封装议题

CXL-enabled systems start their roots on a die

Speaker: Siamak Tavallaei, CXL Advisor to the Board of Directors, CXL™ Consortium

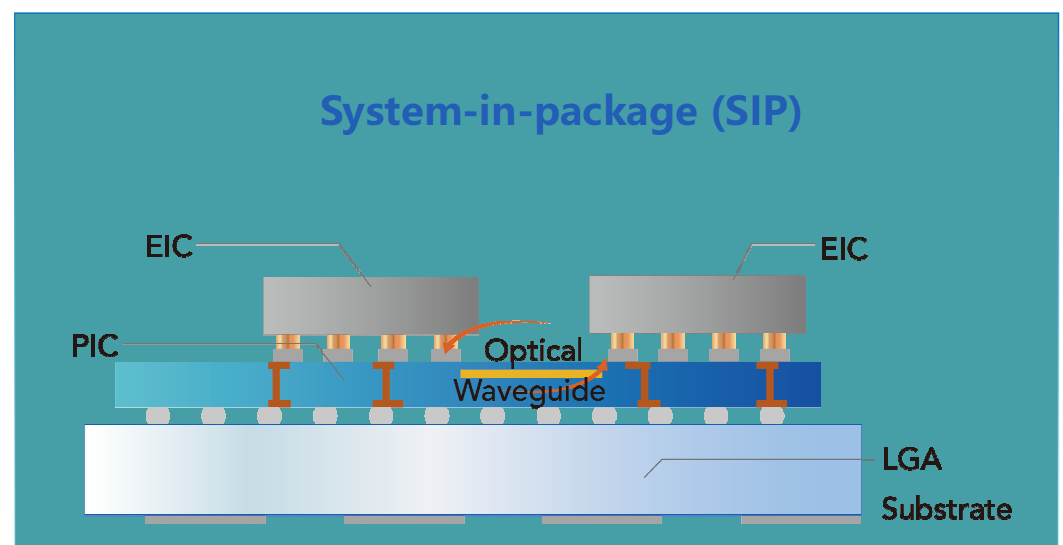

统一on-package和off-package的硅光互联技术:Optical IO

通过光介质层(Optical Interposer),使用光信号取代铜线实现chiplet间的信号互联,支持CXL、PCIe、UCIe、JEDEC(HBM)等工业界标准

OIO技术的带宽密度优势

通过OIO接口将加速器、池化内存、CXL Switch建立互联

如下图所示,是一个基于CXL协议的互联网络。chip间互联的物理层使用PCIe协议;die间互联则使用UCIe协议,封装时同样采用OIO技术;CXL设备互联构成Photonics架构,之间长距离传输通过cable进行。

SuperNova为光源模块,用于信号传输,和设备的芯片接口和switch相连。相关研究

K. Hosseini, et.al., “8 Tbps Co-Packaged FPGA and Silicon Photonics Optical IO”, OFC 2021

- 评

基于die技术生根发芽的搭载CXL的系统。先描述了CXL的应用场景、功能、技术架构、生态,再说明了chiplet技术进行各类硅组件互联的合理性,并提出了使用chiple设计时需关注的问题,并提出了统一on-package和off-package互联的解决方案Optical IO。即在on-package层,通过光介质层(Optical Interposer),使用光信号取代铜线实现chiplet间的信号传输,在off-package,使用光模块、cable等进行。

Enable Large-scale Computing with 3D Optical Chiplet Interconnect

Speaker: Huaiyu Meng, Co-founder and CTO of LIGHTELLIGENCE

晶体管的增长落后于计算需求,只能通过增加硅面积而扩大晶体管数量

基于电子通信的芯片的性能极限导致芯片性能提升失效

- 只有相邻的chiplet才能通信,电子信号在长距离下会减弱

- 远程chiplet间的跳变(鄙人理解为信号走线的转弯)导致延迟增加

- 任务分配的挑战将会导致无效的资源使用

芯粒连接的拓扑结构

基于光互联的NoC (Optical NOC, oNOC)支持更灵活的拓扑结构

如图基于光通信的片上封装:

PIC (Photonc Integrated chip)

- 评

chiplet 3D光互联促进大规模计算。 Huaiyu Meng在第二届HiPchips也进行了类似主题的报告,第三届并无太多新意,在架构层面增加了3D互联

芯片测试议题

Monitoring High Density D2D Interconnect

Speaker : Nir Sever (Senior Director of Business Development, proteanTecs)

EDA工具议题

Chiplet-package Co-design CAD tools for Hetrogenerous-System-in-Package (HeSiP)

Speaker: Yarui Peng, Assistant Professor, Computer Science and Computer Engineering, University of Arkansas

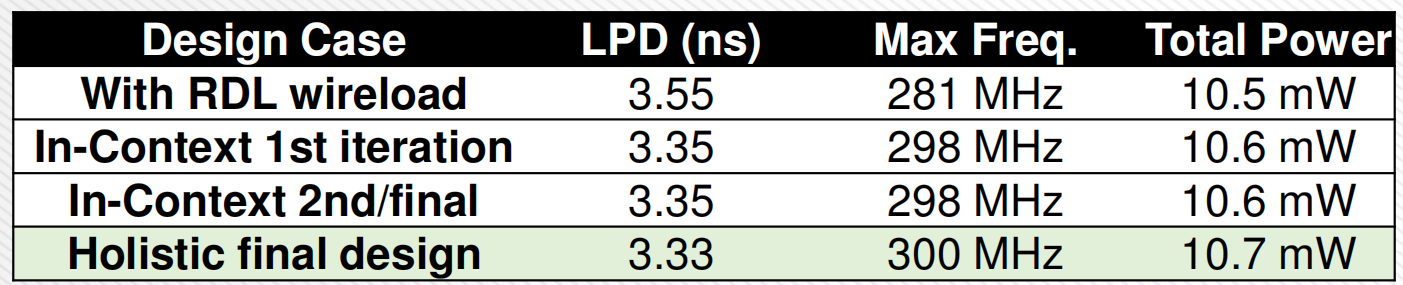

对比传统和理想的chiplet芯片设计流程

新的chiplet设计流程增加对了chiplet划分、设计封装阶段的优化和分析等。

RDL层布线策略

In-context flow: package和chiplet集成布局布线的优化策略

通常对于die内的时序优化,可以通过增加buffer的方式,而package层的时序优化由于没有晶体管,不能使用该方式,因此需要新的时序优化策略。

通过案例讲解工具执行流程

芯片系统架构和划分,设计团队将该MCU划分成core chiplet和8KB的memory chiplet。

制程:TSMC 65nm

封装:TSMC 2.5D InFO

完成package(RDL)和chiplet设计后,所有部件将会组合封装,同时工具将会收集RDL对chiplet设计影响的信息,并进行分析和优化。

设计团队为了对比研究,设计了2D封装和2.5D封装,结果发现,由于RDL布线的影响,2.5D封装设计的系统最高频率只有245MHz,而同设计的2D封装设计可以达到333MHz,为了提醒2.5D设计的性能,设计团队使用该工具的In-context flow进行多次迭代分析优化。

分析发现,导致频率变低的关键路径在于两个chiplet之间,考虑到单core-chiplet的最高系统频率可以达到300MHz,因此采用为每个chiplet创建扩展布线区,通过工具提取两区域特征,弥补SPEFs,最后进行时序创建。

通过这种 In-context flow的方式,经过多次迭代,系统获得了较好的性能。

PowerSynth2

相关研究

- Md. Arafat Kabir, Yarui Peng, “Chiplet-Package Co-Design For 2.5D Systems Using Standard ASIC CAD Tools”, in Proc. Asia and South Pacific Design Automation Conference, pp. 351-356, Jan 2020.

- Md. Arafat Kabir, Dusan Petranovic, and Yarui Peng, “Extraction and Optimization for Heterogeneous 2.5D ChipletPackage Co-Design”, in Proc. International Conference on Computer-Aided Design, 2020 Nov.

- Md. Arafat Kabir, Weishiun Hung, Tsung-Yi Ho, and Yarui Peng, “Holistic and In-Context Design Flow for 2.5D Chiplet-Package Interaction Co-Optimization”, in Proc. International Symposium on VLSI Design, Automation and Test, pp. 1-4, 2021, Invited Paper.

- Md. Arafat Kabir, Dusan Petranovic, and Yarui Peng, “Extraction and Optimization for Heterogeneous 2.5D Chiplet-Package Co-Design”, in Proc. International Conference on Computer-Aided Design, 2020 Nov.

- Md. Arafat Kabir, and Yarui Peng, “Holistic Chiplet-Package Co-Optimization for Agile Custom 2.5D Design”, IEEE Transactions on Components, Packaging, and Manufacturing Technology, vol. 11, no. 5, pp. 715-726, 2021

- Md. Arafat Kabir, and Yarui Peng, “Holistic 2.5D Chiplet Design Flow: A 65nm Shared-Block Microcontroller Case

Study”, in Proc. IEEE International System-on-Chip Conference, 2020 Sep. - Imam Al Razi, Quang Le, Tristan Evans, H. Alan Mantooth, and Yarui Peng, “PowerSynth 2: Physical Design Automation for High-Density 3D Multi-Chip Power Modules”, IEEE Transactions on Power Electronics, vol. 38, no. 4, pp. 4698-4713, 2023

- 评

用于异构封装系统的chiplet封装设计联合的CAD工具。本文提出了一个应用于package和chiplet集成封装的EDA工具,该工具可以进行interposer层的布局布线,对chiplet和package集成后的布局布线优化提出了新的策略,并且该工具有一定的灵活度和可扩展性。

芯片攻击与保护

Chiplet Security Threat Analysis

Speaker: Durgesh Srivastava, Darren Lasko (Nvidia)

封装保护的要点

- 设备秘密

- 固件权限/完整度/隔离

- 专有知识产权(Proprietary IP)

- 当前已有的缓解措施

- 保密计算,包括代码和数据的保密性和完整性保护

常见的威胁

- 基本硬件攻击

- 错误注入攻击(glitch攻击、低压模拟等)

- DFD/DFT攻击

- 先进硬件攻击

- 物理通道访问

- 解码类型

- 错误修正类型

- 封装内互联通道的边带信号攻击

- SW attacks against shared buses

- chiplet供应链攻击,封装前,包括chiplet供应商、集成商等安全隐患

需要一个通用解决方案

- 构建一个“安全岛”隔离DFT和其他攻击加固终端设备(RoT/Trust Anchors)安全属性

- Turst Anchors可以直接访问DFT和本地chiplet的状态,并通过加密的方式发送给RoT。

- 评

chiplet安全威胁分析。知识储备有限,表示没咋看懂,大致描述的是芯片安全保护的问题。

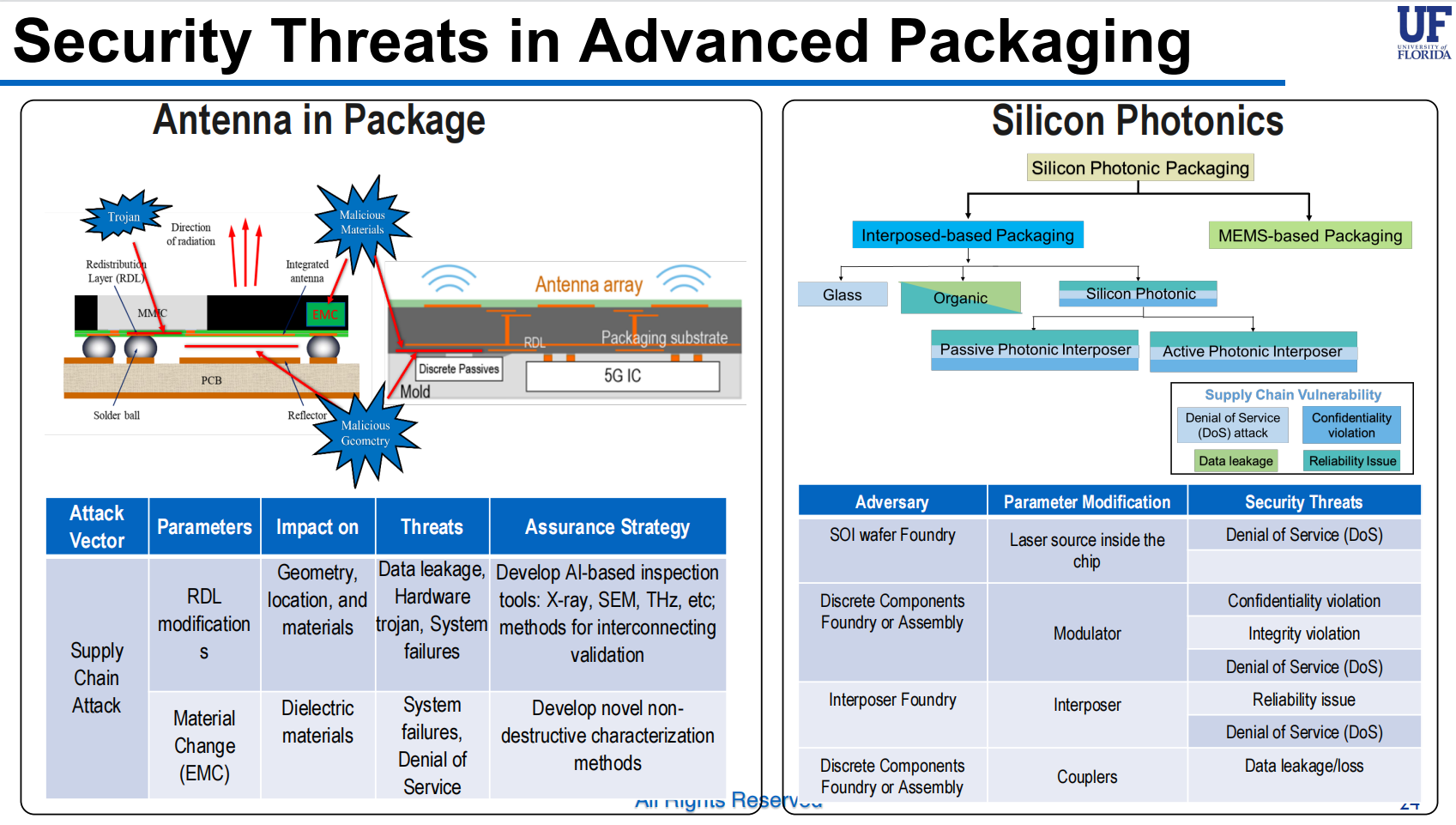

Physical Assurance of Microelectronics From Chiplets to Systems

Speaker: Navid Asadi (Assistant Professor, Director, Security and Assurance lab)

芯片多样的检测方法成为芯片攻击的重要手段

芯片物理保护的角度和手段

chiplet 可重配置的interposer实现芯片保护

从板级系统角度确保物理安全

- 评

从Chiplet层级到系统层的微电子物理安全保护问题。本文探讨了芯片的物理安全保护问题,现代芯片面临这间谍破解、电磁破环等安全问题,该报告就chiplet架构芯片的interposer层、先进分装角度提出了几种防破解的方案,同时在PCB层级的系统层也提出了几种方案。

量子计算芯片

Modular, Distributed, and Hybrid Systems with Quantum Chiplets

Speaker: Fred Chong (Seymour Goodman Professor, University of Chicago Chief Scientist for Quantum Software, Infleqtion)

量子计算将重构世界的诸多领域

相关研究

- Gold, A., Paquette, J.P., Stockklauser, A. et al. Entanglement across separate silicon dies in a modular superconducting qubit device. npj Quantum Inf 7, 142 (2021). https://doi.org/10.1038/s41534-021-00484-1

- 评

基于量子Chiplet的模块化、分布式、混合系统。报告内容没看明白~

其他参考

共封装光学CPO目前发展怎样?

OFC 2021: Ayar Labs实现1Tbps无差错的光芯片间信号互联

北极熊芯创始人马恺声参加ISCA-HiPChips研讨会介绍ACC标准 -

相关阅读:

Windows命令行窗口修改字体方法

代码随想录算法训练营第六十天| 739.每日温度 、496.下一个更大元素 I

spring boot整合mybatis,mybatis generator ,自定义typhandler

为什么重度研发难以短、平、快?以3D引擎研发为例

Shopify Theme 开发 —— 性能优化

服务注册发现_搭建单机Eureka注册中心

Polygon zkEVM zkASM 与 以太坊虚拟机opcode 对应集合

堆--数据流中第K大元素

【前端设计模式】之桥接模式

瑞_Redis_商户查询缓存_添加Redis缓存&缓存更新策略

- 原文地址:https://blog.csdn.net/qq_39815222/article/details/132882842