-

去耦电路设计应用指南(一)MCU去耦设计介绍

参考资料来自网上:

1. 概述

我们经常看到单片机或者IC电路管脚常常会放置一个或者多个陶瓷电容,他们主要是为了增强 MCU 电源的电源完整性 PI,降低 PDN阻抗,提高 MCU 的对于噪声的抗扰度,降低 MCU 对外辐射的 EMI。

后面我们简单了解一下去耦电路器件包含狭义上的旁路电容、去耦电容、磁珠电感、以及 LC/PI 滤波器等,了解如何选择合适的器件来搭建高性能去耦电路,提高电路的 PI/SI/EMC 特性。

2. MCU需要去耦的原因

2.1 去耦电路简介

供电电源与 MCU 之间的连接使用了各类电容以及磁珠电感等滤波器件,形成的去耦电路 有三点主要功能,

一是抑制 MCU 内部产生的 EMI 辐射或者疏导外部干扰噪声进入 MCU;

二是提供 MCU 操作和维持电压的瞬态电流;

三是作为信号回流的通道提高信号完整性。当 MCU 系统级板上的去耦电路不起作用时会出现一下问题:

干扰噪声从外部导入,MCU收到其他的IC的噪声干扰,操作故障;

存在噪声泄露,MCU中的EMI辐射超标;

电源电压波动干扰MCU操作,降低信号完整性,信号线上的噪声叠加; 信号线上回流路径较长,信号完整性降低。2.2 电源噪声产生的原因

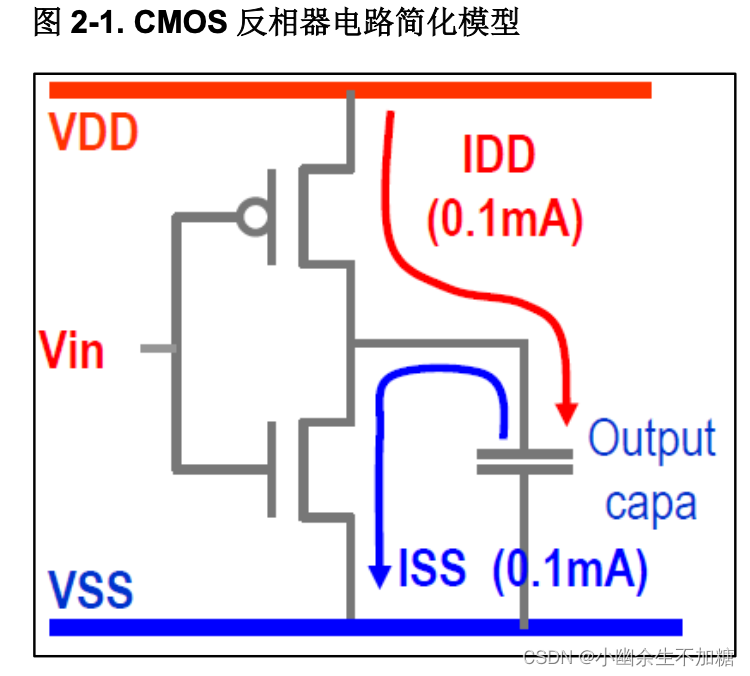

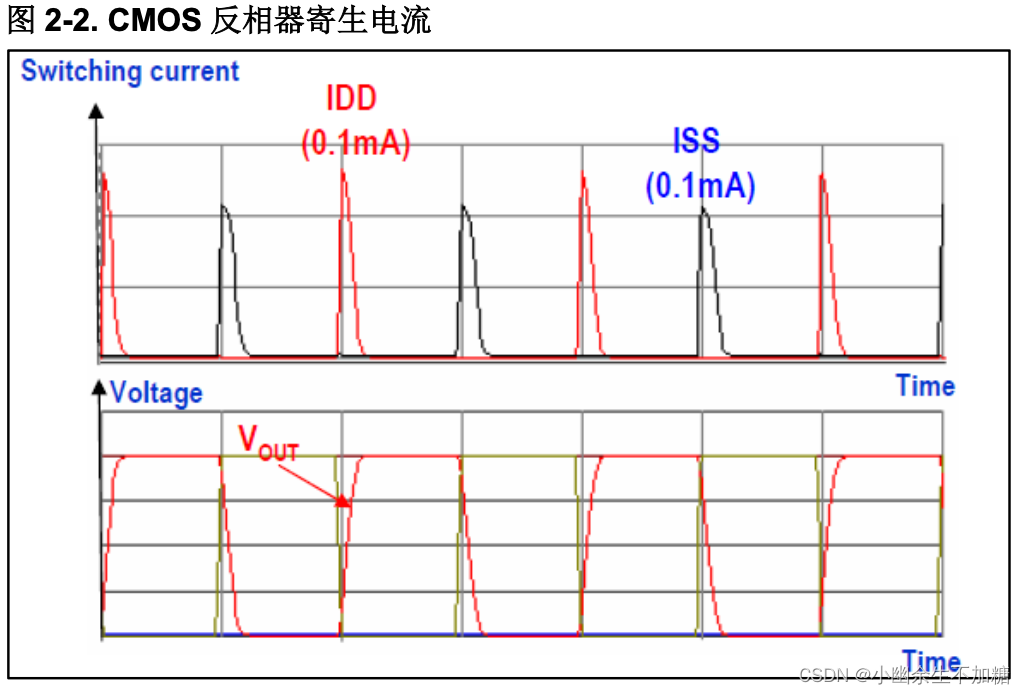

数字IC如MCU大多数使用电路CMOS工艺,通过切换至电源VDD或者接地GND可以 将信号设置为高“1”或低“0”。如图 CMOS 反相器电路简化模型 ,以单个 CMOS 的反相器为例,当 Vin 切换低“0”,上管 PMOS 导通,栅电容充电,Vout 输出高“1”; 当 Vin 切换高“1”,下管 NMOS 导通,栅电容放电,Vout 输出低“0”。当时 CMOS 反相 器高低切换电平时,寄生电流会流经电源 VDD 和接地 GND 如图 2-2. CMOS 反相器寄生 电流,MCU 内部的 CMOS 反相器较多时,寄生电流跳动的非常激烈,很多频率器件如电感,会向外辐射能量造成噪声故障,或者引起外部电源的波动影响其他的 IC。

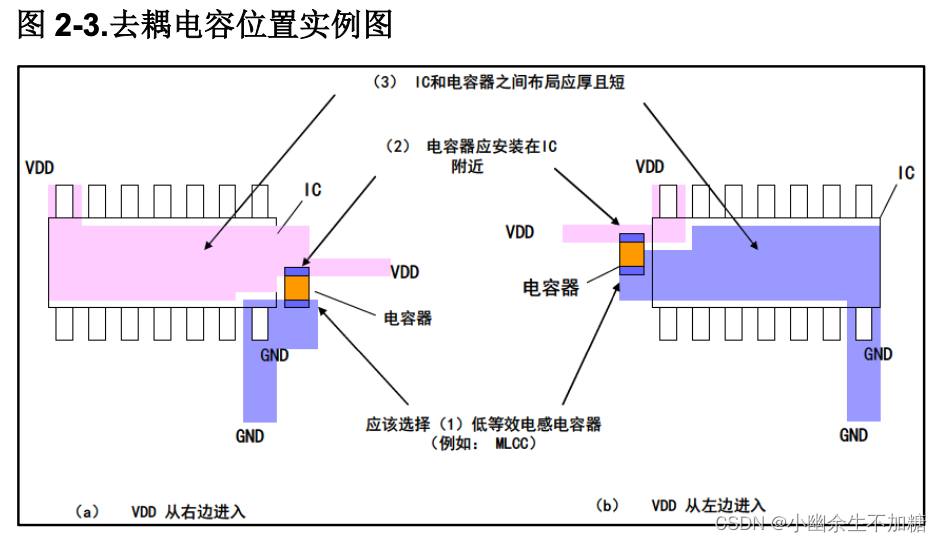

通常为了控制流经 MCU 电源处的电流,需要在 MCU 的电源引脚和 GND 引脚之间安装 去耦电容,为了形成有效去耦电路,需要主要一下加点:

使用较小的ESR电容,形容可以在高频范围内运行的旁路;

严格限制寄生电流流过的范围,将电容安装在MCU附近;

保持layout的寄生电感较小,尤其IC和电容之间。

2.3 插入损耗

通常滤波器使用插入损耗 IL 来表示对噪声的过滤性能,由于电源的去耦电路也是滤波器的一种,所以其抑制噪声性能可以用插入损耗来表示。

插入损耗 IL 用安装在阻抗为 50Ω 的电路中的滤波器效果来描述,为安装滤波器前后的输 出电压之差,以 dB 为单位。插入损耗越大,静噪效果越好。插入损耗可能由 50Ω 系统的 S 参数的传输系数 S21 的绝对值来代替。如图

2.4 去耦电路简介

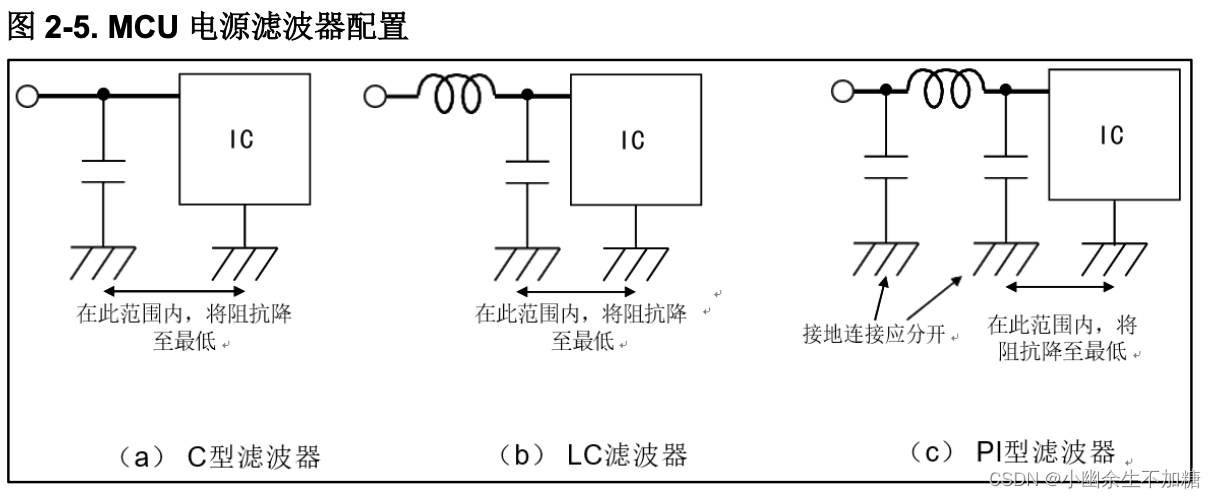

旁路电容作为 C 型滤波器(去耦电容)的应用领域较广, C 型滤波器随着电容的阻抗的 减小,插入损耗 IL 就会增加。电容阻抗与频率成反比成为低通滤波器,理想情况下,频率 越高插入损耗越大。

除了 C 型还有 LC 型以及 PI 型滤波器,在 C 型滤波器基础上再在 MCU 远端电源线上串 一个电感/磁珠就成为 LC 滤波器,在 LC 滤波器基础上再远端在并一个电容就是 PI 型滤 波。如图:

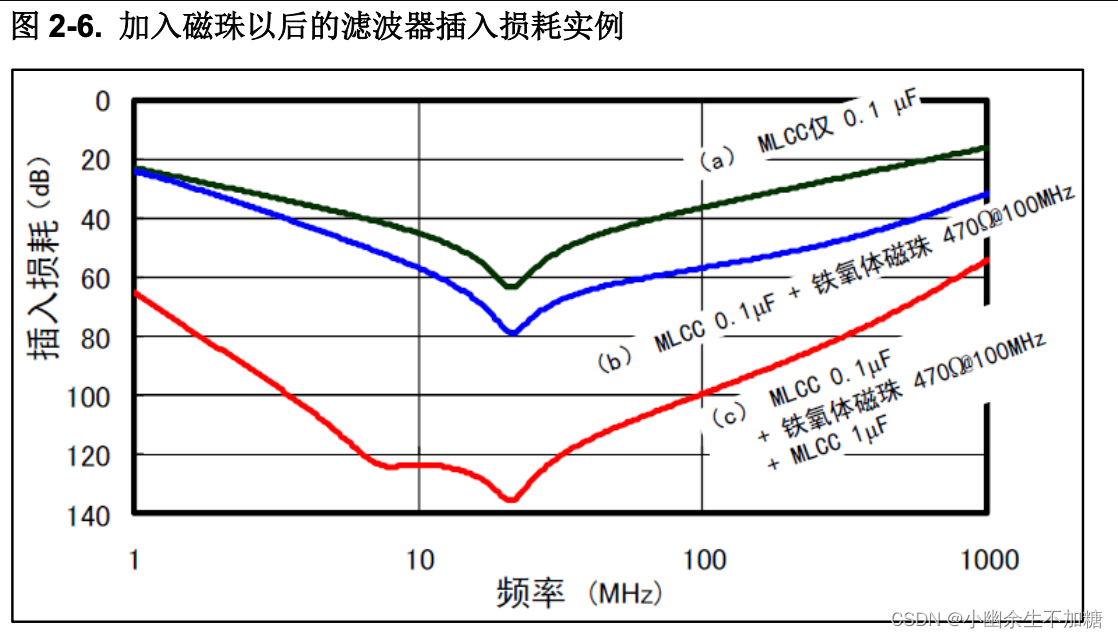

当电容器和电感器结合,如图 2-5 MCU 电源滤波器配置(b)和©所示,与只使用电 容器相比,插入损耗特性曲线斜度会更陡。因为在衰减区,插入损耗会同时增加,当噪声 需要大大削弱时,这种方法更为有用。如图 2-6. 加入磁珠以后的滤波器插入损耗实例显 示当加入电感器后,插入损耗的变化实例。

由于 MCU 的 GND 引脚与最近的电容 GND 成为噪声返回路径,所以尽量缩短两者距离来 降低阻抗,当 CLC-PI 型滤波器 layout 时,两侧电容最好走之字使电容 GND 通过 VIA 分 开。因为 PI 型和 LC 滤波对于干扰噪声具有较大的插入损耗,所以在抗干扰 EMS 防护 MCU 时,组合去耦电路的应对强干扰的效果更好。

-

相关阅读:

Windows&Linux文件传输方式总结

RabbitMQ延迟消息:死信队列 | 延迟插件 | 二合一用法+踩坑手记+最佳使用心得

4、【创业必备企业架构,可开发任意项目】SpringCloud大型企业分布式微服务云架构源码之MySQL 连接

Facade 外观模式简介与 C# 示例【结构型5】【设计模式来了_10】

【Typroa使用】Typroa+PicGo-Core(command line)+gitee免费图片上传配置

java 商机管理系统Myeclipse开发mysql数据库web结构jsp编程计算机网页项目

app专项测试:app弱网测试

【饭谈】公司里偷偷学习专业技术,到底是否合理?

一次做数据报表的踩坑经历,让我领略了数据同步增量和全量的区别

IPT2602协议-USB 快速充电端口控制器

- 原文地址:https://blog.csdn.net/qq_41600018/article/details/132920077