-

详解SPI

引言

串行外设接口(Serial Peripheral Interface,简称SPI)是一种常见且广泛应用于电子系统中的通信协议。作为一种高效可靠的串行通信技术,SPI总线在电气工程和计算机系统领域扮演着至关重要的角色。它不仅在微控制器和外设之间实现快速数据传输,还在许多嵌入式系统和通信设备中发挥着重要作用。

本文将深入探讨SPI总线的基本原理和工作机制,介绍其在数据传输中的优势和特点。无论是用于连接存储器芯片、传感器、显示器还是其他外围设备,SPI总线都展现出了其高速、可靠和简单的硬件实现的特点。

无论是对电气工程师、嵌入式系统开发者还是通信技术爱好者,深入理解SPI的工作原理都是非常必要的。

SPI基础知识

SPI是一种全双工、同步的通信协议,常用于微控制器和外设之间快速、可靠的数据传输。SPI总线的灵活性和高效性使得它成为许多嵌入式系统和通信设备的首选通信接口。

SPI工作原理

SPI总线通常由一个主设备(Master)和一个或多个从设备(Slave)组成。主设备负责控制通信,从设备接受主设备的指令并提供数据响应。SPI总线通过四根线进行通信:

- SCLK(Serial Clock):时钟信号由主设备产生,用于同步数据传输速率。

- MOSI(Master Out Slave In):主设备输出数据,从设备输入数据。

- MISO(Master In Slave Out):从设备输出数据,主设备输入数据。

- SS(Slave Select):主设备通过选通特定从设备,使其处于活动状态。

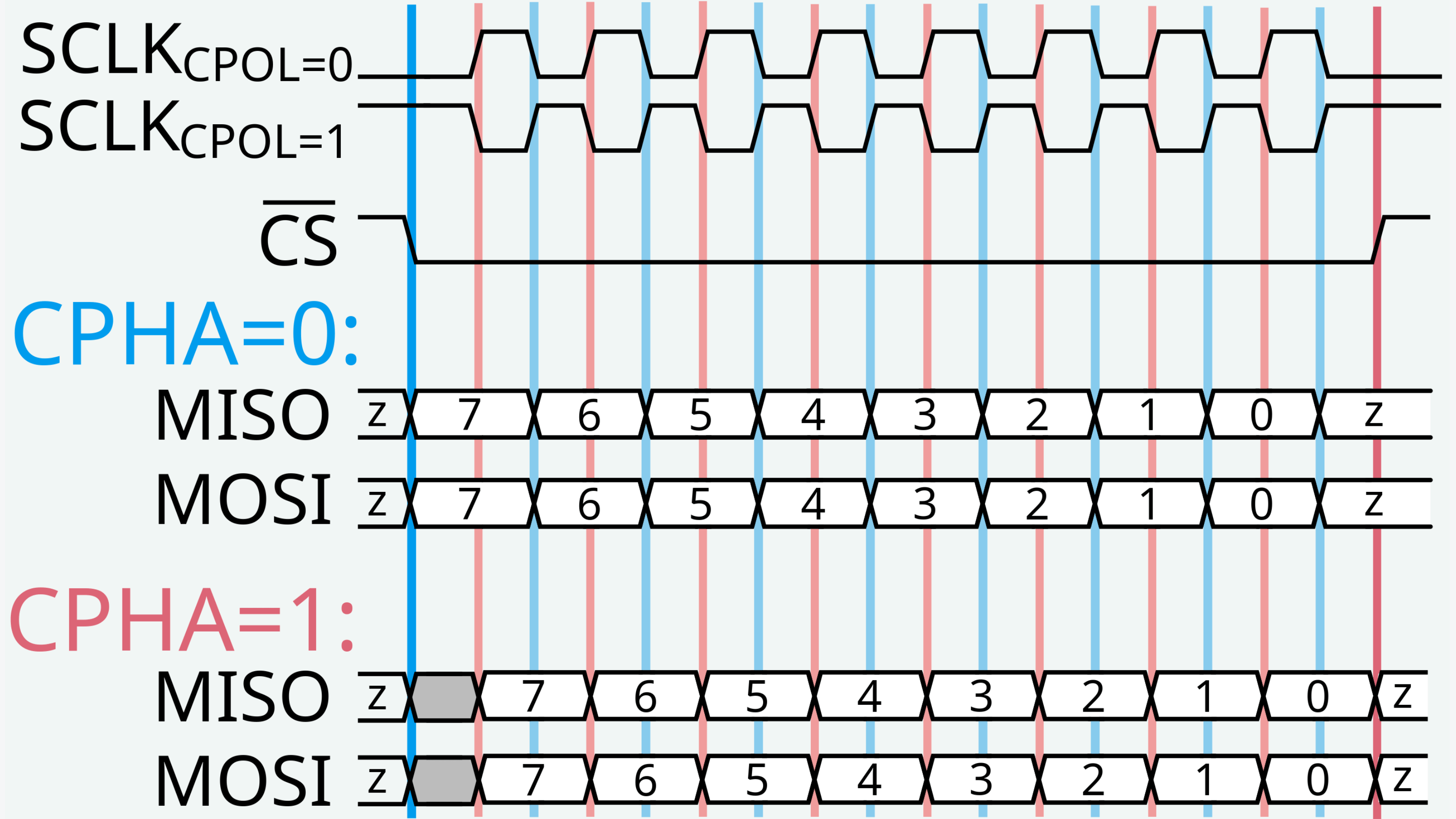

SPI工作模式

SPI(Serial Peripheral Interface)是一种串行外设接口协议,支持多种工作模式,可以根据应用的需要选择合适的模式。SPI总线的工作模式由时钟相位(Clock Phase)和时钟极性(Clock Polarity)组合而成,通常用CPOL和CPHA两个参数来表示。常见的SPI工作模式有四种,分别是模式0、模式1、模式2和模式3。

模式0

- CPOL = 0(时钟空闲状态为低电平)

- CPHA = 0(数据采样在时钟的上升沿,数据输出在时钟的下降沿)

在模式0下,时钟处于空闲状态时为低电平,数据在时钟的上升沿进行采样,数据输出则在时钟的下降沿。这种模式适用于许多SPI设备,是最常见的工作模式。

模式1

- CPOL = 0(时钟空闲状态为低电平)

- CPHA = 1(数据采样在时钟的下降沿,数据输出在时钟的上升沿)

在模式1下,时钟处于空闲状态时为低电平,数据在时钟的下降沿进行采样,数据输出则在时钟的上升沿。模式1与模式0相比,数据采样和输出的时钟边沿相反。

模式2

- CPOL = 1(时钟空闲状态为高电平)

- CPHA = 0(数据采样在时钟的下降沿,数据输出在时钟的上升沿)

在模式2下,时钟处于空闲状态时为高电平,数据在时钟的下降沿进行采样,数据输出则在时钟的上升沿。模式2与模式0相比,时钟空闲状态相反,数据采样和输出的时钟边沿也相反。

模式3

- CPOL = 1(时钟空闲状态为高电平)

- CPHA = 1(数据采样在时钟的上升沿,数据输出在时钟的下降沿)

在模式3下,时钟处于空闲状态时为高电平,数据在时钟的上升沿进行采样,数据输出则在时钟的下降沿。模式3与模式0相比,时钟空闲状态相反。

SPI工作模式表:

SPI mode Clock polarity (CPOL) Clock phase (CPHA) Data is shifted out on Data is sampled on 0 0 0 falling SCLK, and when CS activates rising SCLK 1 0 1 rising SCLK falling SCLK 2 1 0 rising SCLK, and when CS activates falling SCLK 3 1 1 falling SCLK rising SCLK

选择适合的SPI工作模式取决于具体的硬件设备和通信需求。在设计中,需要根据从设备的要求和主设备的特性来选择合适的CPOL和CPHA参数,以确保通信的正确和稳定。根据应用的不同,SPI总线可以通过简单的设置调整工作模式,从而实现灵活、高效的数据传输。

SPI通信流程

SPI通信由主设备发起,大致流程如下:

- 主设备选通一个或多个从设备,将SS线拉低,以确定通信目标。

- 主设备通过SCLK线产生时钟信号,驱动数据在MOSI上发送给从设备。

- 从设备根据时钟信号,在MISO上将响应数据返回给主设备。

- 通信完成后,主设备将SS线拉高,释放从设备。

SPI总线的优势

SPI总线具有许多优点,使其在通信领域脱颖而出:

- 高速传输:SPI总线可以实现高速的数据传输,适用于对通信速率要求较高的应用。

- 简单硬件实现:SPI总线只需几根线就能实现通信,简化了硬件设计。

- 全双工通信:主从设备可以同时进行数据的发送和接收,提高通信效率。

- 灵活性:SPI总线支持多种工作模式,适应不同应用的需求。

对比

下面是SPI、I2C和UART三种通信总线的比较表格:

特点 SPI I2C UART 通信速率 高,可达几十MHz或更高 较低,通常在几百Kbps 介于SPI和I2C之间 连接方式 4根信号线 2根信号线 2根信号线 通信模式 全双工 半双工 半双工 设备支持 用于连接多种外设 主要用于连接低速外设 通常用于点对点连接 电缆长度 有限制,通常在几米内 有限制,通常较短 有限制,通常较短 硬件复杂度 相对简单 较低 相对简单 适用场景 高速数据传输 连接多个低速外设 点对点通信和简单串口通信 UART物理层上可以同时收发,即实现全双工通信,但实际应用中通常采用“问-答”形式,所以一般认为是半双工的。

根据不同的应用需求,选择适合的通信总线可以帮助简化系统设计并提高通信效率。SPI适用于高速数据传输和连接多种外设的场景,I2C适用于连接多个低速外设的场景,而UART适用于点对点通信和简单的串口通信。在实际应用中,开发人员需要根据具体的系统需求和设备支持来做出选择。

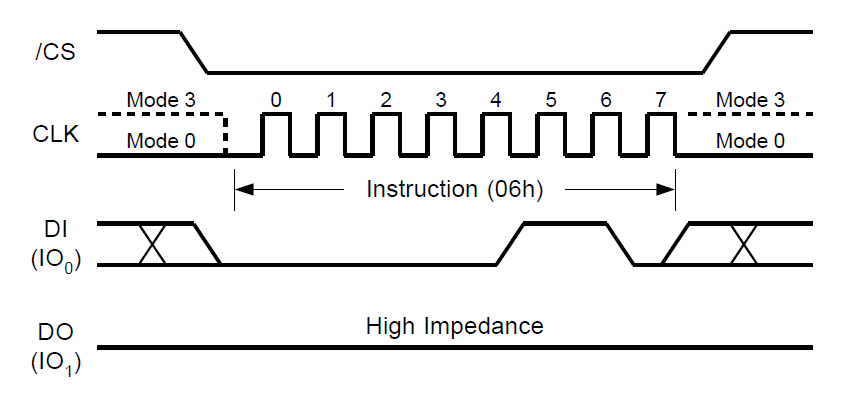

SPI Flash示例

以W25Q32FV的写使能指令

06h为例,W25Q32FV的SPI接口支持模式0和模式3,写使能指令在状态寄存器中将写使能锁存器(WEL)位设置为1。在每一个页编程、四页编程、扇区擦除、块擦除、芯片擦除、写状态寄存器和擦除/编程安全寄存器指令之前,都必须设置WEL位。写使能指令通过拉低/CS,将指令代码06h在CLK的上升沿输入到数据输入(DI)引脚,然后将/CS拉高来进入。

公众号 | FunIO

微信搜一搜 “funio”,发现更多精彩内容。

个人博客 | blog.boringhex.top -

相关阅读:

C/C++后端开发学习路线总结(附带实习学习经历分享)

Linux常用命令大全

前端面试-html、css

OpenGL实现GPU体渲染

你知道如何科学的学习吗?-关于个人成长的思考

【AI语言大模型】文心一言功能使用介绍

A. Grasshopper on a Line

前端国内镜像环境安装网址

steam搬砖项目月入过万靠谱吗

数据结构之索引查找(分块查找)

- 原文地址:https://blog.csdn.net/PengWon/article/details/132869866