-

FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB

FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB

仿真模块SIM_uart_drive_TB,仿真实现。

vivado联合modelsim进行仿真。

一、SIM_uart_drive_TB仿真代码

`timescale 1ns / 1ns //时间单位/时间精度 // // Company: // Engineer: // // Create Date: 2023/09/12 14:52:47 // Design Name: // Module Name: SIM_uart_drive_TB // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module SIM_uart_drive_TB(); /****仿真语法、产生时钟与复位****/ localparam CLK_PERIOD = 20 ; reg clk,rst; initial begin //过程语句,只在仿真里可以使用,不可综合 rst = 1; //上电开始复位 #100; //延时100ns @(posedge clk) rst = 0; //上电复位释放 end always begin//过程语句,只在仿真里可以使用,不可综合 clk = 0; #(CLK_PERIOD/2); clk = 1; #(CLK_PERIOD/2); end localparam P_USER_DATA_WIDTH = 8; reg [P_USER_DATA_WIDTH - 1 : 0] r_user_tx_data ; reg r_user_tx_valid ; wire w_user_tx_ready ; wire [P_USER_DATA_WIDTH - 1 : 0] w_user_rx_data ; wire w_user_rx_valid ; wire w_user_active ; wire w_user_clk ; wire w_user_rst ; assign w_user_active = r_user_tx_valid & w_user_tx_ready; uart_drive#( .P_SYSTEM_CLK (50_000_000 ), //输入时钟频率 .P_UART_BUADRATE (9600 ), //波特率 .P_UART_DATA_WIDTH (P_USER_DATA_WIDTH ), //数据宽度 .P_UART_STOP_WIDTH (1 ), //1或者2 .P_UART_CHECK (2 ) //None=0 Odd-1 Even-2 ) uart_drive_u0 ( .i_clk (clk), .i_rst (rst), .i_uart_rx (o_uart_tx ), .o_uart_tx (o_uart_tx ), .i_user_tx_data (r_user_tx_data ), .i_user_tx_valid (r_user_tx_valid ), .o_user_tx_ready (w_user_tx_ready ), .o_user_rx_data (w_user_rx_data ), .o_user_rx_valid (w_user_rx_valid ), .o_user_clk (w_user_clk ) , .o_user_rst (w_user_rst ) ); /****激励信号****/ always@(posedge w_user_clk,posedge w_user_rst) begin if(w_user_rst) r_user_tx_data <= 'd0; else if(w_user_active) r_user_tx_data <= r_user_tx_data + 1; else r_user_tx_data <= r_user_tx_data; end always@(posedge w_user_clk,posedge w_user_rst) begin if(w_user_rst) r_user_tx_valid <= 'd0; else if(w_user_active) r_user_tx_valid <= 'd0; else if(w_user_tx_ready) r_user_tx_valid <= 'd1; else r_user_tx_valid <= r_user_tx_valid; end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

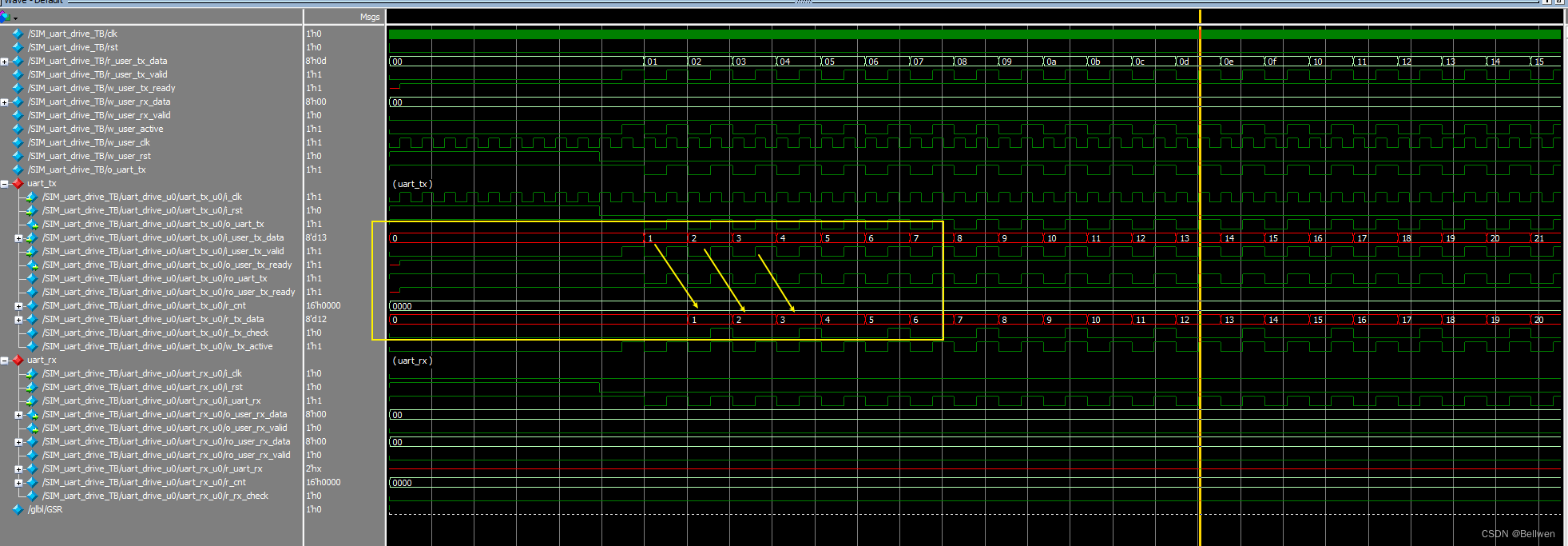

二、仿真结果

总结

还得练,要熟练使用modelsim进行仿真,因为比vivado快。

要会写仿真代码文件,继续多练。

结合协议时序实现UART收发器也算完结了。 -

相关阅读:

Spring-Spring之事务底层源码解析

快来了解一下5个超实用的WPS表格操作技巧!

LeetCodeTop100(一)

CSS三大定位方式(浮动、定位、弹性盒)详细解析

Camera1 源码解析系列(二)—— Camera1 Open() 流程解析

ConcurrentHashMap put和扩容的源码深度解析(内含JDK8中3个bug以及修复的版本)

Slash --- 字符串DP

django-rest-framework 基础二 序列化器和路由

day17-Servlet06

堡垒机的相关介绍

- 原文地址:https://blog.csdn.net/Bellwen/article/details/132839304