一、实验目的

- 掌握Vivado集成开发环境

- 掌握Verilog语言基本知识、

- 掌握并理解算术逻辑单元ALU的原理和设计

二、实验预习

1.ALU(算术逻辑单元)的16种运算的编码

三、模块接口设计

ALU的信号说明如下:

- 定义四个输入信号A、B、Cin、Card。其中,A、B为32位运算数,Card为5位运算操作码,Cin为进位。

- 定义三个输出信号F,Cout,Zero,其中F为运算结果,Cout为结果进位,Zero为零标志。

- 要求根据16种运算操作对运算操作码Card进行编码,并实现这16种运算操作。

四、实验设计

设计代码

仿真代码

五、测试结果及实验分析

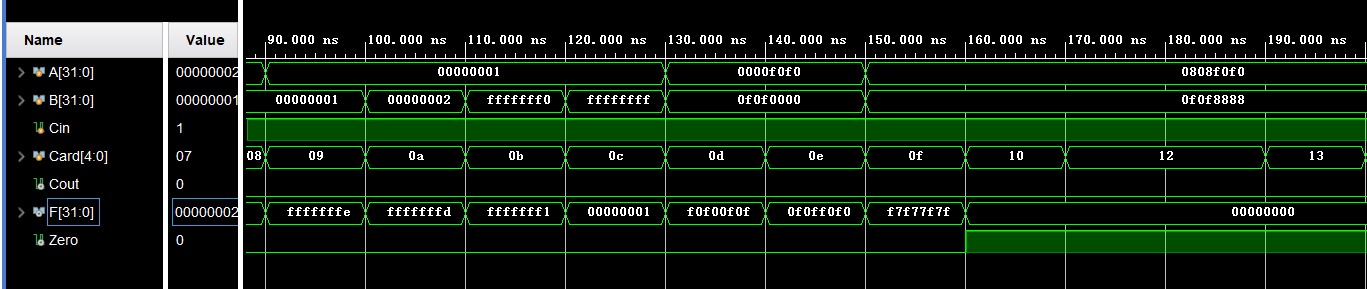

测试波形

| 运算功能 | A(H) | B(H) | Cin | 操作码 (五位) | F(H) | Zero |

|---|---|---|---|---|---|---|

| F=A加B | FFFF_FFFF | 0000_0001 | 1 | 00001 | 0000_0000 | 1 |

| F=A加B加Cin | FFFF_FFFF | 0000_0001 | 1 | 00010 | 0000_0001 | 0 |

| F=A减B | 0000_0001 | 0000_0002 | 1 | 00011 | FFFF_FFFF | 0 |

| F=A减B减Cin | 0000_0001 | 0000_0002 | 1 | 00100 | FFFF_FFFE | 0 |

| F=B减A | 0000_0002 | 0000_0001 | 1 | 00101 | FFFF_FFFF | 0 |

| F= B减A减Cin | 0000_0002 | 0000_0001 | 1 | 00110 | FFFF_FFFE | 0 |

| F=A | 0000_0002 | 0000_0001 | 1 | 00111 | 0000_0002 | 0 |

| F=B | 0000_0002 | 0000_0001 | 1 | 01000 | 0000_0001 | 0 |

| F=/A | 0000_0001 | 0000_0001 | 1 | 01001 | FFFF_FFFE | 0 |

| F=/B | 0000_0001 | 0000_0002 | 1 | 01010 | FFFF_FFFD | 0 |

| F=A+B | 0000_0001 | FFFF_FFF0 | 1 | 01011 | FFFF_FFF1 | 0 |

| F=AB | 0000_0001 | FFFF_FFFF | 1 | 01100 | 0000_0001 | 0 |

| F=A⊙B | 0000_F0F0 | 0F0F_0000 | 1 | 01101 | F0F0_0F0F _ _ | 0 |

| F=A⊕B | 0000_F0F0 | 0F0F_0000 | 1 | 01110 | 0F0F_F0F0 | 0 |

| F=/(AB) | 0808_F0F0 | 0F0F_8888 | 1 | 01111 | F7F7_7F7F | 0 |

| F=0 | 0808_F0F0 | 0F0F_8888 | 1 | 10000 | 0000_0000 | 1 |

实验结果分析:

对比实验结果与正确运算结果,实验结果符合预期。在前6个算术运算操作中,进位信号Cout表现正确。

比如在第2个“F=A加B加Cin”操作中,选取的例子为“A = ffff_ffffH, B = 0000_0001H, Cin = 1”,结果应为进1位,和为0000_0001H,结果正确。

逻辑运算中,测试用例较为复杂,如操作15与非运算,“A = 0808_f0f0H, B = 0f0f_8888H, F = f7f7_7f7fH”,结果正确。当运算操作码无效时,结果输出0。

六、实验总结

本次实验利用Vivado开发环境和Verilog硬件描述语言实现了一个简单的算术逻辑单元。通过本次实验,我们巩固了所学的数字逻辑知识,锻炼了硬件思维,提高了自身动手能力。

__EOF__