-

静态时序分析-配置STA环境

1.什么是STA环境

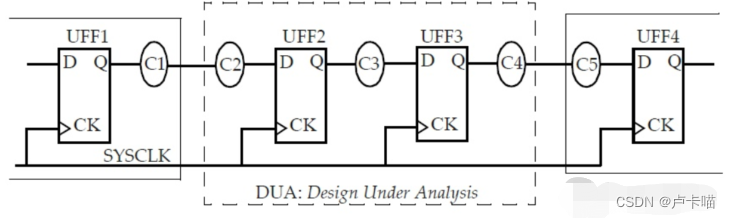

DUA(待分析设计)会与其它同步设计交互,例如DUA从触发器接收数据,并将数据输出到DUA外部的另一个触发器。为了对这种设计执行STA,需要指定触发器的时钟、以及进入设计和退出设计的所有路径的时序约束。

2.时钟配置

定义时钟

定义时钟需要:

- 时钟源

- 周期

- 占空比

- 边沿时间

create_clock -name SYSCLK -period 20 -waveform { 0 5} [get_ports SCLK]- 1

- 2

时钟名为SYSCLK,并在端口SCLK上定义, 周期为20ns。

-waveform {上升沿, 下降沿 ...},必须指定偶数个边沿时刻,然后不断重复,未指定默认值为 {0,period/2}

过渡时间

在某些情况下,工具无法自动计算出过渡时间,可以在时钟源处指定过渡时间(压摆),使用set_clock_transition来指定。

set_clock_transition -rise 0.1 [get_clocks CLK_CONFIG] set_clock_transition -fall 0.12 [get_clocks CLK_CONFIG]- 1

- 2

这个约束仅适用于理想时钟,一旦构建了时钟树就将其忽略,因为此时将会使用时钟引脚上的实际过渡时间。时钟不确定度

set_clock_uncertainty约束来指定时钟周期的时序不确定度(uncertainty),该不确定度可用于对可能会减少有效时钟周期的各种因素进行建模,包括时钟抖动(jitter)和其它需要考虑的悲观度。

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG] set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]- 1

- 2

时钟间不确定度(inter-clock uncertainty)用于指定跨时钟边界路径上的时钟不确定度。

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05 set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1- 1

- 2

时钟延迟

set_clock_latency指定时钟延迟

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK] set_clock_latency 2.1 -fall [all_clocks]- 1

- 2

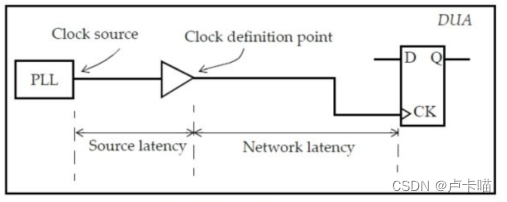

时钟延迟有两种类型:网络延迟(network latency)和源延迟(source latency)。网络延迟是指从时钟定义点到触发器时钟引脚的延迟。源延迟是指从时钟源到时钟定义点的延迟。

源延迟和网络延迟之间的一个重要区别是:一旦为设计建立了时钟树,就可以忽略网络延迟。在时钟树综合完成后,从时钟源到触发器时钟引脚的总时钟延迟是源延迟加上时钟树从时钟定义点到触发器的实际延迟。衍生时钟

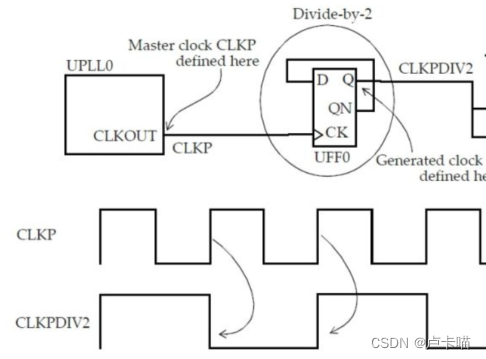

create_generated_clock是由主时钟(master clock)派生而来的时钟。

主时钟的2分频:

create_clock -name CLKP 10 [get_pins UPLLo -

相关阅读:

035、目标检测-物体和数据集

iNFTnews|Web3的核心是什么?一些需要考虑的观点

《算法系列》之位运算

ARM 账号注册报错 The claims exchange ‘Salesforce-UserWriteUsingEmail‘

java毕业设计开题报告基于SSM实现的家政服务系统

OpenCV函数总结

上手Spring

Linux高级IO

SAP角色描述-只能在Logon语言中修改问题解决 .

写给Python社群的第7课:用 Python 模块了不起呀?就是了不起

- 原文地址:https://blog.csdn.net/sinat_41774721/article/details/130526766