-

数字IC手撕代码-同步FIFO

前言:

本专栏旨在记录高频笔面试手撕代码题,以备数字前端秋招,本专栏所有文章提供原理分析、代码及波形,所有代码均经过本人验证。

目录如下:

10.数字IC手撕代码-数据位宽转换器(宽-窄,窄-宽转换)

13.数字IC手撕代码-流水握手(利用握手解决流水线断流、反压问题)

18.数字IC手撕代码-双端口RAM(dual-port-RAM)

...持续更新

更多手撕代码题可以前往 数字IC手撕代码--题库。

目录

原理介绍

在设计系统时,会包含工作在不同时钟频率下的元件,例如处理器和外设。数据在这些元件之间传输时先进先出(FIFO first in first out)阵列起到了重要作用。FIFO是用于对在通信总线上传输的数据进行排列的简单存储结构。

因此,FIFO常用来传输跨不同时钟域的数据。

本节介绍简单的同步FIFO架构,读写使用同样的时钟,为我们后续写异步FIFO(读写时钟非同源)做铺垫。

下面给出了一个同步FIFO的通用架构,DPRAM(Dual Port RAM 双端口RAM)作为存储器来存储信息,在此之上添加判断DPRAM空满信息的组件后,整个模块就是一个同步FIFO了,读写分别使用不同的使能和地址信号(读、写使能,读、写地址分立),使得整个模块可以进行同时读写。

通过读、写指针产生各自的读、写地址,送到读、写端口。写指针指向下一个要写入的地址,读指针指向下一个要读取的地址。有效写使能使得写指针递增, 有效的读使能使读指针递增。

图中的“状态模块”产生FIFO的空满信号,如果“fifo_full”有效,则说明FIFO内部的空间已满,不能再写入数据。如果“fifo_empty”有效,则说明FIFO内乜有可供读取的下一个有效数据。通过对读写指针位置的判断,该模块也可以指示出任意时刻FIFO中空或满区域的个数。

同步FIFO的工作方式

复位后,读写指针都归0。此时“fifo_empty”信号置为有效而“fifo_full”保持低电平。因为FIFO为空,所以阻止对FIFO的读操作,只能进行写操作。后续的写操作会增加写指针的值,并将“fifo_empty”信号置为无效。在写到最后一个数据时,写指针等于RAM_SIZE-1。此时进行一个写指针会使写指针滚回到0,并将“fifo_full”信号置为高电平。

总之,在读、写指针相等时,FIFO要么空要么满,所以需要对两种情况进行区分。

FIFO空满的产生

以深度为4的FIFO为例,一开始读写指针指向同一个位置,FIFO为空。写入三个数据之后,写指针指向RAM_SIZE-1=3的位置,此时再写入一个数据,写指针(wr_ptr)滚回0,和读指针指向同一个位置,此时FIFO为满。

根据这种逻辑,很容易推导出这么一个结论:无论读写指针此时指向什么位置,当wr_ptr+1==rd_ptr时,FIFO再写入一个数据就满了,所以有:

fifo_full = (rd_ptr == (wr_ptr + 1'b1))&& wr_fifo

从而有判断FIFO为满的RTL 代码:

- always@(posedge clk or negedge rstn)begin

- if(!rstn)

- fifo_full <= 1'b0;

- else if(wr_fifo && rd_fifo)

- ;//do nothing

- else if(rd_fifo)

- fifo_full <= 1'b0;

- else if((rd_ptr = wr_ptr + 1'b1) && wr_fifo)

- fifo_full <= 1'b1;

- end

类似的,当读操作使得两个指针在下一个时钟相等时,FIFO变空,产生“fifo_empty”信号。有如下关系:无论读写指针此时指向什么位置,当rd_ptr+1==wr_ptr时,FIFO再读出一个数据就空了。

fifo_empty = (wr_ptr == (rd_ptr + 1'b1))&& rd_fifo

从而有判断FIFO为空的RTL 代码:

- always @(posedge clk or negedge rstn)begin

- if(!rstn)

- fifo_empty <= 1'b1;

- else if(wr_fifo && rd_fifo)

- ;//do nothing

- else if(wr_fifo)

- fifo_empty <= 1'b0;

- else if((wr_ptr = rd_ptr + 1'b1) && rd_fifo)

- fifo_empty <= 1'b1;

- end

计数器判断空满

FIFO还有另一种利用计数器来指示FIFO空满的方法。

计数器的宽度要与FIFO的深度相等,这样计数器才能记录FIFO数据的最大个数。计数器在复位时初始化为0,随后的任何写操作会将其递增1,任何读操作会使其递减1。

在计数器为0时,很容易判断FIFO处于空状态,而当计数器的值等于FIFO的大小时,就能判断FIFO处于满状态。

对于这种采用计数器来判断空满的方式实现比较简单,但是和上一个比较读写指针位置的方法相比资源占用会高一些。因为这种方法要求增加额外的硬件(计数器)来进行计数。

代码

简单来说,FIFO就是一个有判断空满逻辑的双端口RAM,下面我们来写一下以指针循环一周期判断空满的方式的同步FIFO,但是在之前我们先要写一个双端口RAM来存储数据。

Dual Port RAM

- module dual_port_ram#(

- parameter DEPTH = 16,

- parameter WIDTH = 8

- )(

- input wr_clk ,

- input wr_en ,

- input [$clog(DEPTH)-1:0] wr_addr ,

- input [WIDTH-1:0] wr_data ,

- input rd_clk ,

- input rd_en ,

- input [$clog(DEPTH)-1:0] rd_addr ,

- output [WIDTH-1:0] rd_data

- );

- reg [WIDTH-1:0] RAM_MEM [DEPTH-1:0];

- always @(posedge wr_clk)begin

- if(wr_en)

- RAM_MEM[wr_addr] <= wr_data;

- end

- always @(posedge rd_clk)begin

- if(rd_en)

- RAM_MEM[rd_addr] <= rd_data;

- end

- endmodule

整个双端口RAM其实就是一个简单的写使能时,把数据写入输入的写地址。读使能时,把数据从地址里读出来的那么一个功能,后续在FIFO中例化该Dual Port RAM模块。

sync_FIFO

- `include "clog.v"

- module sync_fifo#(

- parameter WIDTH = 8 ,

- parameter DEPTH = 16

- )(

- input clk ,

- input rstn , // reset while rstn is negative

- //write interface

- input [WIDTH-1:0] data_in , // input data

- input wr_en , // write enable

- //read interface

- input rd_en , // read enable

- output [WIDTH-1:0] data_out ,

- output reg fifo_empty ,

- output reg fifo_full

- );

- //signal define

- reg [clog(DEPTH)-1:0] wr_ptr;

- reg [clog(DEPTH)-1:0] rd_ptr;

- wire wr_fifo;

- wire rd_fifo;

- //write data opration

- always @(posedge clk or negedge rstn)begin

- if(!rstn)

- wr_ptr <= 1'b0;

- else if(wr_fifo)

- wr_ptr <= wr_ptr + 1'b1;

- end

- assign wr_fifo = wr_en && !fifo_full;

- //read data opration

- always @(posedge clk or negedge rstn)begin

- if(!rstn)

- rd_ptr <= 1'b0;

- else if(rd_fifo)

- rd_ptr <= rd_ptr + 1'b1;

- end

- assign rd_fifo = rd_en && !fifo_empty;

- //full signal judgment

- always@(posedge clk or negedge rstn)begin

- if(!rstn)

- fifo_full <= 1'b0;

- else if(wr_fifo && rd_fifo)

- ;//do nothing

- else if(rd_fifo)

- fifo_full <= 1'b0;

- else if((rd_ptr == wr_ptr + 1'b1) && wr_fifo)

- fifo_full <= 1'b1;

- end

- //empty signal judgment

- always @(posedge clk or negedge rstn)begin

- if(!rstn)

- fifo_empty <= 1'b1;

- else if(wr_fifo && rd_fifo)

- ;//do nothing

- else if(wr_fifo)

- fifo_empty <= 1'b0;

- else if((wr_ptr == rd_ptr + 1'b1) && rd_fifo)

- fifo_empty <= 1'b1;

- end

- dual_port_ram #(

- .DEPTH (DEPTH) ,

- .WIDTH (WIDTH)

- )u_dual_port_ram

- (

- .wr_clk (clk) , //sync FIFO ,wr_clk = rd_clk

- .wr_en (wr_fifo) ,

- .wr_addr (wr_ptr) ,

- .wr_data (data_in) ,

- .rd_clk (clk) ,

- .rd_en (rd_fifo) ,

- .rd_addr (rd_ptr) ,

- .rd_data (data_out)

- );

- endmodule

此外,还写了一个判断位宽的函数clog.v

- `ifndef MY_CLOG

- `define MY_CLOG

- function integer clog (input integer depth);

- begin

- for (clog=0; depth-1>0; clog=clog+1)

- depth = depth >>1;

- end

- endfunction

- `endif

testbench

- `timescale 1ns/1ns

- module sync_fifo_tb();

- parameter WIDTH = 8;

- parameter DEPTH = 16;

- reg clk ;

- reg rstn ;

- reg [WIDTH-1:0] data_in ;

- reg rd_en ;

- reg wr_en ;

- wire [WIDTH-1:0] data_out ;

- wire empty ;

- wire full ;

- always #5 clk = ~clk;

- initial begin

- clk <= 1'b0;

- rstn <= 1'b0;

- data_in <= 'd0;

- rd_en <= 1'b0;

- wr_en <= 1'b0;

- //write 16 times to make fifo full

- #10

- rstn <= 1'b1;

- repeat(16)begin

- @(negedge clk)begin

- wr_en <= 1'b1;

- data_in <= $random; // generate 8bit random number data_in

- end

- end

- //read 16 times to make fifo empty

- repeat(16)begin

- @(negedge clk)begin

- wr_en <= 1'b0;

- rd_en <= 1'b1;

- end

- end

- //read and write 8 times

- repeat(8)begin

- @(negedge clk)begin

- wr_en <= 1'b1;

- data_in <= $random;

- rd_en <= 1'b0;

- end

- end

- //Continuous read and write

- forever begin

- @(negedge clk)begin

- wr_en <= 1'b1;

- data_in <= $random;

- rd_en <= 1'b1;

- end

- end

- end

- initial begin

- #800

- $finish();

- end

- initial begin

- $fsdbDumpfile("sync_fifo.fsdb");

- $fsdbDumpvars(0);

- end

- sync_fifo #(

- .WIDTH (WIDTH) ,

- .DEPTH (DEPTH)

- )u_sync_fifo

- (

- .clk (clk) ,

- .rstn (rstn) ,

- .data_in (data_in) ,

- .rd_en (rd_en) ,

- .wr_en (wr_en) ,

- .data_out (data_out) ,

- .fifo_empty (empty) ,

- .fifo_full (full)

- );

- endmodule

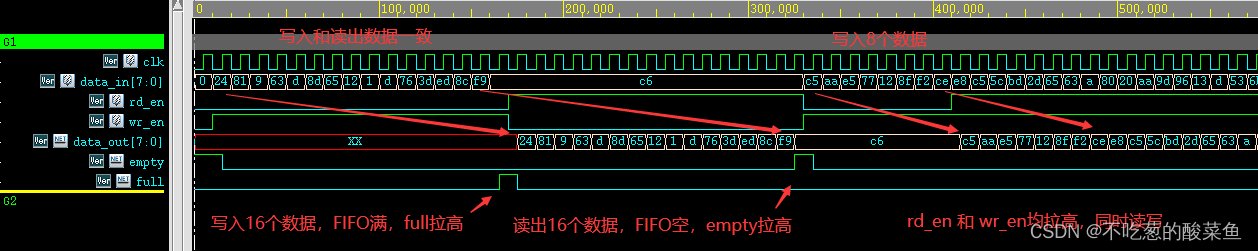

波形图

仿真结果和分析的结果一致, 写入16个数据将FIFO写满,此时full信号拉高;读出16个数据将FIFO读空,此时empty信号拉高;写入8个数据之后,同时读写,写入数据和读出数据均保持一致,功能正确。

了解了同步FIFO的设计方法后,再进行异步FIFO的设计就比较简单了,下篇博客记录如何写一个异步FIFO,解决FIFO中跨时钟域的问题。

更多手撕代码题可以前往 数字IC手撕代码--题库。

-

相关阅读:

Shell三剑客之sed命令详解

模拟实现.net中的Task机制:探索异步编程的奥秘

集合幂级数相关

21天学习挑战赛——Python操作MySQL和SqlServer

【电子元件】常用电子元器件的识别之电阻器

给EmEditor添加自定义外部工具DuilibPreviewer

【每日练习】牛客-组队决赛

LeetCode[662]二叉树的最大宽度

Opentelemetry SDK的简单用法

JVS-rules规则引擎,解决大数据风控的自动化决策利器

- 原文地址:https://blog.csdn.net/qq_57502075/article/details/128180751