-

嵌入式 ADC使用手册完整版 (188977万字)(附源码详细篇)

嵌入式 ADC使用手册完整版 (188977万字)💜(附源码详细篇)💜

- 【1】ADC简介

- 【2】ADC主要特征

- 【3】ADC引脚和内部信号

- 【4】ADC 模块框图

- 【5】ADC校准(CLB)

- 【6】ADC 时钟

- 【7】ADCON 开关

- 【8】ADC规则组和注入组

- 【9】ADC转换模式

- 【10】ADC注入通道管理

- 【11】ADC模拟看门狗

- 【12】ADC数据对齐

- 【13】ADC可编程的采样时间

- 【14】ADC外部触发

- 【15】ADC DMA 请求

- 【16】ADC温度传感器和内部参考电压 VREFINT

- 【17】ADC可编程分辨率(DRES) – 快速转换模式

- 【18】ADC片上硬件过采样

- 【19】ADC 同步模式

- 【20】ADC中断

- 【21】ADC 寄存器 [写代码须知]

- 【22】ADC基地址

- 【23】ADC状态寄存器 (ADC_STAT)

- 【24】ADC控制寄存器 0 (ADC_CTL0)

- 【25】ADC控制寄存器 1 (ADC_CTL1)

- 【26】ADC采样时间寄存器 0 (ADC_SAMPT0)

- 【27】ADC采样时间寄存器 1 (ADC_SAMPT1)

- 【28】ADC注入通道数据偏移寄存器 x (ADC_IOFFx) (x=0..3)

- 【29】ADC看门狗高阈值寄存器 (ADC_WDHT)

- 【30】ADC看门狗低阈值寄存器 (ADC_WDLT)

- 【31】ADC规则序列寄存器 0 (ADC_RSQ0)

- 【32】ADC规则序列寄存器 1 (ADC_RSQ1)

- 【33】ADC规则序列寄存器 2 (ADC_RSQ2)

- 【34】ADC注入序列寄存器 (ADC_ISQ)

- 【35】ADC注入数据寄存器 x (ADC_IDATAx) (x= 0..3)

- 【36】ADC规则数据寄存器 (ADC_RDATA)

- 【37】ADC过采样控制寄存器 (ADC_OVSAMPCTL)

- 【38】ADC源码

- ADC结局总结

ADC的用途非常广泛,常常用于采集电压等数据,本章介绍ADC的使用 和 说明 嵌入式的伙伴一定要收藏哦

【1】ADC简介

【1】12位ADC是一种采用

逐次逼近方式的模拟数字转换器。它有18个多路复用通道,可以转换来自16个外部通道和2个内部通道的模拟信号。

【2】模拟看门狗允许应用程序来检测输入电压是否超出用户设定的高低阈值。

【3】各种通道的A/D转换可以配置成单次、连续、扫描或间断转换模式。

【4】ADC转换的结果可以按照左对齐或右对齐的方式存储在16位数据寄存器中。

【5】片上的硬件过采样机制可以通过减少来自MCU的相关计算负担来提高性能。

【2】ADC主要特征

高性能:

` – 可配置12位、10位、8位、或者6位分辨率; – 自校准; – 可编程采样时间; – 数据寄存器可配置数据对齐方式; – 支持规则数据转换的DMA请求。 `- 1

- 2

- 3

- 4

- 5

- 6

- 7

模拟输入通道:

` – 16个外部模拟输入通道; – 1个内部温度传感通道(VSENSE); – 1个内部参考电压输入通道(VREFINT)。 `- 1

- 2

- 3

- 4

- 5

转换开始的发起:

` - 软件触发; – 硬件触发。 `- 1

- 2

- 3

- 4

转换模式:

` – 转换单个通道,或者扫描一序列的通道; – 单次模式,每次触发转换一次选择的输入通道; –连续模式,连续转换所选择的输入通道; – 间断模式; – 同步模式(适用于具有两个或多个ADC的设备)。 `- 1

- 2

- 3

- 4

- 5

- 6

- 7

模拟看门狗。

中断的产生:

` – 规则组或注入组转换结束; – 模拟看门狗事件。 `- 1

- 2

- 3

- 4

过采样:

` – 16位的数据寄存器; – 可调整的过采样率,从2x到256x; – 高达8位的可编程数据移位。 `- 1

- 2

- 3

- 4

- 5

ADC供电要求:

2.6V到3.6V,一般电源电压为3.3V。

ADC输入范围:

VREFN≤VIN≤VREFP。

【3】ADC引脚和内部信号

图12-1. ADC模块框图给出了ADC框图。

表12-1. ADC内部信号给出了ADC

表12-2. ADC引脚定义给出了ADC引脚说明。

注意:VDDA和VSSA必须分别连接到VDD和VSS。

【4】ADC 模块框图

【5】ADC校准(CLB)

ADC 带有一个前置校准功能。

【1】在校准期间,ADC 计算一个校准系数,这个系数是应用于 ADC 内部的,它直到 ADC下次掉电才无效。

【2】在校准期间,应用不能使用 ADC,它必须等到校准完 成。

在 A/D 转换前应执行校准操作。通过软件设置 CLB=1 来对校准进行初始化,在校准期间 CLB 位会一直保持 1,直到校准完成,该位由硬件清 0。当 ADC 运行条件改变(例如,VDDA、VREFP 以及温度等),建议重新执行一次校准操作。

内部的模拟校准通过设置 ADC_CTL1 寄存器的 RSTCLB 位来重置。

软件校准过程:

1. 确保ADCON=1; 2. 延迟14个ADCCLK以等待ADC稳定; 3. 设置RSTCLB (可选的); 4. 设置CLB=1; 5. 等待直到CLB=0。(直到校准完成,该位由硬件清 0)- 1

- 2

- 3

- 4

- 5

【6】ADC 时钟

ADCCLK 时钟是由

时钟控制器提供的,它和AHB、APB2 时钟保持同步。

在RCU 时钟控制器中,有一个专门用于ADC 时钟的可编程分频器。

【7】ADCON 开关

ADC_CTL1 寄存器中的 ADCON 位是 ADC 模块的使能开关。

如果该位为 0,则 ADC 模块保 持复位状态。

为了省电,

当ADCON 位为 0 时,ADC 模拟子模块将会进入掉电模式。

ADC 使 能后需要等待 tus时间后才能采样,tsu 数值详见芯片数据手册。

【8】ADC规则组和注入组

ADC 支持 18 个多路通道,可以把转换组织成两组:

一个规则组通道和一个注入组通道。

规则组,可以按照特定的序列组织成多达

16 个转换的序列。ADC_RSQ0~ADC_RSQ2 寄存器

规定了规则组的通道选择。

ADC_RSQ0 寄存器的RL[3:0]位规定了整个规则组转换序列的长 度。

注入组,可以按照特定的序列组织成多达

4 个转换的序列。ADC_ISQ 寄存器规定了注入组的 通道选择。

ADC_ISQ 寄存器的IL[1:0]位规定了整个注入组转换序列的长度。

【9】ADC转换模式

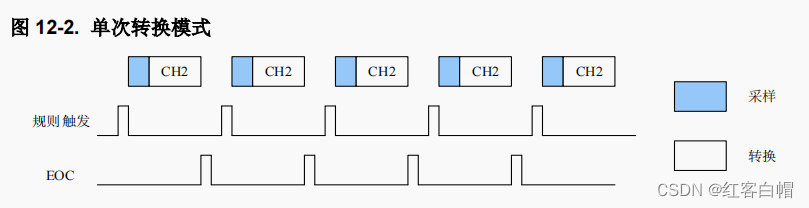

【9.1】ADC单次转换模式

该模式能够运行在

规则组和注入组。

单次转换模式下,ADC_RSQ2 寄存器的 RSQ0[4:0]位或 者 ADC_ISQ 寄存器的 ISQ3[4:0]位规定了 ADC 的转换通道。

当ADCON 位被置 1,一旦相应 软件触发或者外部触发发生,ADC 就会采样和转换一个通道。

规则通道单次转换结束后,转换数据将被存放于 ADC_RDATA 寄存器中,EOC 将会置 1。如果 EOCIE 位被置 1,将产生一个中断。

注入通道单次转换结束后,转换数据将被存放于 ADC_IDATA0 寄存器中。

EOC 和 EOIC 位将会置 1。如果 EOCIE 或 EOICIE 位被置 1,将产生一个中断。

规则组单次转换模式的软件流程:

-

- 确保ADC_CTL0寄存器的DISRC(规则组间断模式)和SM(扫描转换模式)位以及ADC_CTL1寄存器的CTN(连续模式)位为0;

-

- 用模拟通道编号来配置RSQ0(规则序列寄存器 0);

-

- 配置ADC_SAMPTx寄存器(采样时间寄存器 1);

-

- 如果有需要,可以配置ADC_CTL1寄存器的ETERC(规则组外部触发使能)和ETSRC(规则组外部触发选择)位;

-

- 设置SWRCST(规则组转换开始)位,或者为规则组产生一个外部触发信号;

-

- 等到EOC置1;(硬件自动置1)

-

- 从ADC_RDATA(规则数据寄存器)寄存器中读ADC转换结果;

-

- 写0清除EOC标志位。(软件手动清零)

注入组单次转换模式的软件流程:

-

- 确保ADC_CTL0寄存器的DISRC(规则组间断模式)和SM(扫描转换模式)位为0;

-

- 用模拟通道编号来配置ISQ3 (注入序列寄存器 :通道编号(0…17)写入这些位来选择注入组的第 n 个转换的通道);

-

- 配置ADC_SAMPTx寄存器 (采样时间寄存器 );

-

- 如果有需要,可以配置ADC_CTL1寄存器的ETEIC(注入组外部触发使能)和ETSIC(注入组外部触发选择)位;

- 5. 设置SWICST(注入组转换开始)位,或者为注入组产生一个外部触发信号;

-

- 等到EOC、EOIC置1;(硬件自己置1)

-

- 从ADC_IDATA0(注入数据寄存器)寄存器中读ADC转换结果;

-

- 写0清除EOC、EOIC标志位。(手动写入)

【9.2】ADC连续转换模式

该模式可以运行在

规则组通道上。

对 ADC_CTL1 寄存器的 CTN 位置 1 可以使能连续转换模式。 在此模式下,ADC 执行由RSQ0[4:0]规定的转换通道。

当 ADCON 位被置 1,一旦相应软件触发或者外部触发产生,ADC就会采样和转换规定的通道。转换数据保存在ADC_RDATA(规则数据寄存器) 寄存器中。

规则组连续转换模式的软件流程:

1. 设置ADC_CTL1寄存器的CTN(连续转换模式)位为1;

2. 根据模拟通道编号配置RSQ0;

3. 配置ADC_SAMPTx寄存器;

4. 如果有需要,配置ADC_CTL1寄存器的ETERC和ETSRC位;

5. 设置SWRCST位,或者给规则组产生一个外部触发信号;

6. 等待EOC标志位置1;(硬件置1 :代表转化结束)

7. 从ADC_RDATA寄存器中读ADC转换结果;

8. 写0清除EOC标志位;(软件置0:代表可以再次开启转化)

9. 只要还需要进行连续转换,重复步骤【6~8】。

由于要循环查询 EOC(转化结束) 标志位,DMA(直接存储器访问寄存器) 可以被用来传输转换数据,软件流程如下:1. 设置

ADC_CTL1寄存器的CTN位为1;

2. 根据模拟通道编号配置RSQ0;

3. 配置ADC_SAMPTx寄存器;

4. 如果有需要,配置ADC_CTL1寄存器的ETERC和ETSRC位;

5. 准备DMA模块,用于传输来自ADC_RDATA(规则数据寄存器)的数据;

6. 设置SWRCST位,或者给规则组产生一个外部触发。(两种选择 都可以开始转换)

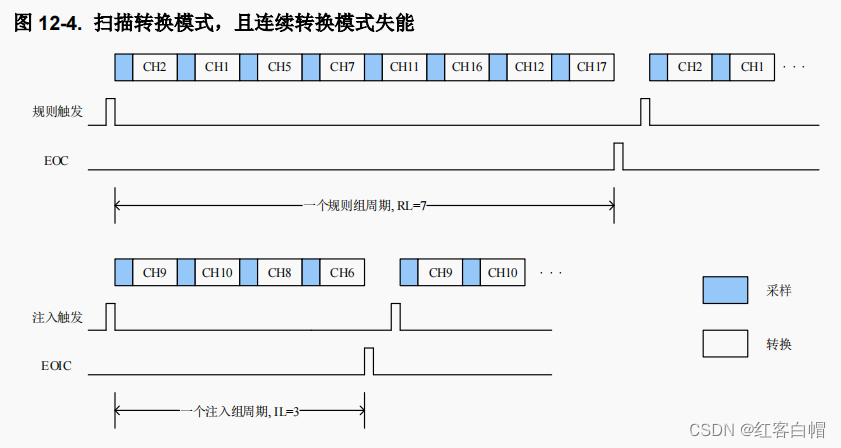

【9.3】ADC扫描转换模式

扫描转换模式可以通过将 ADC_CTL0 寄存器的 SM 位置 1 来使能。

在此模式下,ADC 扫描转换所有被ADC_RSQ0~ADC_RSQ2 寄存器或 ADC_ISQ 寄存器选中的所有通道。

一旦ADCON 位被置 1,当相应软件触发或者外部触发产生,ADC 就会一个接一个的采样和转换规则组或注入组通道。

转换数据存储在 ADC_RDATA 或ADC_IDATAx 寄存器中。

规则组或注入组转换结束后,EOC 或者 EOIC 位将被置 1。如果 【EOCIE 或 EOICIE 位被置1,将产生中断】。

当规则组通道工作在扫描模式下时,ADC_CTL1 寄存器的 DMA 位必须设置为 1。

如果 ADC_CTL1 寄存器的 CTN 位也被置 1,则在规则通道转换完之后,这个转换自动重新开 始。(

扫描模式和连续转化模式并存)

规则组扫描转换模式的软件流程:

1. 设置 ADC_CTL0 寄存器的 SM 位和 ADC_CTL1 寄存器的 DMA 位为 1;

2. 配置 ADC_RSQx 和 ADC_SAMPTx 寄存器;

3. 如果有需要,配置 ADC_CTL1 寄存器中的 ETERC 和 ETSRC 位;

4. 准备 DMA 模块,用于传输来自 ADC_RDATA 的数据;

5. 设置 SWRCST 位,或者给规则组产生一个外部触发;

6. 等待 EOC 标志位置 1;

7. 写 0 清除 EOC 标志位。

注入组扫描转换模式的软件流程:

1. 设置 ADC_CTL0 寄存器的 SM 位为 1;

8. 配置 ADC_ISQ 和 ADC_SAMPTx 寄存器;

9. 如果有需要,配置 ADC_CTL1 寄存器中的 ETEIC 和 ETSIC 位;

10. 设置 SWRCST 位,或者给注入组产生一个外部触发;

11. 等待 EOC、EOIC 标志位置 1;

12. 读 ADC_IDATAx 寄存器中的转换结果;

13. 写 0 清除 EOC、EOIC 标志位。

【9.4】ADC间断模式

对于规则组,ADC_CTL0 寄存器的 DISRC 位置 1 使能间断转换模式。

该模式下可以执行一次 n 个通道的短序列转换(n<=8),此转换是ADC_RSQ0~RSQ2 寄存器所选择的转换序列的一部分。

数值 n 由 ADC_CTL0寄存器的 DISCNUM[2:0]位(间断模式下的转换数目)给出。

当相应的软件触发或外部触发发生,ADC 就会采样和转换在ADC_RSQ0~RSQ2寄存器所选择通道中接下来的 n 个通道,直到规则序列中所有的通道转换完成。

每个规则组转换周期结束后,EOC位将被置1。如果EOCIE

位被置 1 将产生一个中断。

对于注入组,ADC_CTL0 寄存器的 DISIC 位置 1 使能间断转换模式。

该模式下可以执行ADC_ISQ 寄存器所选择的转换序列的一个通道进行转换。

当相应的软件触发或外部触发发生, ADC 就会采样和转换ADC_ISQ寄存器中所选择通道的下一个通道,直到注入组序列中所有通道转换完成。

每个注入组通道转换周期结束后,EOIC 位将被置 1。如果 EOICIE 位被置 1 将 产生一个中断。

规则组和注入组不能同时工作在间断模式,同一时刻只能有一组被设置成间断模式。

规则组间断模式的软件流程:

1. 设置ADC_CTL0寄存器的DISRC 位和ADC_CTL1寄存器的DMA位为 1;

2. 配置 ADC_CTL0 寄存器的DISNUM[2:0]位;

3. 配置ADC_RSQx 和 ADC_SAMPTx寄存器;

4. 如果有需要,配置 ADC_CTL1 寄存器中的ETERC 和 ETSRC 位;

5. 准备DMA模块,用于传输来自 ADC_RDATA 的数据;

6. 设置SWRCST 位,或者给规则组产生一个外部触发;

7. 如果需要,重复步骤 【6】;

8. 等待 EOC 标志位置 1;

9. 写 0 清除 EOC 标志位。

注入组间断模式的软件流程:

1. 设置 ADC_CTL0 寄存器的 DISRC 位为 1;

9. 配置 ADC_ISQ 和 ADC_SAMPTx 寄存器;

10. 如果有需要,配置 ADC_CTL1 寄存器中的 ETEIC 和 ETSIC 位;

11. 设置 SWICST 位,或者给注入组产生一个外部触发;

12. 如果需要,重复步骤 【4】;

13. 等待 EOC、EOIC 标志位置 1;

14. 读 ADC_IDATAx 寄存器中的转换结果;

15. 写 0 清除 EOC、EOIC 标志位。

【10】ADC注入通道管理

【10.1】ADC自动注入

如果将

ADC_CTL0寄存器的ICA位置 1,在规则组通道之后,注入组通道被自动转换。

该模式下注入组通道的外部触发不能被使能。

该模式可以转换ADC_RSQ0~ADC_RSQ2 和 ADC_ISQ寄存器中设置的多至20个转换序列。

除了ICA 位之外,如果CTN 位也被置 1,注 入组通道将在规则组通道之后被自动转换。

【10.2】ADC触发注入

清除 ICA 位,在规则组通道转换期间如果软件触发或者外部触发发生,则启动触发注入转换。

这种情况下,ADC取消当前转换,注入通道序列进行转换 。

注入通道组转换结束后,规则组转换从上次被取消的转换处重新开始。

【11】ADC模拟看门狗

【1】 ADC_CTL0 寄存器的

RWDEN 和 IWDEN 位置 1将分别使能规则组和注入组的模拟看门狗功 能。

【2】 如果ADC 的模拟转换电压低于低阈值或高于高阈值时,ADC_STAT 状态寄存器的WDE 位将被置 1。

【3】如果WDEIE 位被置 1,将产生中断。

【4】ADC_WDHT 和 ADC_WDLT 寄存器用来设 定高低阈值。

【5】内部数据的比较在对齐之前完成,因此阀值与 ADC_CTL1寄存器的DAL 位确定 的对齐方式无关。

【6】ADC_CTL0 寄存器的RWDEN,IWDEN,WDSC 和 WDCHSEL[4:0]位可以 用来选择模拟看门狗监控单一通道或者多通道。

【12】ADC数据对齐

ADC_CTL1 寄存器的 DAL 位确定转换后数据存储的对齐方式。

注入组通道转换的数据值已经减去了在ADC_IOFFx寄存器中定义的偏移量,因此结果可能是 一个负值。符号值是一个扩展值。

6 位分辨率的数据对齐不同于 12 位/10 位/8 位分辨率数据对齐,如图 12-10 所示。

【13】ADC可编程的采样时间

ADC 使用若干个 ADCCLK 周期对输入电压采样,采样周期数目可以通过

ADC_SAMPT0 和ADC_SAMPT1 寄存器的SPTn[2:0]位更改。

每个通道可以用不同的时间采样。在 12 位分辨率的情况下,

总转换时间=采样时间+12.5 个 ADCCLK 周期。例如:

ADCCLK = 30MHz ,采样时间为 1.5 个周期,那么总的转换时间为:“1.5+12.5”个 ADCCLK 周期,即

0.467us。 【14/30=0.46666666】

【14】ADC外部触发

外部触发输入的上升沿可以触发规则组或注入组的转换。

规则组的外部触发源由 ADC_CTL1 寄存器的ETSRC[2:0]位控制,注入组的外部触发源由 ADC_CTL1 寄存器的ETSIC[2:0]位控 制。

ETSRC[2:0]和 ETSIC[2:0]控制位可以用来确定 8 个可能事件中的哪一个可以触发规则和注入组的转换。

【15】ADC DMA 请求

DMA 请求,可以通过设置 ADC_CTL1 寄存器的 DMA 位来使能,它用于规则组多个通道的转 换结果。

ADC在规则组一个通道转换结束后产生一个 DMA 请求,DMA 接受到请求后可以将 转换的数据从 ADC_RDATA寄存器传输到用户指定的目的地址。

【16】ADC温度传感器和内部参考电压 VREFINT

将 ADC_CTL1 寄存器的 TSVREN 位置 1 可以使能

温度传感器通道(ADC0_CH16)和 VREFINT通道(ADC0_CH17)。

温度传感器可以用来测量器件周围的温度。

传感器输出电压能被 ADC 转换成数字量。建议温度传感器的采样时间至少设置为 ts_temp µs(具体数值请参考 datasheet 文 档)。

温度传感器不用时,复位TSVREN位可以将其置于掉电模式。

温度传感器的输出电压随温度线性变化,由于生产过程的多样化,温度变化

曲线的偏移在不同 的芯片上会有不同(最多相差

45°C)。

内部温度传感器更适合于检测温度的变化,而不是测量绝对温度。

如果需要测量精确的温度,应该使用一个外置的温度传感器来校准这个偏移错误。

内部电压参考VREFINT : 提供了一个稳定的(

带隙基准)电压输出给 ADC 和比较器。VREFINT 内 部连接到 ADC0_CH17输入通道。

使用温度传感器:

1. 配置温度传感器通道(ADC_IN16)的转换序列和采样时间为 ts_temp µs

2. 置位 ADC_CTL1 寄存器中的 TSVREN 位,使能温度传感器

3. 置位 ADC_CTL1 寄存器的 ADCON 位,或者由外部触发启动 ADC 转换

4. 从 ADC 数据寄存器中读取并计算温度传感器数据 Vtemperature,并由下面公式计算出实际温度:

温度 (°C) = {(V25 – Vtemperature) / Avg_Slope} + 25

V25:温度传感器在 25°C 下的电压,典型值请参考相关型号 datasheet。

Avg_Slope:温度与温度传感器电压曲线的均值斜率,典型值请参考相关型号datasheet。

【17】ADC可编程分辨率(DRES) – 快速转换模式

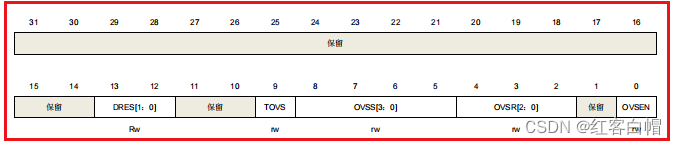

通过降低 ADC 的分辨率,可能获得较快的转换时间(tADC)。 对寄存器 ADC_OVSAMPCTL 中的 DRES[1:0]位进行编程即可配置分辨率为 6、8、10、12 位。

对于那些不需要高精度数据的应用,可以使用较低的分辨率来实现更快速地转换。

只有在 ADCON 比特为 0 时,才能修改 DRES[1:0]的值。

较低的分辨率能够减少转换时间。

如表 12-7.不同分辨率对应的 tCONV 时间所示,较低的分辨率能够减少逐次逼近步骤所需的转换时间 tADC。

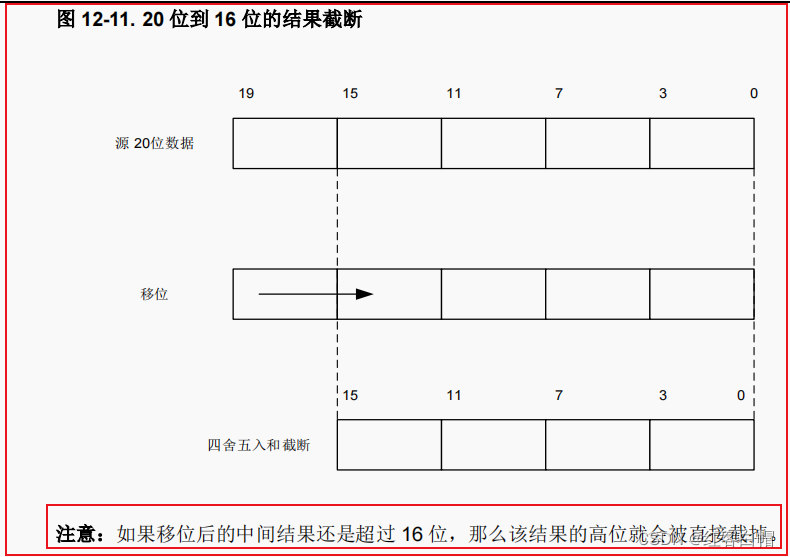

【18】ADC片上硬件过采样

片上硬件过采样单元执行数据预处理以减轻 CPU 负担。

它能够处理多个转换,并将多个转换的结果取平均,得出一个16位宽的数据。其结果值根据如下公式计算得出,其中 N 和 M 的值 可以被调整,过采样单元可以通过设置 ADC_OVSAMPCTL 寄存器的OVSEN 位来使能,它 是以降低数据输出率为代价,换取较高的数据分辨率。

Dout(n)是指 ADC 输出的第 n 个数字信 号:

片上硬件过采样单元执行两个功能:

求和和位右移。

【1】过采样率N 是在 ADC_OVSAMPCTL 寄 存器的OVSR[2:0]位定义,它的取值范围为 2x 到 256x。【2】

除法系数M 定义一个多达 8 位的右 移,它通过 ADC_OVSAMPCTL 寄存器 OVSS[3:0]位进行配置。

求和单元能够生成一个

多达 20 位(256*12 位)的值。

【1】首先,将这个值要进行右移,将移位后剩 余的部分再通过取整转化一个近似值,最后将高位会被截断,仅保留最低 16 位有效位作为最 终值传入对应的数据寄存器中。

图 12-12. 右移 5 位和取整的数例描述一个从原始 20 位的累积数值处理成 16 位结果值的例子。

表 12-8. N 和 M 的最大输出值(灰色部分表示截断)给出了 N 和 M 各种组合的数据格式,初始转换值为 0xFFF。

和标准的转换模式

相比,过采样模式的转换时间不会改变:在整个过采样序列的过程中采样时 间仍然保持相等。

每 N个转换就会产生一个新的数据,一个等价的延迟为 N x tADC = N x (tSMPL + tCONV)。

【19】ADC 同步模式

在有两个或者两个以上的 ADC 模块的产品中,可以使用 ADC 同步模式。

在 ADC 同步模式下, 根据ADC_CTL0 寄存器中SYNCM[3:0]位所选的模式,转换的启动可以是 ADC0 主和 ADC1 从的交替触发或同步触发。

在同步模式下,当配置由外部事件触发的转换时,从 ADC 必须通 过软件来配置触发来,从而避免错误的触发引起不必要的转换。此外,对于主 ADC 和从 ADC 的外部触发必须被使能。

共有以下几种模式:

` – 独立模式 – 规则并行模式 – 注入并行模式 – 快速交叉模式 – 慢速交叉模式 – 交替触发模式 – 注入并行模式+规则并行模式 – 规则并行模式+交替触发模式 – 注入并行模式+交叉模式 `- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

在 ADC 同步模式下,即使 DMA 不用,也要将 DMA 置位,

从 ADC的转换数据可以通过主ADC数据寄存器读取。ADC 同步框图如图 12-13. ADC 同步框图所示。

【19.1】ADC独立模式

在这种模式下,ADC 同步是忽略的,每个 ADC 都独立工作。

【19.2】ADC规则并行模式

此模式可并行转换规则通道组,外部触发来源于

规则通道组的ADC0的多路开关(由ADC_CTL1寄存器的ETSRC[2:0]决定),ADC1 被并行触发。

在 ADC0 或 ADC1 的转换事件结束时,即ADC0 或 ADC1的规则通道组转换完毕,会产生一个EOIC 中断。32 位 ADC_RDATA 寄存器包含上半字(由 ADC1 转换的数据构成)和下半字(由ADC0 转换的数据构成),32 位的DMA被用来将 ADC_RDATA 中的数据传送到SRAM。

注意:

1.不要在两路 ADC 上转换相同的通道(两路 ADC 在同一通道转换时采样时间不可重叠)。

2.在并行模式下,ADC0 和 ADC1 并行采样的两个通道的需要设置为准确的相同采样时间。

【19.3】ADC注入并行模式

此模式同时转换一个注入通道组,外部触发来源于注入通道组的多路开关(由

ADC_CTL1寄存 器的ETSIC[2:0]决定),ADC1被并行触发。

在ADC0 或 ADC1的转换事件结束时,即 ADC0 和 ADC1 的注入通道组被转换完,会产生一 个EOIC 中断。其转换的数据被存储在各自的ADC_IDATAx寄存器中。

注意:

1.不要在两路 ADC 上转换相同的通道(两路 ADC 在同一通道转换时采样时间不可重叠)。

2.在并行模式下,ADC0 和 ADC1 并行采样的两个通道的需要设置为准确的相同采样时间。

【19.4】ADC快速交叉模式

此模式应用于规则通道组(通常一个通道),外部触发来源于规则通道组的

ADC0的多路开关 (由ADC_CTL1寄存器的ETSRC[2:0]决定)。

当触发产生时,ADC1 立刻启动,而 ADC0 在7个 ADC 时钟周期后启动。

如果 ADC0 和 ADC1 的 CTN 位被置位,所选的规则通道组在两个 ADC 中被不停的转换。

32 位 ADC_RDATA 寄存器包含上半字(由 ADC1 转换的数据构成)和下班字(由 ADC0 转换 的数据构成)。

在ADC0产生EOC 中断后(可通过置位EOCIE 位),可通过 32 位 DMA 将 ADC_RDATA 中数据传送到 SRAM。

注意:

可允许的最大采样时间必须小于 7 个 ADC 采样时钟,从而避免 ADC0 和 ADC1 在转换相同通道时出现采样时钟重叠。

【19.5】ADC慢速交叉模式

此模式应用于规则通道组(通常一个通道),外部触发来源于规则通道组的

ADC0的多路开关 (由ADC_CTL1 寄存器的ETSRC[2:0]决定)。

当触发产生时,ADC1立刻启动,而ADC0在14个 ADC 时钟周期后启动,在ADC0启动后的14个时钟周期,ADC1再次启动。

该模式下不需要使用连续模式,因为该模式本身会连续转换规则组。

32 位 ADC_RDATA寄存器包含上半字(由 ADC1 转换的数据构成)和下半字(由 ADC0 转换 的数据构成)。

在ADC0产生EOC 中断后(可通过置位EOCIE 位),可通过 32 位DMA将ADC_RDATA中数据传送到SRAM。

注意:

1.可允许的最大采样时间必须小于 14 个 ADC 采样时钟,从而避免 ADC0 和 ADC1 在转换相同通道时出现采样时钟重叠。

2.在快速交叉模式和慢速交叉模式下,必须确保没有注入通道事件被外部触发。

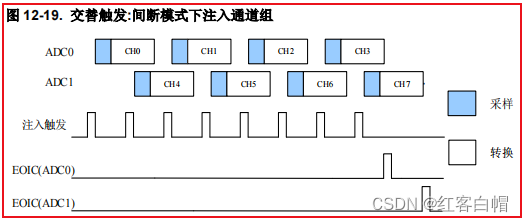

【19.6】ADC交替触发模式

此模式应用于注入通道组(通常一个通道),外部触发来源于

注入通道组的 ADC0 的多路开关(由 ADC_CTL1 寄存器的ETSRC[2:0]决定)。

当第一次触发发生,ADC0所有的注入通道被转换。

当第二次触发发生,ADC1所有的注入通道被转换。

如果 ADC0 和 ADC1 的 EOIC 中断被使能,二者的通道被转换完毕,其相应的中断就会被触发。

如果所有的注入通道组转换完成后另一个外部触发发生,那么交替触发进程将通过转换 ADC0注入通道组实现重启。

如果

使能 ADC0 和 ADC1 间断模式,

当第一次触发发生,ADC0 转换第一组注入通道。

当第二次触发发生,ADC1 转换第一组注入通道。

然后,ADC0 转换第二组注入通道,ADC1 转换第 二组通道,以此类推。

如果 ADC0 和 ADC1 的 EOIC 中断被使能,二者的通道被转换完毕,其相应的中断就会被触 发。

如果所有的注入通道组转换完成后另一个外部触发发生,那么交替触发进程将实现重启。

【19.7】ADC规则并行和注入并行组合模式

在独立模式下,规则通道组的转换可以被注入通道组的转换所中断。

在 ADC 同步模式下,注 入并行通道组的转换也可以中断规则并行通道组的转换。

注意:在规则并行和注入并行组合模式下,两路通道的采样时间应该被设置成相同值。

【19.8】ADC规则并行和交替触发组合模式

注入通道组的交替触发转换的启动可以中断规则通道组的并行转换。如图所示,交替触发中断规则并行转换。

当注入通道事件发生时,注入交替转换立刻启动。如果规则转换此刻正在运行, 为保证注入 通道组转换启动后的同步,规则通道组在两路 ADC 的转换停止。当注入通道组转换完成后, 规则通道组的转换同步启动。

注意:在规则并行和交替触发组合模式下,两路通道的采样时间应该被设置成相同值。

【19.9】ADC注入并行和交叉组合模式

通过注入转换可以中断交叉转换,当注入触发发生时,交叉变换被中断,注入转换启动。在注入转换完成后,交叉转换恢复,如图 12-22 所示。

【20】ADC中断

以下任一个事件发生都可以产生中断:

规则组和注入组转换结束;

模拟看门狗事件;单独的中断使能位可使得使用更灵活。

ADC0、ADC1 和 ADC2 都被映射到同一个中断向量 ISR[18]。

【21】ADC 寄存器 [写代码须知]

寄存器这里比较重要,以最高标题解析

【22】ADC基地址

ADC0 基地址:0x4001 2400

ADC1 基地址:0x4001 2800

ADC2 基地址:0x4001 3C00

【23】ADC状态寄存器 (ADC_STAT)

地址偏移:0x00

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【24】ADC控制寄存器 0 (ADC_CTL0)

地址偏移:0x04

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【25】ADC控制寄存器 1 (ADC_CTL1)

地址偏移:0x08

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【26】ADC采样时间寄存器 0 (ADC_SAMPT0)

地址偏移:0x0C

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【27】ADC采样时间寄存器 1 (ADC_SAMPT1)

地址偏移:0x10

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【28】ADC注入通道数据偏移寄存器 x (ADC_IOFFx) (x=0…3)

地址偏移:0x14-0x20

复位值:0x0000 0000

该寄存器只能按字(32位)访问

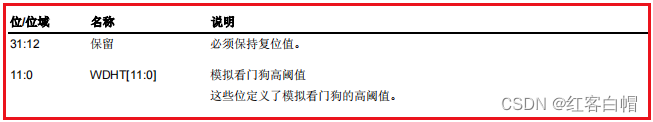

【29】ADC看门狗高阈值寄存器 (ADC_WDHT)

地址偏移:0x24

复位值:0x0000 0FFF

该寄存器只能按字(32位)访问

【30】ADC看门狗低阈值寄存器 (ADC_WDLT)

地址偏移:0x28

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【31】ADC规则序列寄存器 0 (ADC_RSQ0)

地址偏移:0x2C

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【32】ADC规则序列寄存器 1 (ADC_RSQ1)

地址偏移:0x30

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【33】ADC规则序列寄存器 2 (ADC_RSQ2)

地址偏移:0x34

复位值:0x0000 0000

该寄存器只能按字(32位)访问

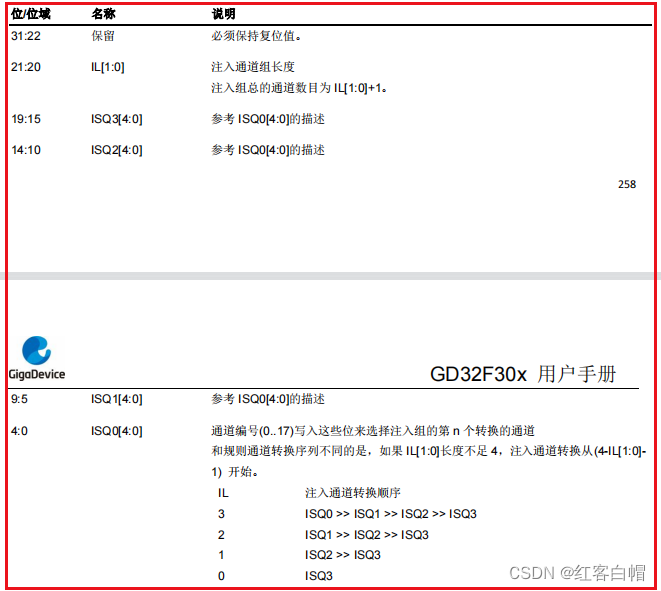

【34】ADC注入序列寄存器 (ADC_ISQ)

地址偏移:0x38

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【35】ADC注入数据寄存器 x (ADC_IDATAx) (x= 0…3)

地址偏移:0x3C-0x48

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【36】ADC规则数据寄存器 (ADC_RDATA)

地址偏移:0x4C

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【37】ADC过采样控制寄存器 (ADC_OVSAMPCTL)

地址偏移:0x80

复位值:0x0000 0000

该寄存器只能按字(32位)访问

【38】ADC源码

源码内容庞大,本文章是容不下了,注释的非常清晰,但是对于ADC的初始化有多种选择,具体采用哪种还要看实际项目,如果想看源码的,请看源码:

一定要边看代码,边看手册,才能真正领悟其中的真谛

GD32F30x系列ADC源码,对初学者参考价值巨大,(非常详细篇)万字源码

ADC结局总结

ADC内容繁多,而且实际运行中还配合DMA(直接存储器访问)和RCU(复位时钟单元)等一起使用,ADC外设时钟一般和APB时钟相连,而APB和AHB时钟相连,环环相扣,初始化时一定要配置妥当,更多的经验我们在实战中吸取吧!

-

相关阅读:

如何实现Git Push之后自动部署到服务器?

随手笔记(二)

javaweb03-js基础

科普:什么是视频监控平台?如何应用在场景中?

神经网络模型压缩综述

Linux每日智囊

片段与活动的交互

查找算法【平衡二叉树】 - 平衡二叉树的删除

el-table相同的值合并单元格+多级表头

使用Python进行自然语言处理:情感分析

- 原文地址:https://blog.csdn.net/m0_45463480/article/details/128062193