-

verilog实现分频(奇数分频,偶数分频,且50%占空比,通用版本)

大家好,最近写了几个分频器。实现奇数分频和偶数分频效果,且占空比满足50%,代码已经经过测试,需要可自取。感谢关注。

一、上代码

- `timescale 1ns / 1ps

- //

- module CLK_DIV_ODDandEVEN50P

- #(

- parameter Multiple = 11 //Multiple表示的是倍频倍数。

- )

- (

- input sys_rst,

- input sys_clk,

- output clk_div ,

- output [15:0] cnt

- );

- wire odd ;

- wire even ;

- assign odd = (Multiple[0]==1'b1)?1'b1:1'b0; //奇数判断

- assign even = (Multiple[0]==1'b0)?1'b1:1'b0; //偶数判断

- assign clk_div = (odd)?clk_odd: (even)?clk_even:0; //将奇数或者偶数分频结果输出

- reg [15:0] cnt=16'b0;

- always@(posedge sys_clk)

- begin

- if(sys_rst) //复位信号,高有效

- begin

- cnt <= 16'b0;

- end

- else

- if(cnt == (Multiple -1))

- begin

- cnt <=16'b0;

- end

- else

- begin

- cnt <= cnt + 1'b1 ;

- end

- end

- //--------奇数分频过程------start---------//

- reg clk_oddP=1'b0;

- always@(posedge sys_clk)

- begin

- if(sys_rst) //复位信号,高有效

- begin

- clk_oddP <= 1'b0;

- end

- else

- if(cnt <= (Multiple /2 ))

- begin

- clk_oddP <= 1'b0 ;

- end

- else

- begin

- clk_oddP <= 1'b1 ;

- end

- end

- reg clk_oddN=1'b0;

- always@(negedge sys_clk)

- begin

- if(sys_rst) //复位信号,高有效

- begin

- clk_oddN <= 1'b0 ;

- end

- else

- if(cnt <= (Multiple /2))

- begin

- clk_oddN <=1'b0;

- end

- else

- begin

- clk_oddN <= 1'b1 ;

- end

- end

- wire clk_odd ;

- assign clk_odd = clk_oddP | clk_oddN ; //通过或运算实现50%占空比。

- //--------奇数分频过程------end---------//

- //--------偶数分频过程------start---------//

- reg clk_even=1'b0;

- always@(posedge sys_clk)

- begin

- if(sys_rst) //复位信号,高有效

- begin

- clk_even <= 1'b0;

- end

- else

- if(cnt <= (Multiple /2 -1))

- begin

- clk_even <= 1'b0 ;

- end

- else

- begin

- clk_even <= 1'b1 ;

- end

- end

- //--------偶数分频过程------end---------//

- endmodule

二、上仿真代码

- `timescale 1ns / 1ps

- /

- module CLK_DIV_ODDandEVEN50P_TB;

- // Inputs

- reg sys_rst;

- reg sys_clk;

- // Outputs

- wire clk_div;

- wire [15:0] cnt;

- // Instantiate the Unit Under Test (UUT)

- CLK_DIV_ODDandEVEN50P uut (

- .sys_rst(sys_rst),

- .sys_clk(sys_clk),

- .clk_div(clk_div),

- .cnt(cnt)

- );

- initial begin

- // Initialize Inputs

- sys_rst = 1;

- sys_clk = 0;

- // Wait 100 ns for global reset to finish

- #100;

- sys_rst = 0;

- forever #500 sys_clk=~sys_clk;

- // Add stimulus here

- end

- endmodule

三、上仿真结果

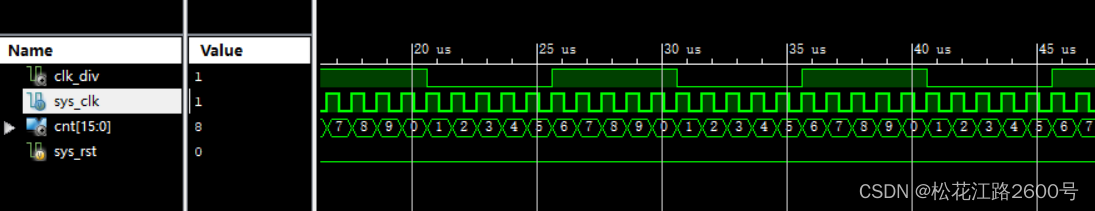

图1:10分频50%占空比效果(multiple=10)

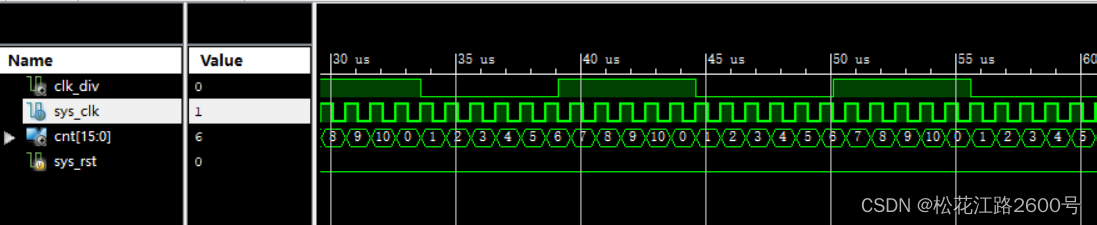

图2:11分频50%占空比效果(multiple=11) 由图1和图2可知,仅仅通过带边变量multiple的值可以实现不同分频,且满足50%占空比。其中:

①sys_clk是系统时钟,本代码中作为被分频时钟。

②clk_div是分频后时钟。

③cnt是计数器,作为分频计数使用。

④sys_rst是复位信号,高有效。

感谢关注。

-

相关阅读:

数据结构刷题(三十三):完全背包最小值情况。322. 零钱兑换、279. 完全平方数

MIT 6.S081学习笔记(第一章)

Docker安装RabbitMQ

云原生k8s之Pod基础概念

LeetCode题解:171. Excel 表列序号,哈希表,TypeScript,详细注释

【JVM】synchronized锁升级的过程

TYFLOW学习17

Springboot、Tomcat+skywalking 链路追踪、日志收集配置

OpenGL ES入门教程(二)之绘制一个平面桌子

【华为校招】【校招】【Java】单词搜索(DFS)

- 原文地址:https://blog.csdn.net/weixin_47032674/article/details/128111038