-

高精度定时器学习(通过官方手册学习)

功能描述

一般说明

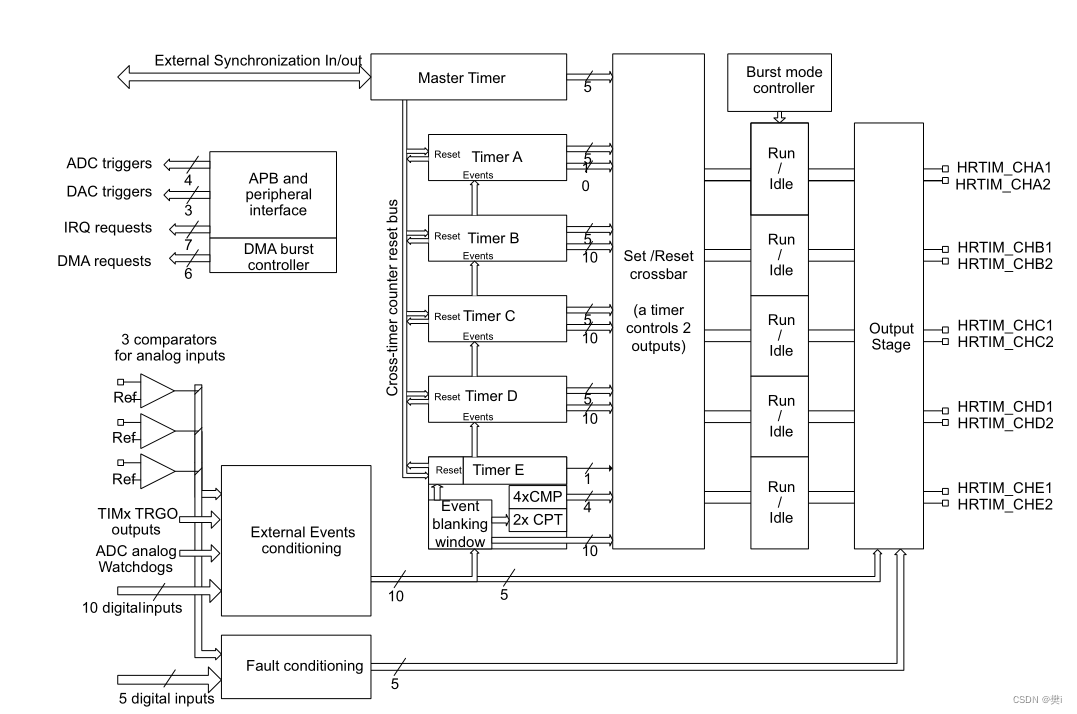

HRTIM可以划分为几个模块:

•主定时器

•计时单元(定时器A至定时器E)

•输出级

•突发模式控制器

•所有定时器共享的外部事件和故障信号调节逻辑

•系统接口

主计时器基于16位递增计数器。它可以通过4个比较单元设置/重置10个输出中的任何一个,并向5个定时器单元提供同步信号。其主要目的是让定时器单元由唯一的源控制。交错降压转换器是一个典型的应用示例,其中主定时器管理多个单元之间的相移。

定时器单元独立工作或与包括主定时器在内的其他定时器耦合工作。每个计时器包含两个输出的控制。输出设置/复位事件由定时单元比较寄存器或来自主定时器、其他定时器或外部事件的事件触发。输出级具有多种功能

•当2个输出配置为互补PWM模式时增加死区时间

•在调制信号上增加载波频率

•通过异步将输出设定为预定义的安全水平来管理故障事件

突发模式控制器可以在轻负载操作的情况下接管一个或多个定时器的控制。可以对脉冲串长度和周期以及输出的空闲状态进行编程。

外部事件和故障信号调节逻辑包括:

输入选择MUX(例如,用于为给定外部事件通道选择数字输入或片上源)

•极性和边缘灵敏度编程

•数字滤波(10个通道中的5个)系统接口允许HRTIM与MCU的其余部分交互:

•向CPU发出中断请求

•DMA控制器自动访问存储器,包括HRTIM特定突发模式•ADC和DAC转换器触发器HRTIM寄存器分为7组

•主定时器寄存器

•定时器A到定时器E寄存器

•所有定时器单元共享的功能的通用寄存器

注:作为书写惯例,文本和寄存器中对5个计时单位的引用使用“x”字母进行概括,其中x可以是从a到E的任何值。

计时器的框图如图244所示。

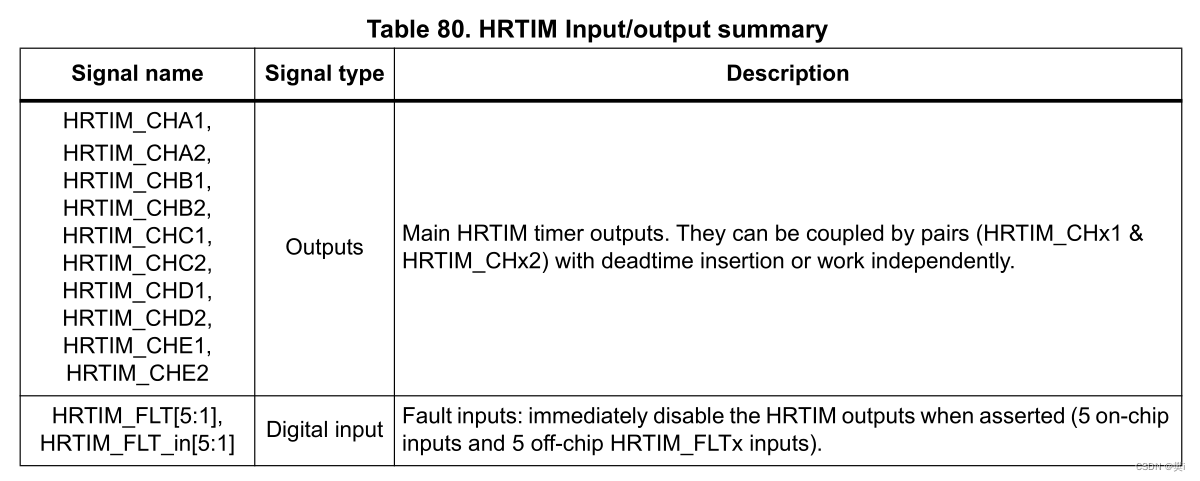

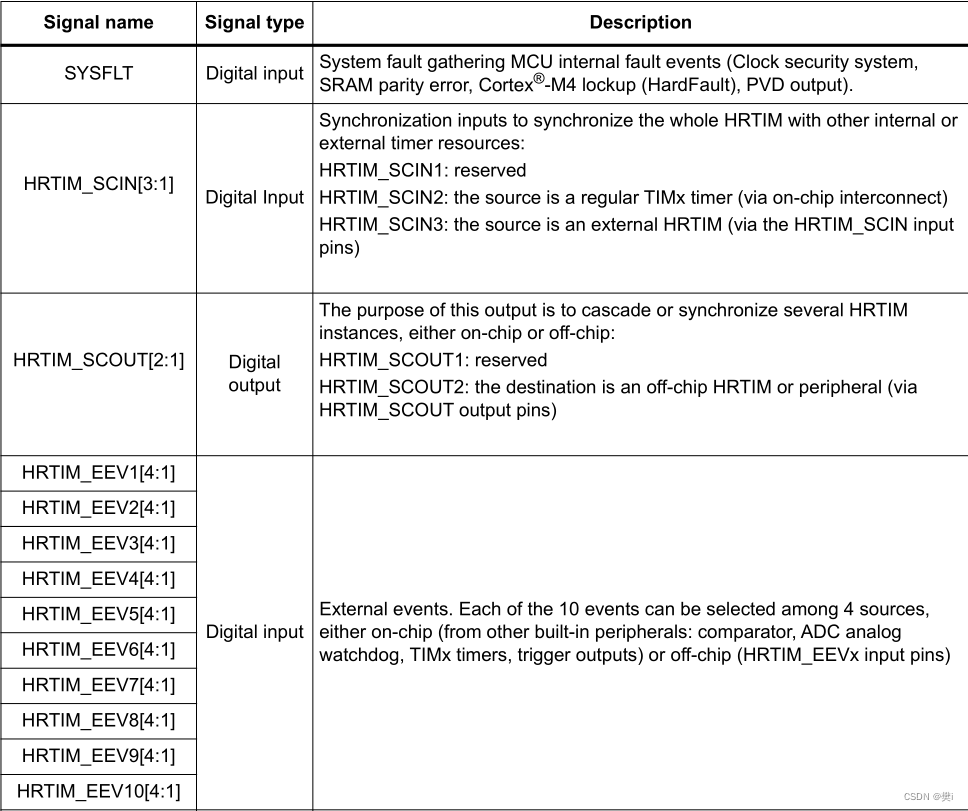

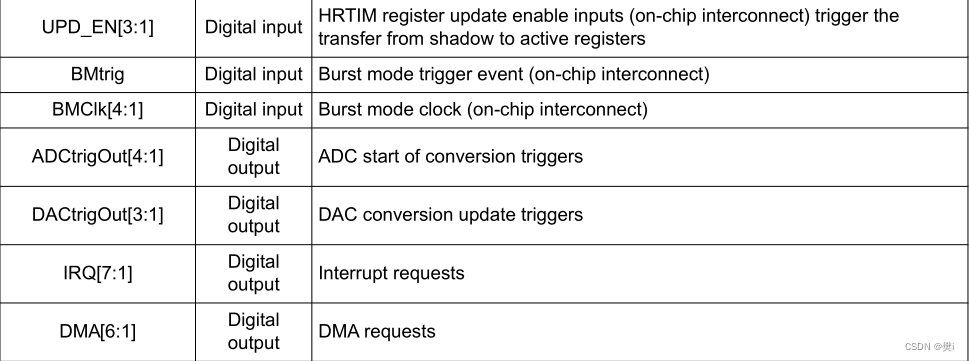

HRTIM引脚和内部信号

下表总结了片上和片外HRTIM输入和输出。

时钟

HRTIM必须由HRTIM系统时钟提供,以提供全分辨率。使用边缘定位逻辑将HRTIM时钟周期均匀地划分为多达32个中间步骤。HRTIM中存在的所有时钟都是从该参考时钟导出的。

术语的定义

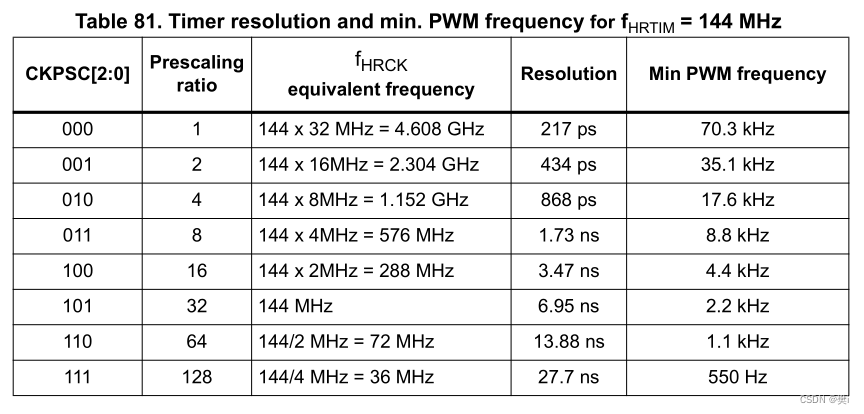

f HRTIM:主HRTIM时钟。所有后续时钟都是派生的,并与该源同步。

f HRCK:高分辨率等效时钟。考虑到f HRTIM时钟周期除以32,它相当于144 x 32=4.608 GHz的频率。

f DTG:死区时间发生器时钟。为方便起见,本文档中仅使用了t DTG周期(t DTG=1/f DTG)。

f CHPFRQ:斩波级时钟源。

f 1STPW:定义斩波器模式下初始脉冲长度的时钟源。为方便起见,本文件中仅使用t 1STPW周期(t 1STSW=1/f 1STPW)。

f BRST:突发模式控制器计数器时钟。

f采样:采样故障或外部事件输入所需的时钟。

f FLTS:从f HRTIM导出的时钟,该时钟用作f SAMPLEING的源,用于过滤故障事件。

f EEVS:从f HRTIM派生的时钟,该时钟用作f SAMPLEING的源以过滤外部事件。

定时器时钟和预分频器

HRTIM中的每个计时器都有自己的时钟预分频器,可以调整计时器分辨率。

高分辨率可用于边缘定位、PWM周期调整和外部触发脉冲持续时间。

高分辨率不适用于以下功能

•计时器读取和写入访问

•捕获单元

对于低于32的时钟预缩放比(CKPSC[2:0]:5),计数器和捕获寄存器的最低有效位不重要。最低有效位无法写入(仅限计数器寄存器),读取时返回0。

例如,如果CKPSC[2:0]=2(预编码4),将0xFFFF写入计数器寄存器将产生0xFFF0的有效值。相反,0xFFFF和0xFFF0之间的任何计数器值将被读取为0xFFF0。

初始化在启动时,在写入比较寄存器和周期寄存器之前,必须首先初始化预分频器位字段。一旦定时器启用(HRTIM_MCR寄存器中设置了MCEN或TxCEN位),则无法修改预分频器。

当启用多个定时器时,预分频器与首先启动的定时器的预分频同步。

死区时钟

死区时间预分频器由f HRTIM/8/2(DTPRSC[2:0])提供,用HRTIM_DTxR寄存器中的DTPRSC[2]位编程。

对于f HRTIM=144MHz,t DTG的范围从868ps到6.94ns。

斩波级时钟

斩波级时钟源f CHPFRQ源自f HRTIM,分频因子范围为16至31,因此对于f HRTIM=144 MHz,562.5 kHz<=f CHPFR Q<=9 MHz。

t 1STPW是斩波器模式下初始脉冲的长度,用HRTIM_CHPxR寄存器中的STRPW[3:0]位编程,如下:t 1STSW=(STRPW[3]+1)x 16 x t HRTIM。

它使用f HRTIM/16作为时钟源(f HRTIM=144 MHz时为9 MHz)。

突发模式预

分频器突发模式控制器计数器时钟fBRST可以由几个源提供,其中一个源于fHRTIM。

在这种情况下,f BRST的范围从f HRTIM到f HRTIM/32768(f HRTIM=144 MHz时为4.4 kHz)。

故障输入采样时钟故障输入噪声抑制滤波器具有由f sampling定义的时间常数,该时间常数可以是f HRTIM或f FLTS。

f FLTS是从f HRTEM导出的,并且对于f HRTEM=144 MHz。

外部事件输入采样时钟故障输入噪声抑制滤波器具有用f SAMPLEING定义的时间常数,其可以是f HRTIM或f EEVS。

f EEVS从f HRTIM导出,并且对于f HRTIM=144 MHz。Timer A…E timing units

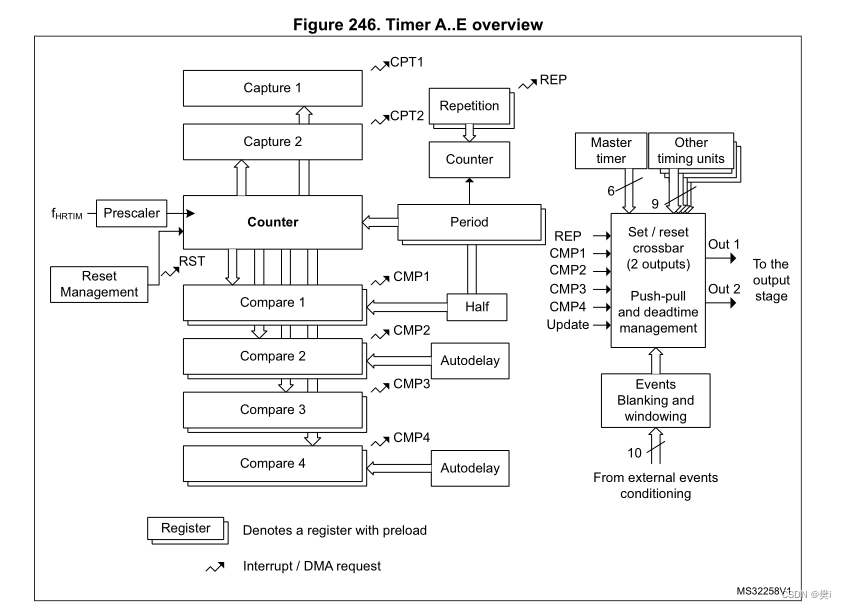

如图所示,HRTIM嵌入5个相同的计时单元,由16位递增计数器和自动重新加载机制组成,以定义计数周期、4个比较和2个捕获单元。

每个单元包括2个输出的所有控制功能,因此它可以作为独立定时器运行。

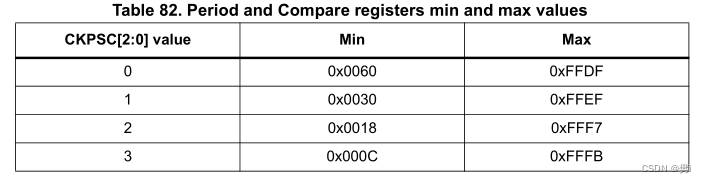

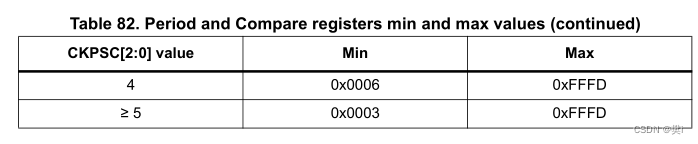

周期和比较值必须在与高分辨率实施相关的下限和上限内,如表82所示:

•最小值必须大于或等于f HRTEM时钟的3个周期

•最大值必须小于或等于f hrTEM时钟的0xFFFF-1个周期

注意:大于周期寄存器值的比较值不会生成比较匹配事件。

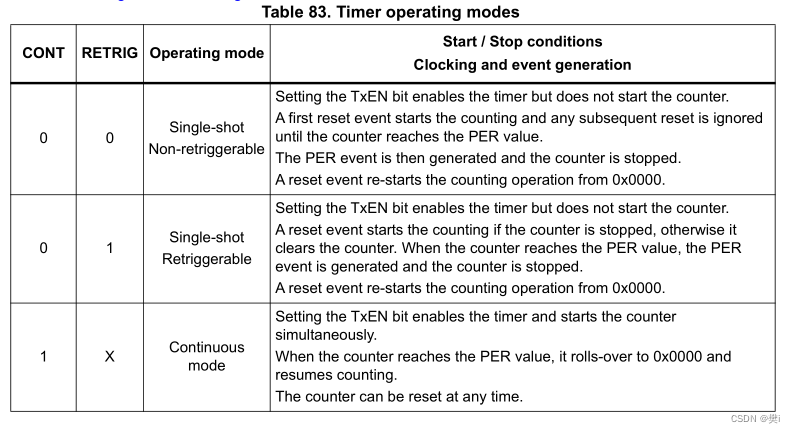

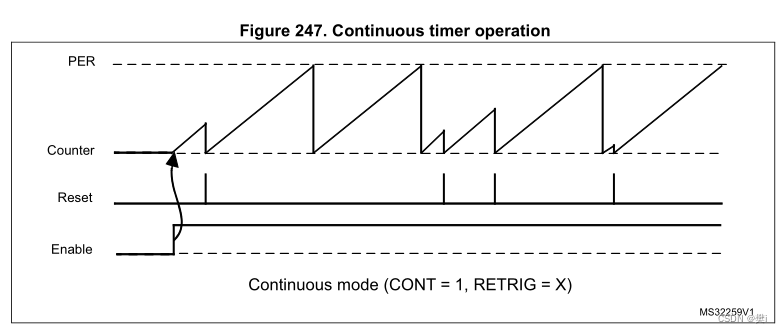

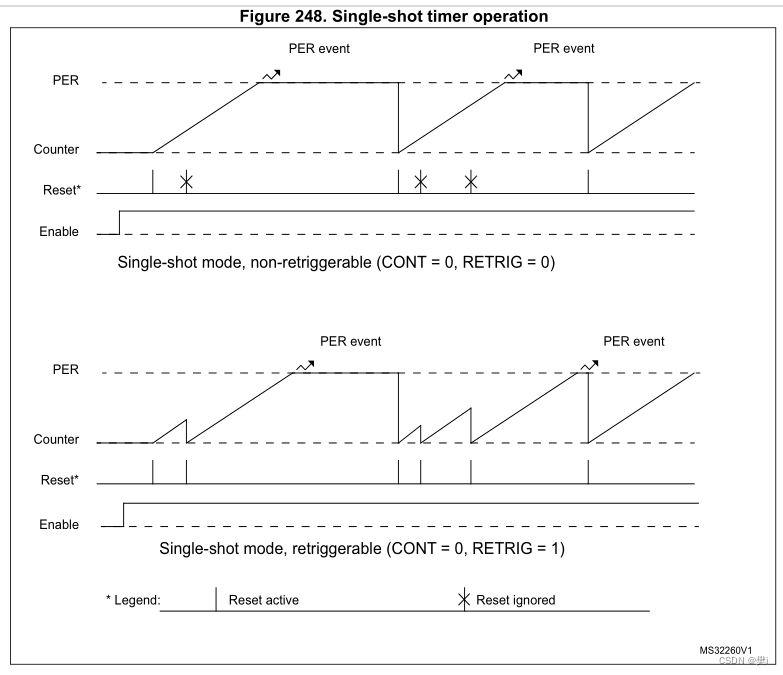

计数器操作模式定时器A…E可以在连续(自由运行)模式或单触发模式下操作,其中通过复位事件开始计数,使用HRTIM_TIMxCR控制寄存器中的CONT位。额外的RETRIG位允许您选择单次触发操作是可再触发还是不可再触发。表83、图247和图248总结了操作细节。

可以随时清除TxEN位以禁用计时器并停止计数。

翻转事件

当计数器在连续模式下达到HRTIM_PERxR寄存器中设置的周期值后返回0时,会生成计数器翻转事件。

此事件在HRTEM中用于多种用途:

–设置/重置输出

–触发寄存器内容更新(从预加载转移到活动)

–触发IRQ或DMA请求

–用作突发模式时钟源或突发启动触发器

–用作ADC触发器

–减少重复计数器

如果计时器启动时初始计数器值高于周期值,或者如果在计数器已经高于该值时设置了新的周期,则计数器不会复位:它将在最大周期值时溢出,重复计数器不会递减。

Timer reset

计时单位计数器的重置可由HRTIM_RSTxR寄存器中最多30个同时选择的事件触发,这些事件来自以下来源:

•计时单位:比较2,比较4和更新(3个事件)

•主计时器:重置和比较1…4(5个事件)。

•外部事件EXTEVNT1…10(10个事件)

•所有其他计时单位(例如计时器A的计时器B…e):比较1、2和4(12个事件)

可以同时选择多个事件来处理多个重置源。在这种情况下,对多个重置请求进行“或”运算。当在相同的f HRTEM时钟周期内产生2个计数器重置事件时,将考虑最后一次计数器重置。

此外,可以使用HRTIM_CR2寄存器中的TxRST位对计数器进行软件复位。这些控制位被分组到单个寄存器中,以允许同时重置几个计数器。

仅当相关计数器启用(TxCEN位设置)时,才会考虑重置请求。

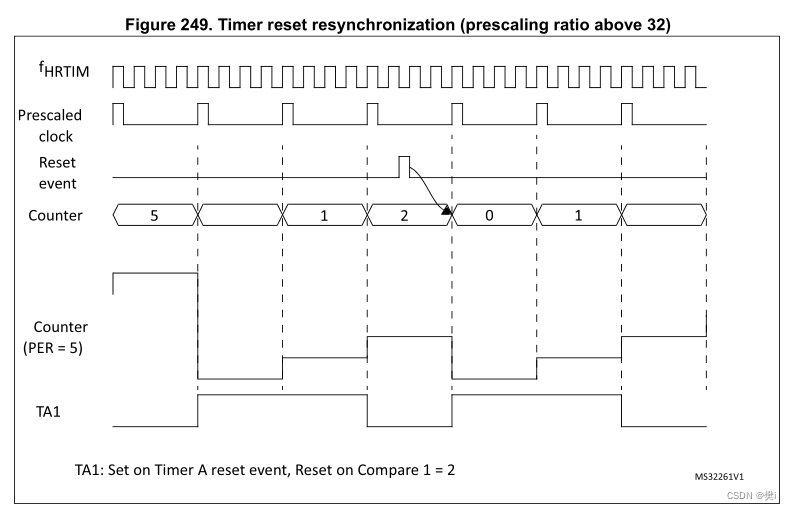

当f HRTIM时钟预缩放比高于32(计数周期高于f HRTIM)时,计数器复位事件被延迟到预缩放时钟的下一个有效边沿。这允许在输出转换与复位事件同步时保持无抖动波形生成(通常是恒定Ton时间转换器)。

图249显示了时钟预缩放比为128(f HRTIM除以4)时如何处理复位

重复计数器一种常见的软件实践是在达到周期值时产生中断,以便在下一个周期开始之前留出最大的处理时间。重复计数器的主要目的是通过将开关频率和中断频率解耦来调整周期中断率和卸载CPU。

计时单元有一个重复计数器。此计数器无法读取,但只能用HRTIM_REPxR寄存器中的自动重新加载值编程。

当定时器启用(TXCEN位设置)时,重复计数器用HRTIM_REPxR寄存器的内容初始化。一旦定时器被启用,无论何时计数器被清除,无论是由于复位事件还是计数器翻转,重复计数器都会减少。当它达到零时,如果启用(HRTIM_DIER寄存器中的REPIE和REPDE位),则发出REP中断或DMA请求。

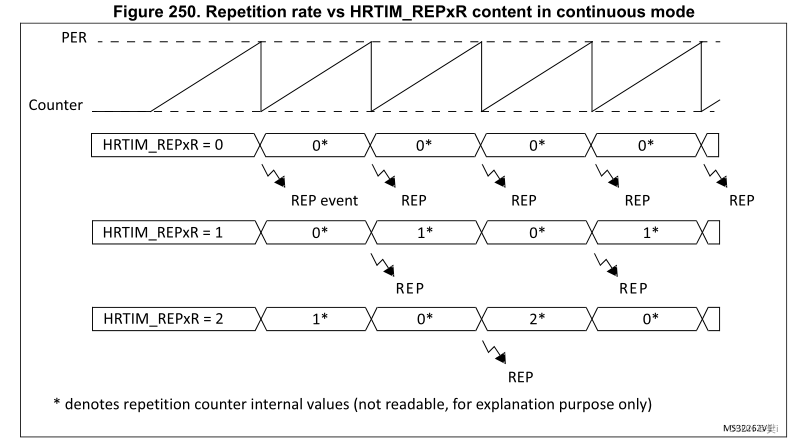

如果HRTIM_REPxR寄存器设置为0,则为每个周期生成一个中断。对于大于0的任何值,在(HRTIM_REPxR+1)个周期之后生成REP中断。图250显示了连续模式下各种值的重复计数器操作。

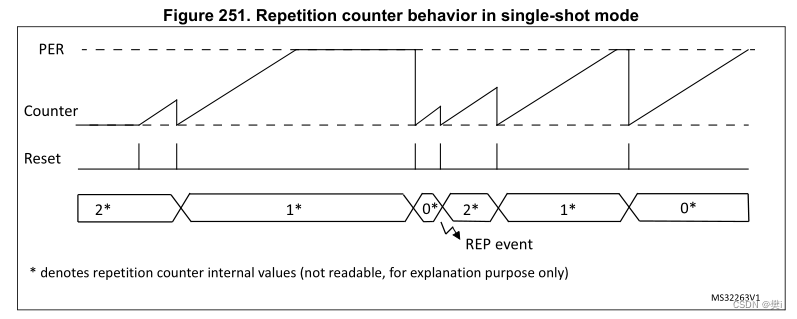

当计数器在连续或单触发模式下达到周期值(可变频率操作)之前复位时,也可以使用重复计数器(下图251)。重置导致重复计数器递减,计数器启用后的第一次启动除外(TxCEN位设置)

来自HRTIM_SCIN[3:1]源的重置或启动事件导致重复次数与任何其他重置一样减少。然而,在SYNCIN启动的单触发模式下(在HRTIM_TIMxCR寄存器中设置SYNCSTRTx位),重复计数器将仅在周期后的第一个复位事件时递减。在HRTIM_SCIN[3:1]输入上的新请求重新启动计数器之前,任何后续重置都不会改变重复计数器

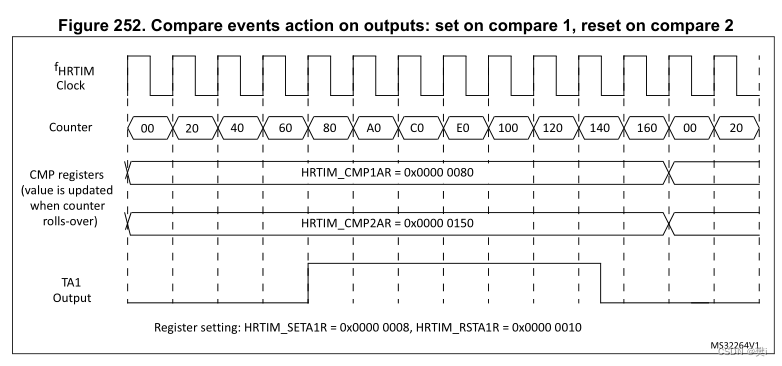

设置/重置横杆

“设置”事件对应到输出活动状态的转换,而“重置”事件对应于到输出非活动状态的转变。

波形的极性在输出级中定义,以适应正或负逻辑外部分量:对于正极性(POLx=0),激活电平对应于逻辑电平1,对于负极性(POLx=1),激活级别对应于逻辑级别0。

每个定时单元处理两个输出的设置/复位交叉开关。这2个输出可通过最多32个事件进行设置、重置或切换,这些事件可从以下源中选择:

–计时单位:周期、比较1…4、寄存器更新(6个事件)

–主计时器:周期、比较1…4、HRTIM同步(6个事件)

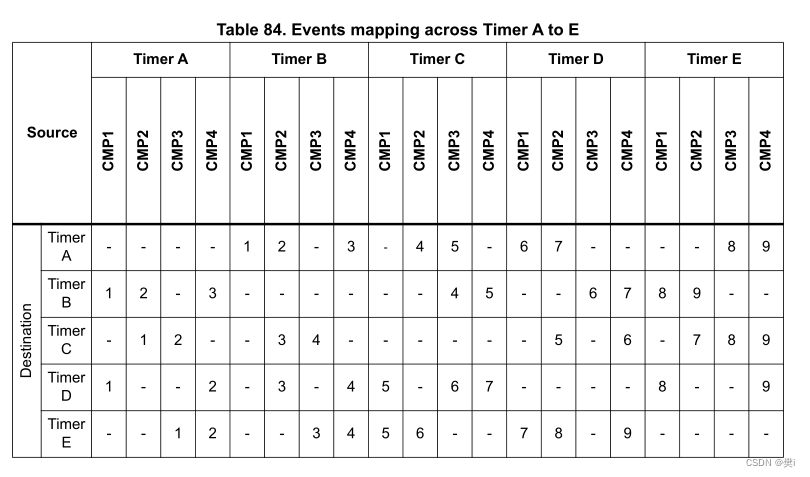

–所有其他计时单位(例如定时器A的定时器B…e):TIMEVNT1…9(9个事件如表84所述)

–外部事件EXTEVNT1…10(10个事件)

–软件强制(1个事件)

事件源被“或”运算,可以同时选择多个事件。

每个输出由两个32位寄存器控制,一个用于设置(HRTIM_SETxyR),另一个用于复位(HRTIM _RSTxyR)。其中x表示计时单位:A.E,y表示输出1或2(例如HRTIM_RETA1R、HRTIM_MSTC2R…)。

如果为设置和重置选择了相同的事件,它将切换输出。不可能在每t HRTEM周期内切换输出状态一次以上:如果在同一周期内发生两次连续切换事件,则只考虑第一次。

只有当计数器启用(TxCEN位设置)时,才会考虑设置和重置请求,除非软件强制请求允许在定时器启动时前置输出。

表84总结了可用于设置和重置输出的其他定时单元的事件。该数字对应于寄存器中列出的计时器事件(如TIMEVNTx),空位置表示不可用事件。

例如,计时器A的输出可以通过以下事件设置或重置:计时器B比较1、2和4、计时器C比较2和3……和计时器E比较3将在HRTIM_SETA1R中列为TIMEVNT8。

更新时设置/重置事件更新时设置或重置事件以低分辨率完成。当CKPSC[2:0]<5时,高分辨率延迟被设置为其最大值,以便与其他比较设置/重置事件相比,更新时的设置/重置将始终滞后,抖动在f HRTIM时钟周期的0和31/32之间变化。

半模式

该模式旨在生成具有固定50%占空比和可变频率的方波信号(通常用于使用谐振拓扑的转换器)。它允许在编程新周期时自动将占空比强制为周期值的一半。

通过将HRTIM_TIMxCR寄存器中的半位写入1来启用该模式。当写入HRTIM_PERxR寄存器时,它会自动更新比较1值与HRTIM_PER xR/2值。

生成方波的输出必须编程为CMP1事件上有一个转换,周期事件上有1个转换,如下所示:–HRTIM_SETxyR=0x0000 0008,HRTIM_RSTxyR=0x0000 00004,或–HRIM_SETxyR=0x0000 0004,HRIM_RSTxyR=0x00000 0008 HALF模式覆盖HRTIM_CMP1xR寄存器的内容。对HRTIM_PERxR寄存器的访问只会导致比较1内部寄存器被更新。用户可访问的HRTIM_CMP1xR寄存器未更新为HRTIM_PERxR/2值。

当预加载被启用(PREEN=1,MUDIS,TxUDIS)时,比较1活动寄存器在更新事件上被刷新。如果预加载被禁用(PREEN=0),则一旦写入HRTIM_PERxR,比较1活动寄存器就会更新。

当启用HALF模式时,周期必须大于或等于f HRTIM时钟的6个周期(如果CKPSC[2:0]=0,则为0xC0;如果CKPSC[2:0]=1,则为x60;如果CKPSC[2:0]=2,则应为0x30;…)。

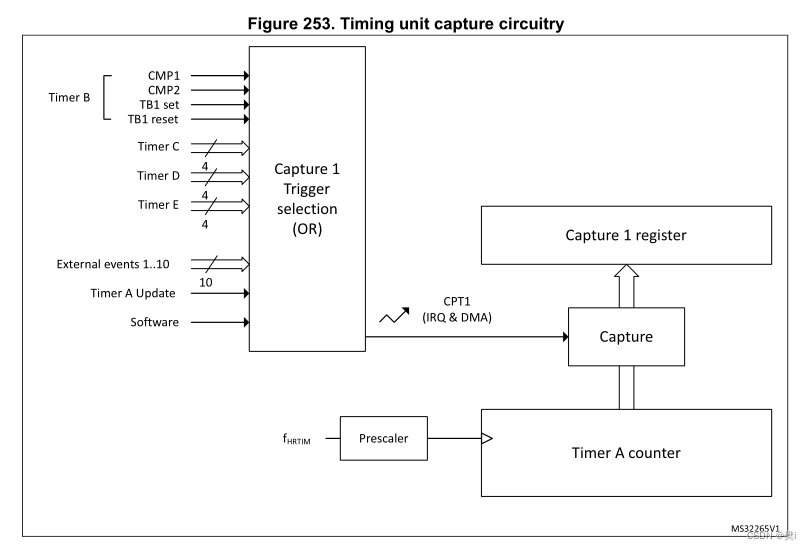

捕获

计时单元能够捕获由内部和外部事件触发的计数器值。其目的是:•测量事件到达时间或发生间隔•在自动延迟模式下更新比较2和比较4值(请参阅自动延迟模式)。

捕获以f HRTIM分辨率完成:对于低于32的时钟预缩放比(CKPSC[2:0]<5),寄存器的最低有效位不重要(读为0)。

定时器有两个捕获寄存器:HRTIM_CPT1xR和HRTIM_CPT2xR。捕获触发器在HRTIM_CPT1xCR和HRTIM_CPT 2xCR寄存器中编程。

计时单位计数器的捕获可由以下源中的多达28个事件触发,这些事件可在HRTIM_CPT1xCR和HRTIM_CPT2xCR寄存器中同时选择:

•外部事件EXTEVNT1…10(10个事件)

•所有其他计时单位(例如定时器A的定时器B…e)

比较1、2并输出1个设置/重置事件(16个事件)

计时单位:更新(1个事件)

软件捕获(1个)

可以同时选择多个事件来处理多个捕获触发器。在这种情况下,并发的触发器请求被“或”运算。当在HRTIM_TIMxDIER寄存器中设置CPTxIE和CPTxDE位时,捕获可以生成中断或DMA请求。

电路不会防止过度捕获:即使未读取前一个值,或者未清除捕获标志,也会触发新的捕获。

-

相关阅读:

谱瑞PS186|替代PS186方案|TypeC转HDMI4K视频转换方案设计

Flutter 必备知识点

Spring监听器-spring源码详解(五)

基于opencv+tensorflow+神经网络的智能银行卡卡号识别系统——深度学习算法应用(含python、模型源码)+数据集(一)

eCapture环境搭建编译|Android https明文抓包

微信公众号-遇到的问题

I2C、SPI、CAN、PCIe 对比

【数据结构】栈

log日志异常堆栈打印的正确姿势

多寄存器内存访问指令的寻址方式

- 原文地址:https://blog.csdn.net/weixin_42914004/article/details/127891576