-

逻辑功能的几种基本描述方法

逻辑功能的几种基本描述方法

1.数据流描述(用“assign”连续赋值语句)数据流描述方式类似于布尔方程,既含有逻辑单元的结构信息,又隐含地表示某种行为。“assign”语句一般用于组合逻辑的赋值,称为持续赋值方式。这种方法简单,只需将逻辑表达式放在关键字“assign”后即可。如:

assign F=~((A&B)|(C&D))。- 1

2.结构描述

结构描述是通过实例进行描述的。将Verilog 预定义的基元实例嵌入到语言中,监控实例的输入,一旦其中任何一个发生变化,便重新运算并输出。在Verilog语言中,可通过调用如下元件的方式来描述电路的结构:

(1)调用Verilog内置门元件(门级结构描述);

(2)调用开关级元件(开关级结构描述);(3)用户定义元件UDP(门级结构描述);(4)模块实例(创建层次结构)。调用元件的方法类似于在电路图输入方式下调入库元件一样,键入元件的名字和引脚的名字即可。要求每个实例元件的名字必须是唯一的。如:and myand4(f,a,b,c,d); //调用门元件,定义了一个四输入与门 and c3(out,a,b,c) //三输入与门,名字为c3- 1

- 2

- 3

- 4

3.行为描述

行为描述方式是一种使用高级语言的方法。它和用软件编程语言描述没有什么不同,具有很强的通用性和有效性。它是通过行为实例来实现的。

(1)initial语句:一般用于仿真中的初始化,仅执行一次。

(2)always 语句:语句不断重复执行,含义是一旦赋值给定,仿真器便等待变量的下一次变化,有无限循环之意。4.混合描述

在模块中,上述逻辑功能的描述方法可以混合使用,即模块描述中可以包含实例化的门、模块实例化语句、连续赋值语句以及always语句和initial语句的混合。它们之间可以相互包含。来自always语句和initial语句的值能够驱动门或开关,而来自于门或连续赋值语句的值能够反过来用于触发always语句和initial语句。

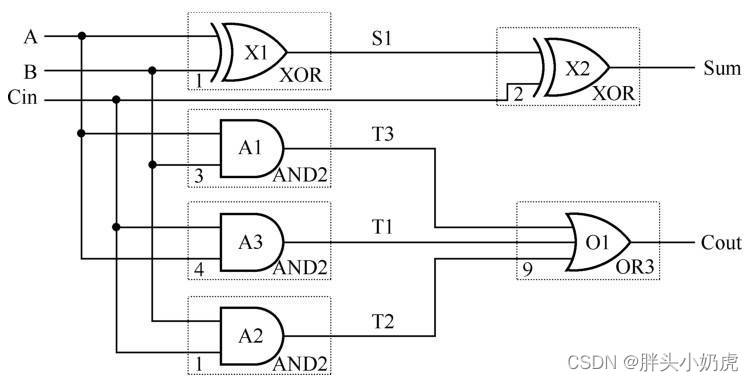

下面是混合设计方式的1位全加器实例(电路示意图如图8-1所示)。

【例】1位全加器module Add1(A,B,Cin,Sum,Cout); input A,B, Cin; output Sum, Cout; reg Cout; reg T1,T2,T3; wire S1; xor X1(S1, A, B); // 门实例语句。 always @( A or B or Cin) // always 语句 begin T1 = A&Cin; T2 = B&Cin; T3 = A&B; Cout =(T1|T2)|T3; end assign Sum = S1^Cin; // 连续赋值语句。 endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

只要A或B上有事件发生,门实例语句即被执行。只要A、B或C i n上有事件发生,就执行always语句,并且只要S1或Cin上有事件发生,就执行连续赋值语句。

-

相关阅读:

小程序中用于跳转页面的5个api是什么和区别

ROS自学笔记十八:ModuleNotFoundError: No module named ‘serial‘

使用开源Cesium+Vue实现倾斜摄影三维展示

Google Earth Engine(GEE)——利用sentinel-2数据进行农作物提取分析

西瓜书-2.4模型评估与选择

java使用MD5加密

C#调用C++动态库接口函数和回调函数方法 后续

程序员的颈椎病怎么办?

Python爬虫|基础知识点详细汇总(requests、urllib、re、bs4、xpath、多线程、协程、数据保存、selenium)

【图论——第七讲】Pirm算法求最小生成树问题及其堆优化

- 原文地址:https://blog.csdn.net/weixin_55804957/article/details/127729894