-

静态时序分析简明教程(五)]生成时钟的sdc约束方法

生成时钟的sdc约束方法

一、写在前面

一个数字芯片工程师的核心竞争力是什么?不同的工程师可能给出不同的答复,有些人可能提到硬件描述语言,有些人可能会提到对于特定算法和协议的理解,有些人或许会提到对于软硬件的结合划分,作者想说,这些说法,其实对也不对,硬件描述语言,翻来覆去无非是always和assign这几个语句的反复使用,而一些基础的协议算法,深究起来其实也并不复杂,于作者而言,在常规的技能以外,有两项额外的技能颇为重要,其中之一便为sdc/STA的分析能力,它的重要之处在于作为桥梁建立了前端和后端的连接,虽然对于DE工程师而言,初版交付的sdc往往不甚准确,也没有办法通过这份sdc生成一份无误的timing report,但sdc的内容体现却是完完整整的将时序约束从行为级的描述映射到了gate level这样一个真实的电路层次上面。

写此专栏,一为学习记录,二为交流分享,以犒粉丝读者。1.1 快速导航链接·

静态时序分析简明教程(一)绪论

静态时序分析简明教程(二)基础知识:建立保持时间,违例修复,时序分析路径

静态时序分析简明教程(三)备战秋招,如何看懂一个陌生的timing report

静态时序分析简明教程(四)时钟常约束

静态时序分析简明教程(五)生成时钟

静态时序分析简明教程(六)端口延迟

静态时序分析简明教程(七)完整端口约束

静态时序分析简明教程(八)虚假路径

静态时序分析简明教程(九)多周期路径

静态时序分析简明教程(十)组合电路路径

静态时序分析简明教程(十一)模式分析与约束管理

静态时序分析简明教程(十二)浅议tcl语言二、生成时钟

在静态时序分析简明教程(四)时钟常约束中,我们讨论了如何创建和标识一个普通的时钟信号,按照以下的BNF(巴斯科范式)来进行。

create_clock -period period_value [source_objects] [-name clock_name] [-waveform edge_list] [-add] [-comment comment_string]- 1

- 2

- 3

- 4

- 5

- 6

而在常规的时钟约束以外,另一个我们经常讨论的问题,则是时钟的分频和倍频问题,即“生成时钟”问题,它的BNF(巴斯科范式)如下,而生成时钟的母命令为“create_generated_clock”

create_generated_clock [source_objects] -source clock_source_pin [-master_clock master_clock_name] [-edges edge_list] [-divide_by factor] [-multiple_by factor] [-invert] [-edge_shift shift_list] [duty_cycle percent] [-combinational] [-add] [-comment comment_string]- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

2.1 标识时钟源

与时钟常规约束类似,通过类似以下的命令来进行标识,详情可见静态时序分析简明教程(四)时钟常约束中的3.2节内容,通过以下的命令,我们知道生成的时钟,是作用于何处

[get_ports A] [get_nets N] [get_pins FF/P]- 1

- 2

- 3

作用于何处知道后,我们也需要知道,生成时钟,来源于何处,通过 -souce和标识时钟源的以下组合, 我们可以明确新的时钟来源于哪一个老时钟

-source [get_ports A] [get_nets N] [get_pins FF/P]- 1

- 2

- 3

2.2 时钟命名

与时钟常规约束类似,详情可见静态时序分析简明教程(四)时钟常约束中的3.3节内容,通过-name的形式设定名称。

2.3 设定生成时钟的特性

生成时钟的特性,其实就是指生成的新时钟,相较于原来的老时钟的如“分频、倍频、相位变化”等内容的改变,我们有以下的三种方法来约束新时钟的相关特性

2.3.1 -edges

-edges是通过描述对应源时钟边沿(上升沿和下降沿)的整数列表,来描述生成时钟的特性,我们需要至少三个整数,才能描述新时钟的周期特性(两个上升沿,一个下降沿;或者两个下降沿,一个上升沿)假如不是三个整数,想要描述更复杂的时钟周期,我们也需要奇数个整数,来描述新时钟的周期特性

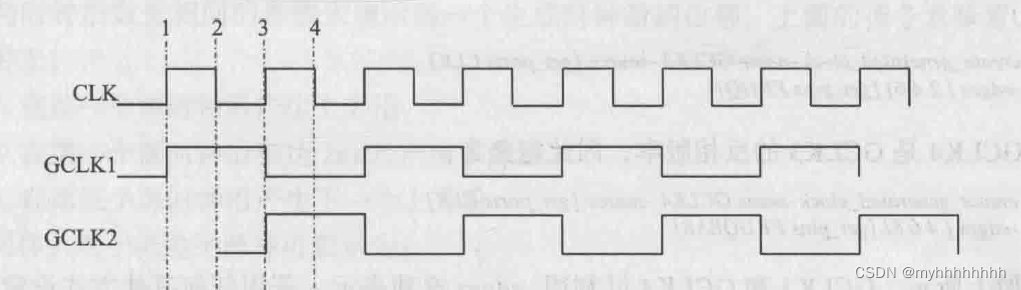

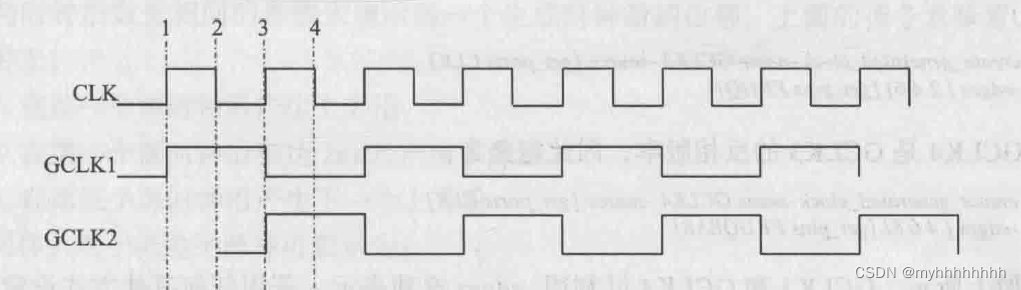

比如上面的这幅图片,加入我们想要描述GCLK1的时钟特性的话,我们可以发现,GCLK1的上升沿,对齐CLK的1号边沿,下降沿,对齐CLK的3号边沿,第二个上升沿,对应CLK的5号边沿(即一个完整周期需要三个边沿)因此我们的SDC需要约束为以下:

create_generated_clock -name GCLK1 -source [get_ports CLK] -edges {1 3 5} [get_pins FF1/Q] #第一个出现的-source [get_ports CLK],是为了标识:生成的时钟来源于哪一个老时钟 #第二个出现的 [get_pins FF1/Q],是为了将生成时钟映射到具体的电路端口/引脚上- 1

- 2

- 3

- 4

2.3.2 -divide_by

通过-divide_by,我们可以描述分频信号,假如CLK是源时钟,GCLK1是生成时钟,我们可以通过如下的描述进行sdc约束

create_generated_clock -name GCLK1 -source [get_ports CLK] -divide_by 2 [get_pins FF1/Q] #通过这种形式,我们描述了相较于CLK的二分频新的信号GCLK1- 1

- 2

- 3

2.3.3 -invert

除此以外,我们还可以通过-invert的形式描述取反的时钟波形

create_generated_clock -name GCLK2 -source [get_ports CLK] -invert -divide_by 2 [get_pins FF1/Q] #通过这种形式,我们描述了相较于CLK的同时进行二分频和反相操作的新的信号GCLK2- 1

- 2

- 3

- 4

2.3.4 -multiply_by

通过-multiply_by,我们可以描述倍频信号,假如GCLK1是源时钟,CLK是生成时钟,即CLK相较于GCLK1为倍频信号,我们可以通过如下的描述进行sdc约束

create_generated_clock -name CLK -source [get_ports GCLK1] -multiply_by 2 [get_pins FF2/Q]- 1

- 2

2.3.5 时钟沿位移

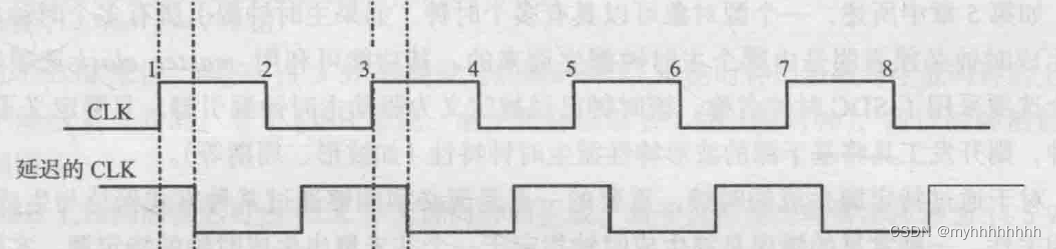

生成时钟的时钟沿可能会受时钟的影响发生位移,在遇到这种情况的时候,我们可以通过-edge_shift的选项,选取一组浮点数,来表示在时间单元内每一个时钟沿的位移。

我们的SDC可以约束如下:

create_generated_clock -name PULSE -source [get_ports clk] -edges {1 1 3} -edge_shift {0 2 0} [get_pins FF1/Q] #在第一个源时钟沿产生上升沿 #在第一个源时钟沿到达2ns后产生下降沿 #在第三个源时钟沿产生上升沿- 1

- 2

- 3

- 4

- 5

2.4 多个同源时钟

参见静态时序分析简明教程(四)时钟常约束中3.5的内容,同样是通过-add来避免时钟信号的覆盖

2.5 使能组合电路路径

假如从源时钟到生成时钟的路径一部分是时序电路,另一部分是组合电路,为了隔绝二者之间的联系,可以使用 -combinational 来加以标识,因为这里用到的不多,因此简略介绍如上。

2.6 注释时钟

参见静态时序分析简明教程(四)时钟常约束中3.6的内容,使用-comment的尾缀增加时钟注释。

三、总结

本节中我们讲解了如何根据源时钟,产生新时钟的SDC约束方法,通过multiply的方式使时钟倍频,通过divide的方式使时钟分频,通过-source的方式标识源时钟(老时钟),也可以通过-edge的方式对齐源时钟和生成时钟的边沿,此外我们还讨论了有关时钟相位偏移的sdc相关约束方法。

-

相关阅读:

MyCat安装

【freeRTOS】操作系统之三-信号量

Redis学习笔记--002

一线大厂软件测试面试题及答案解析,2022最强版...

springboot整合freemarker根据模板导出excel

快速安装redis各种版本

Nacos 配置中心底层原理(1.X版本)

分布式多主关系数据库的底线业务优势

DSPE-PEG-Hydroxyl,DSPE-PEG-OH,一种18碳饱和磷脂PEG衍生物

k8s教程(13)-pod定向调度

- 原文地址:https://blog.csdn.net/weixin_43698385/article/details/127716655