-

【一】Qsys的软核知识记录

第三讲

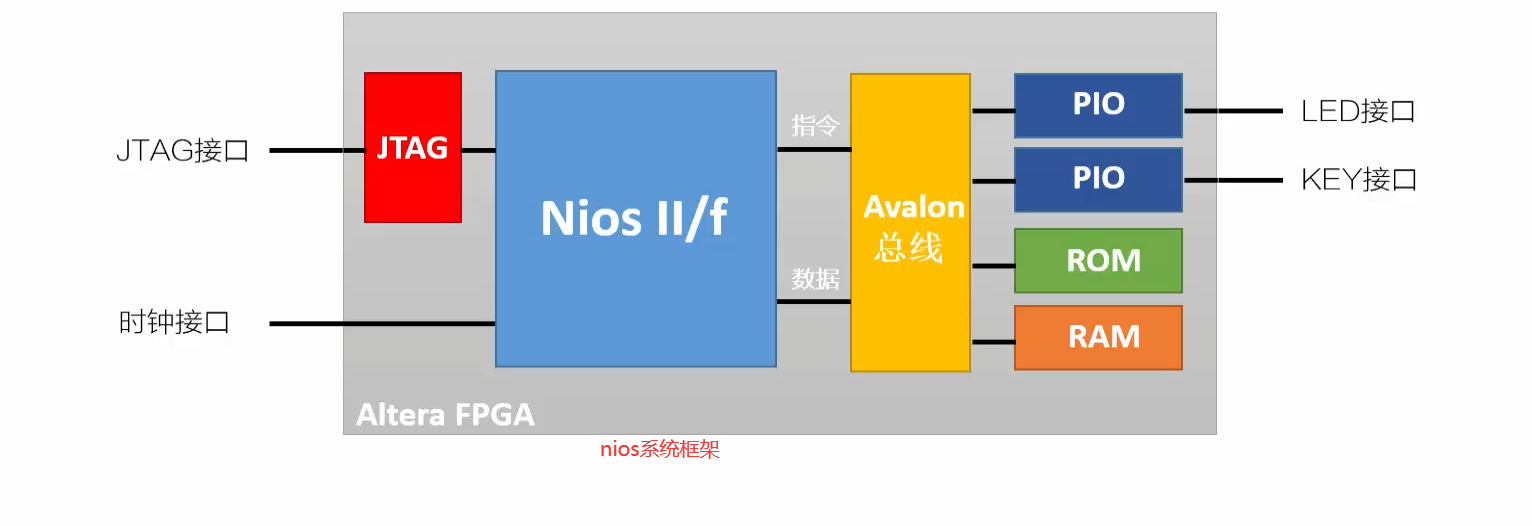

1、 在quartus和Qsys中开发称为硬件开发,eclipse中开发为软件开发

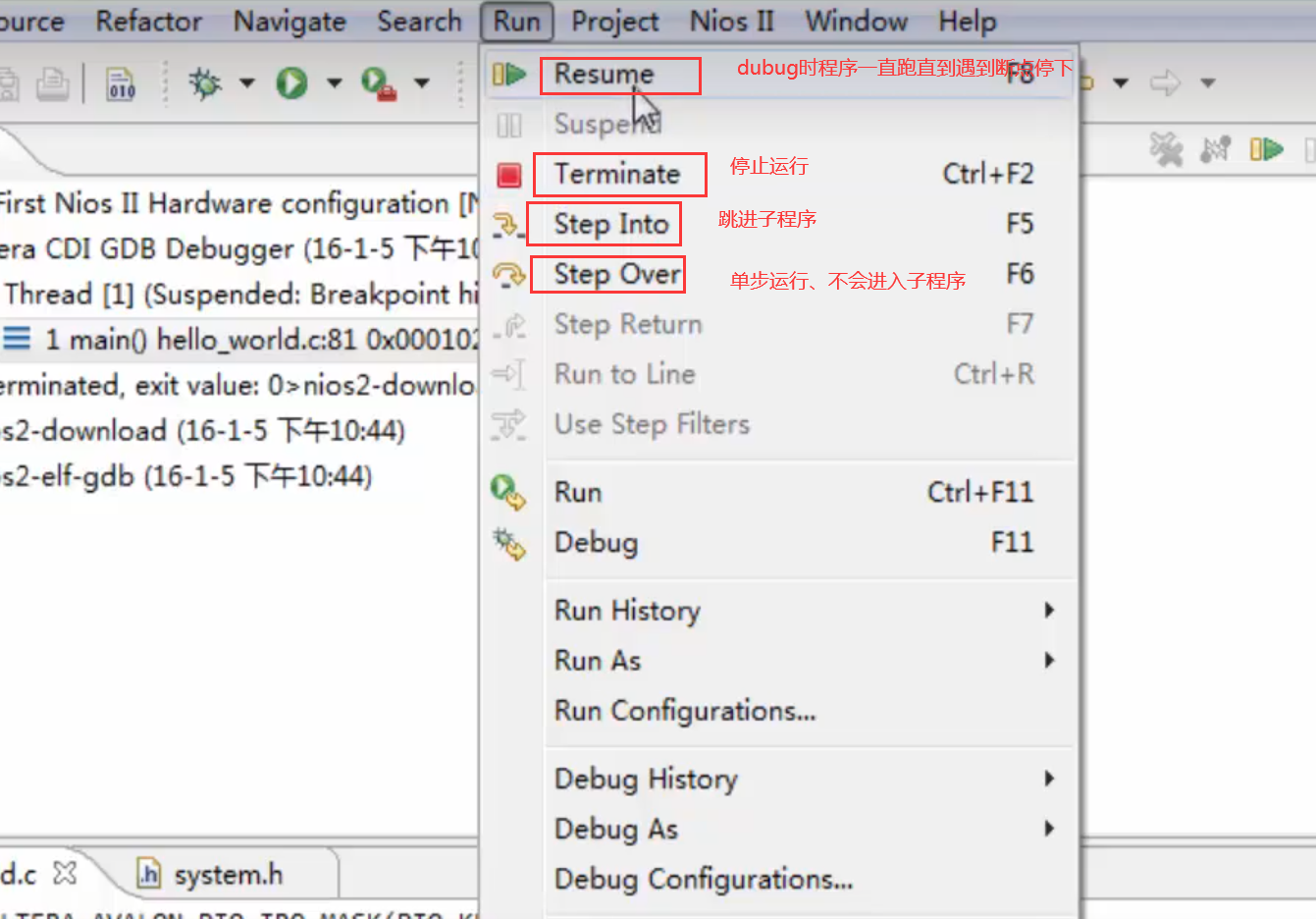

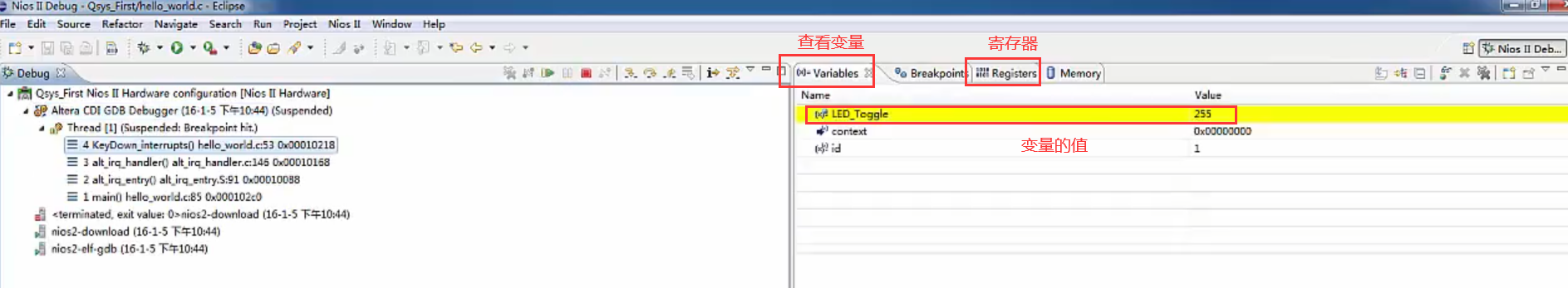

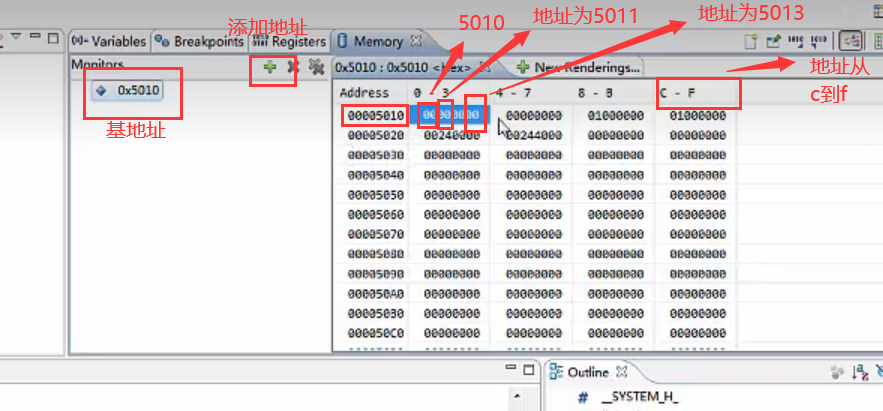

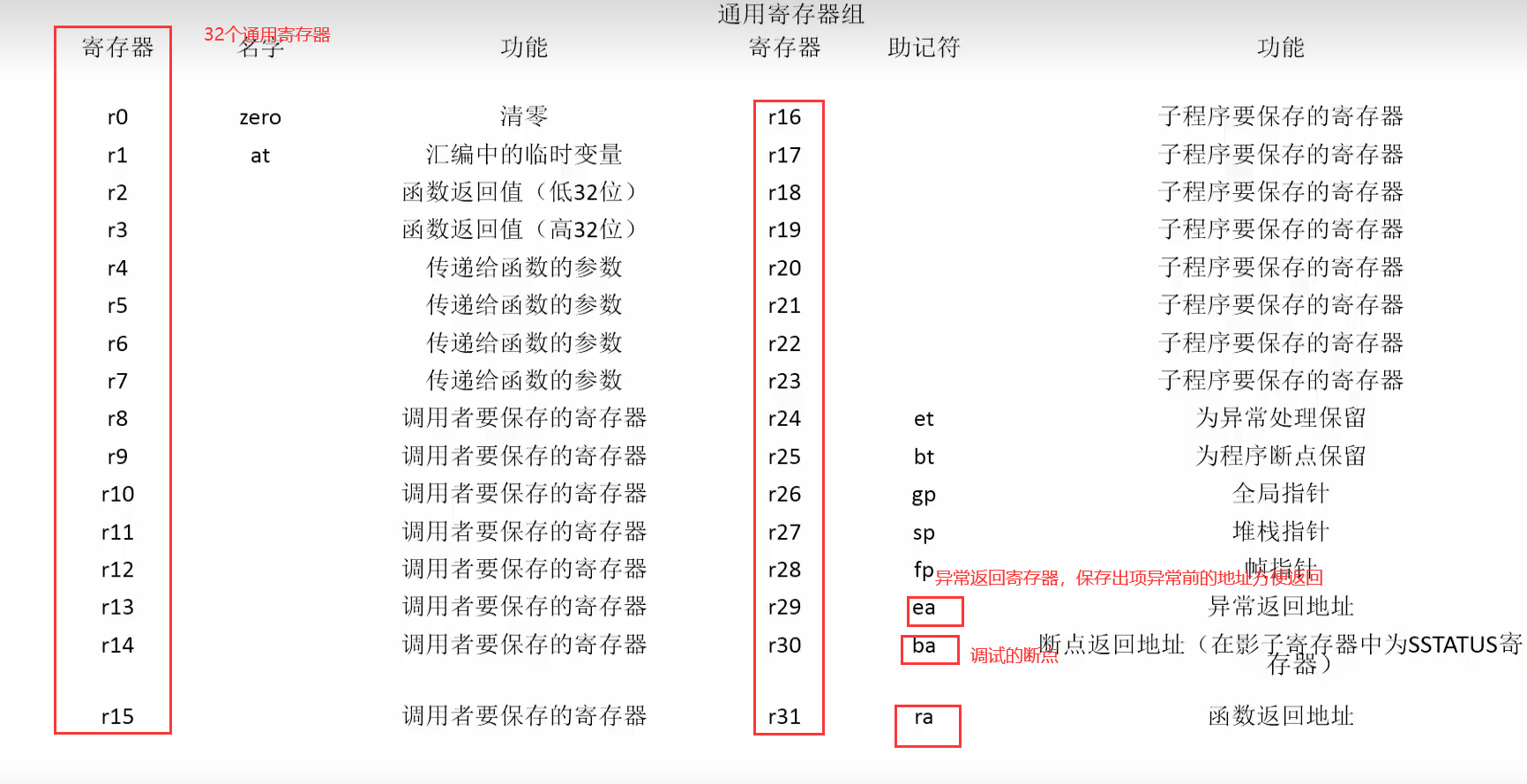

2、关于dubug

一个地址放8个字节,

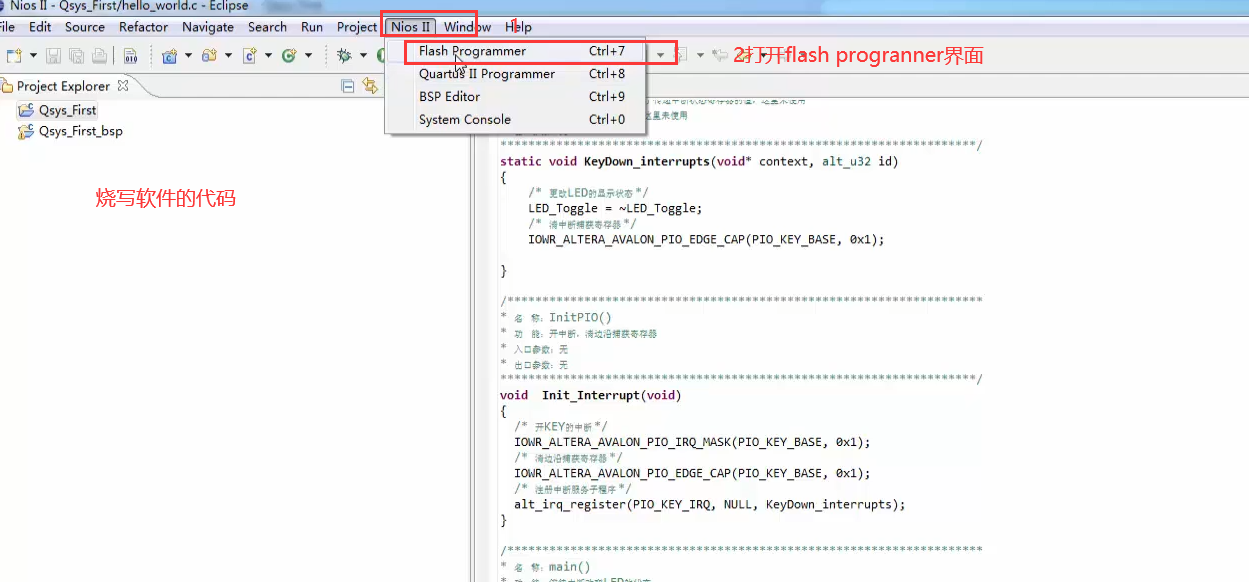

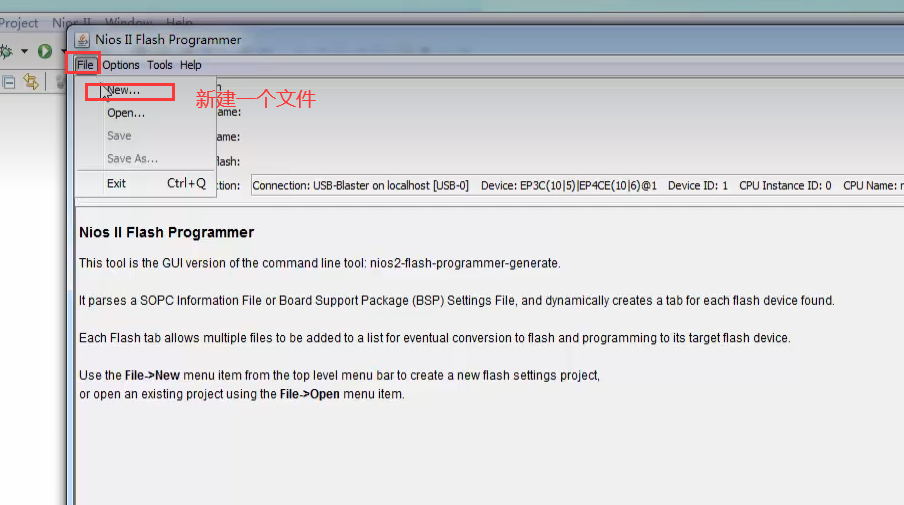

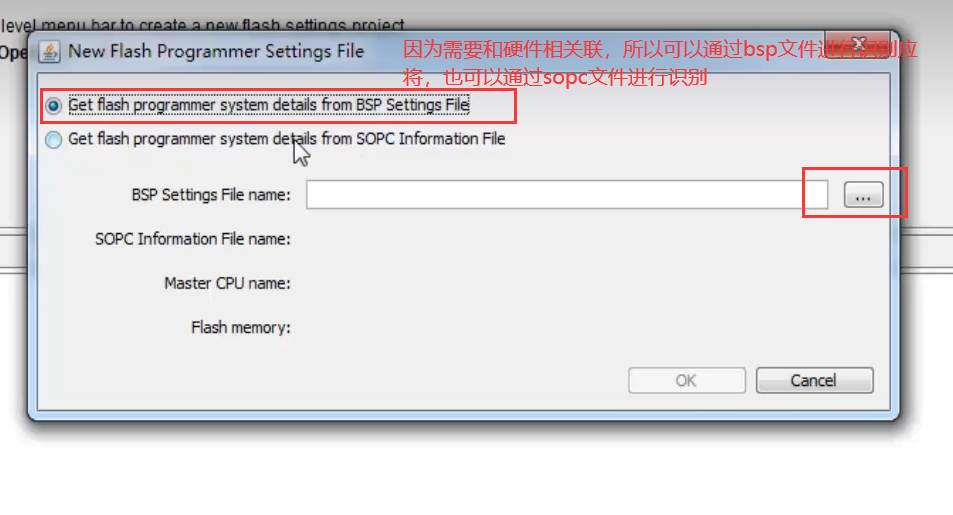

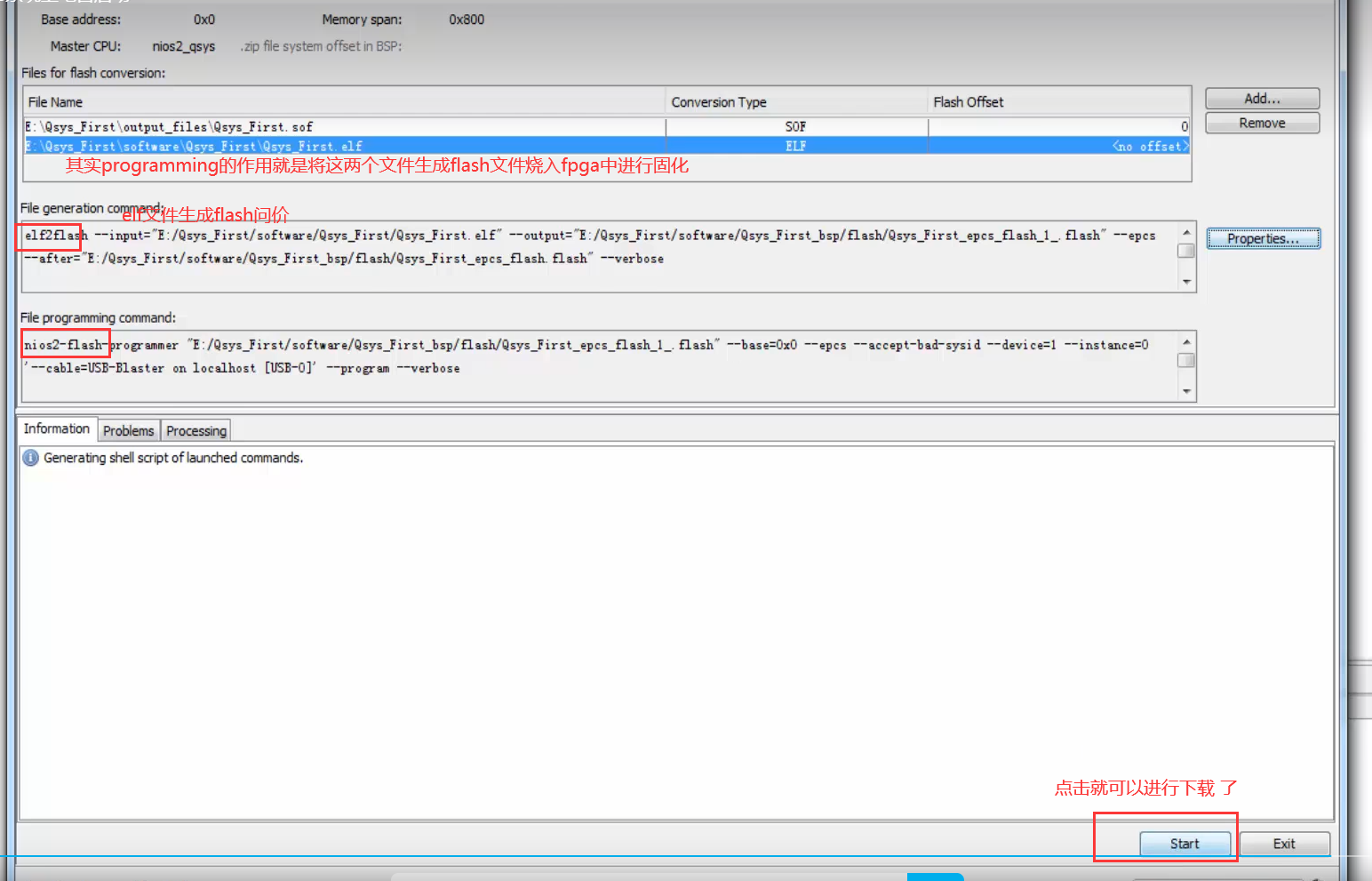

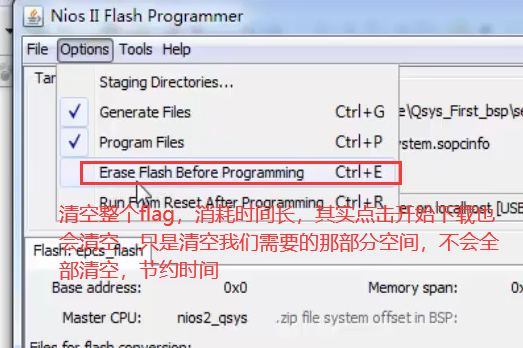

固件化程序

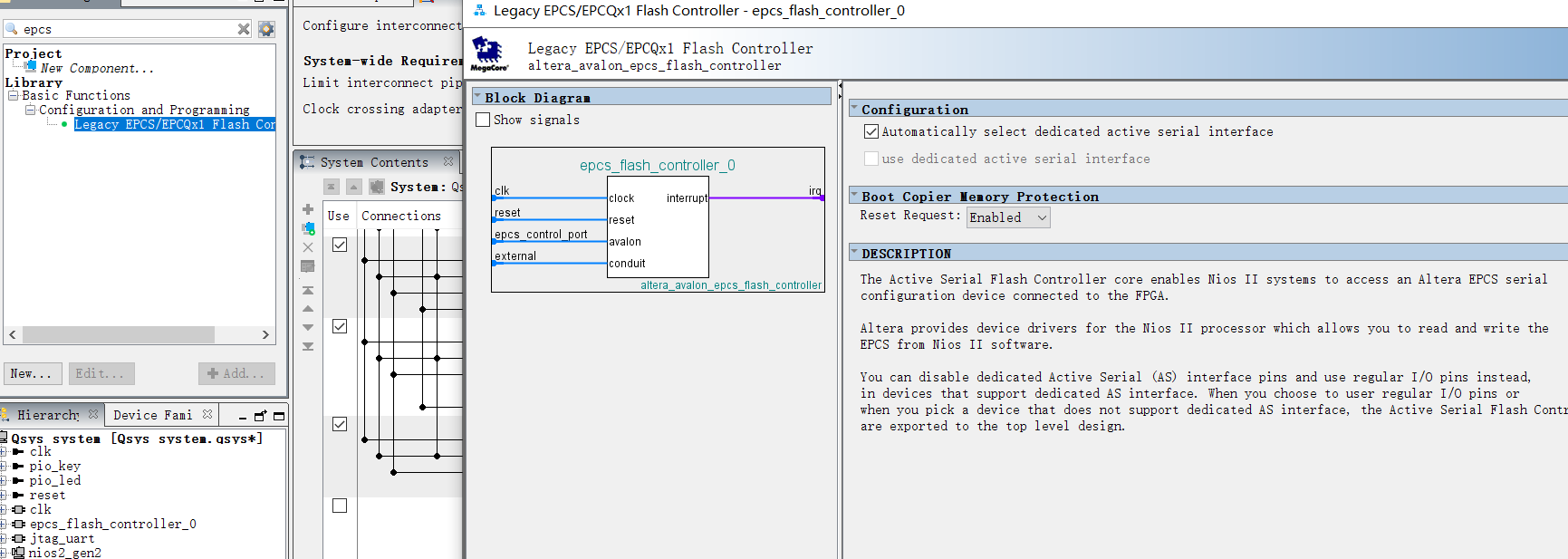

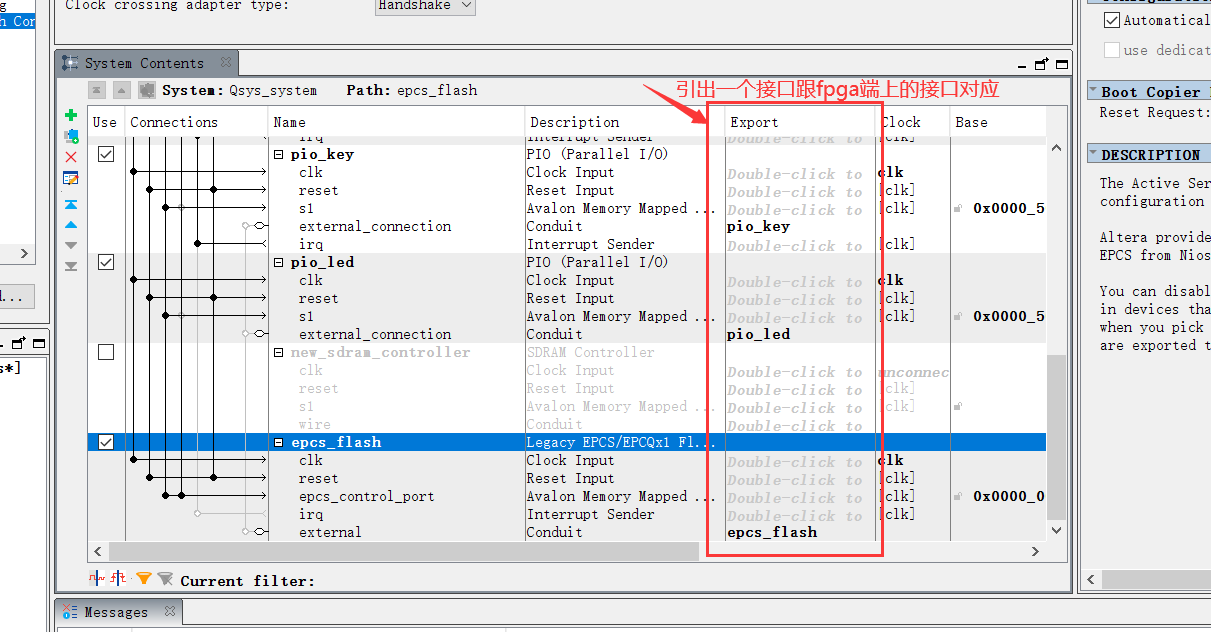

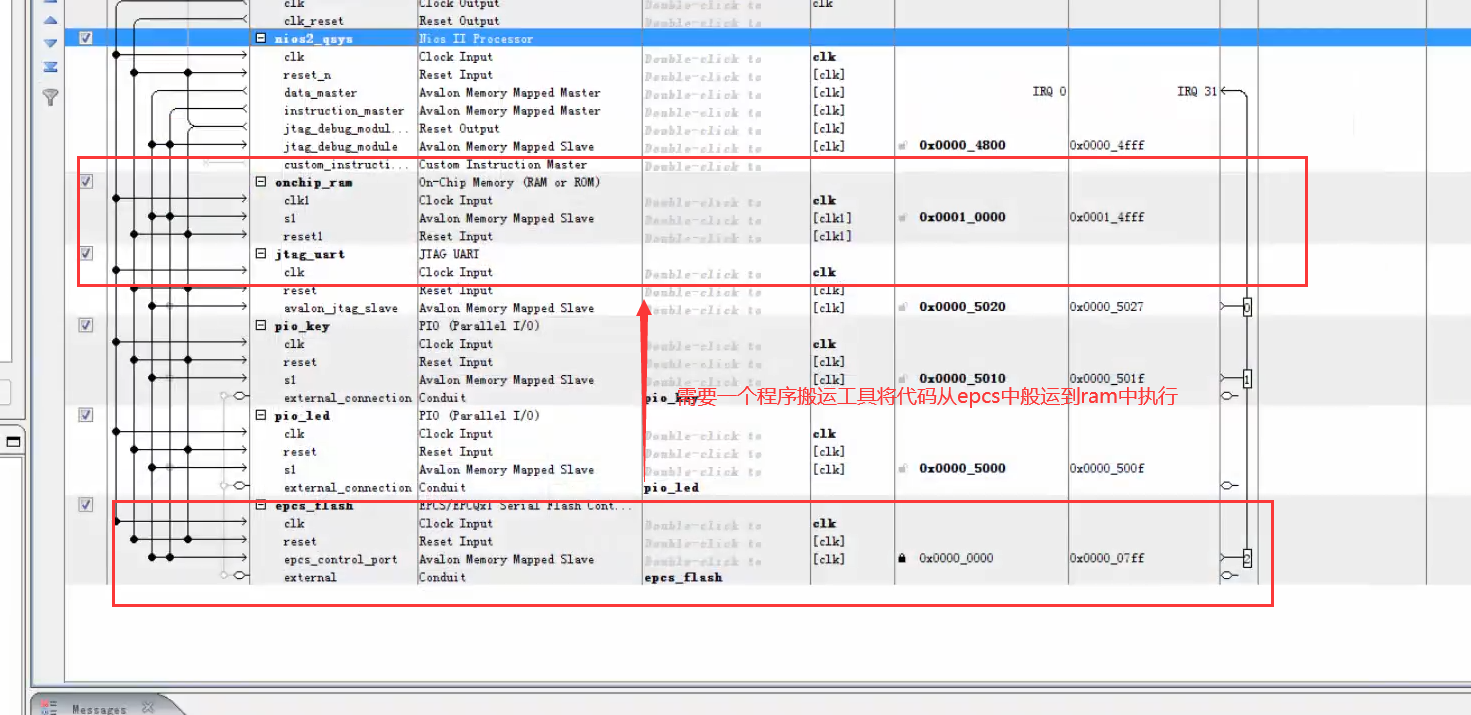

需要在Qsys中加入epcs_flash_controller的flash控制器。epcs实际上就是一个串行的flash

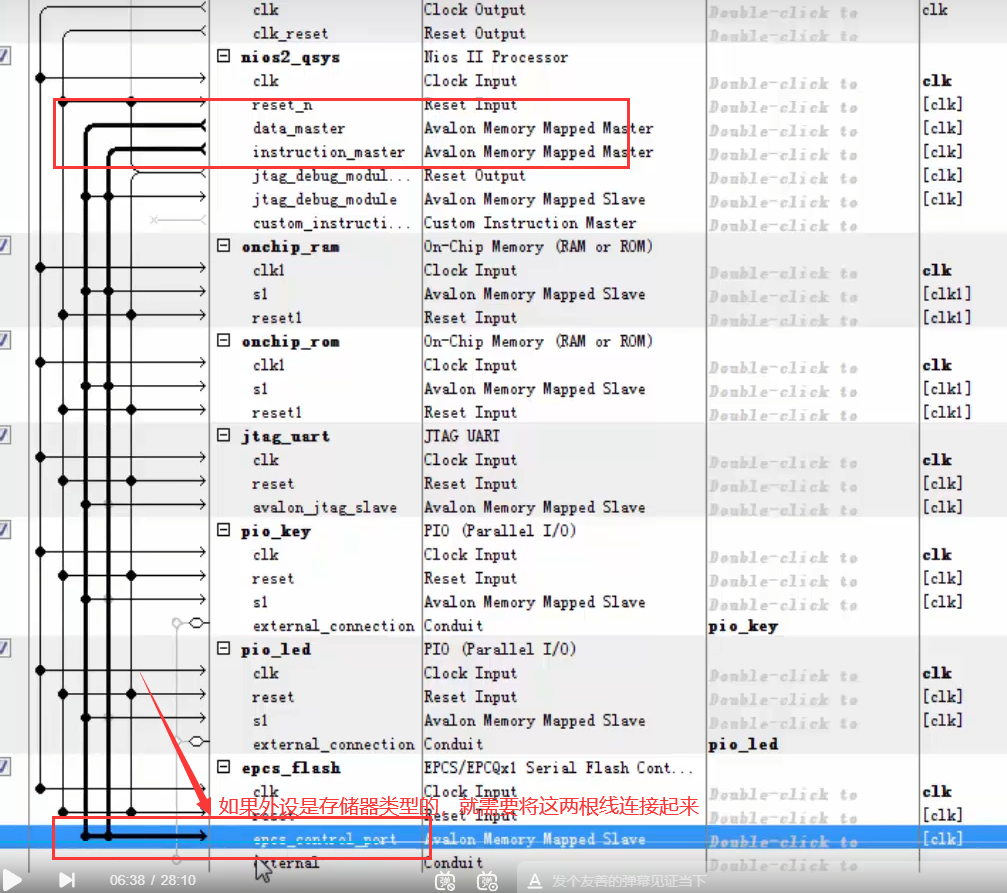

如果添加的核(外设)为存储器类型的,就需要将data_master和instruction_master两个线连接起来,如果外设不是存储类型的只需要连接data_master

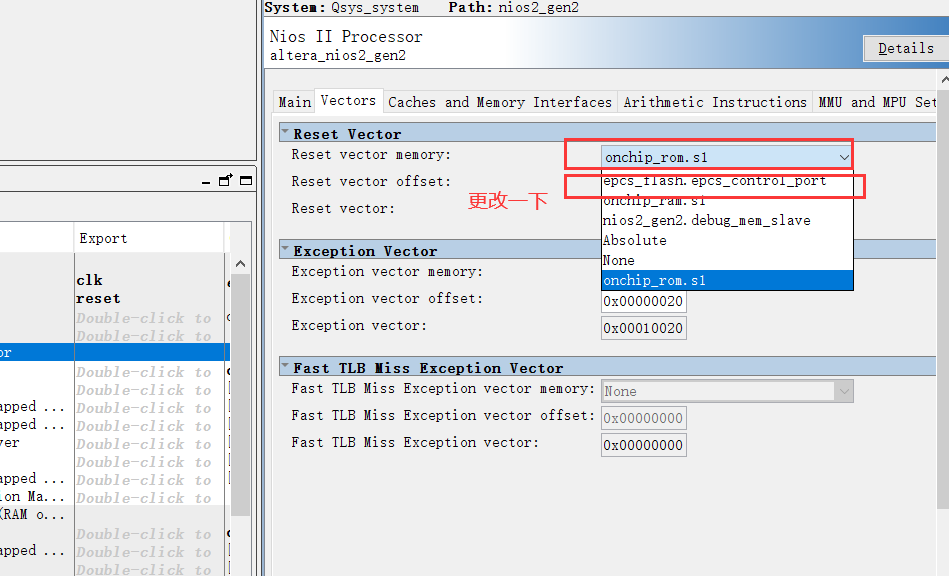

出现这样的错误 Error: Qsys_system.nios2_gen2: Reset slave onchip_rom.s1 not connected to instruction_master.

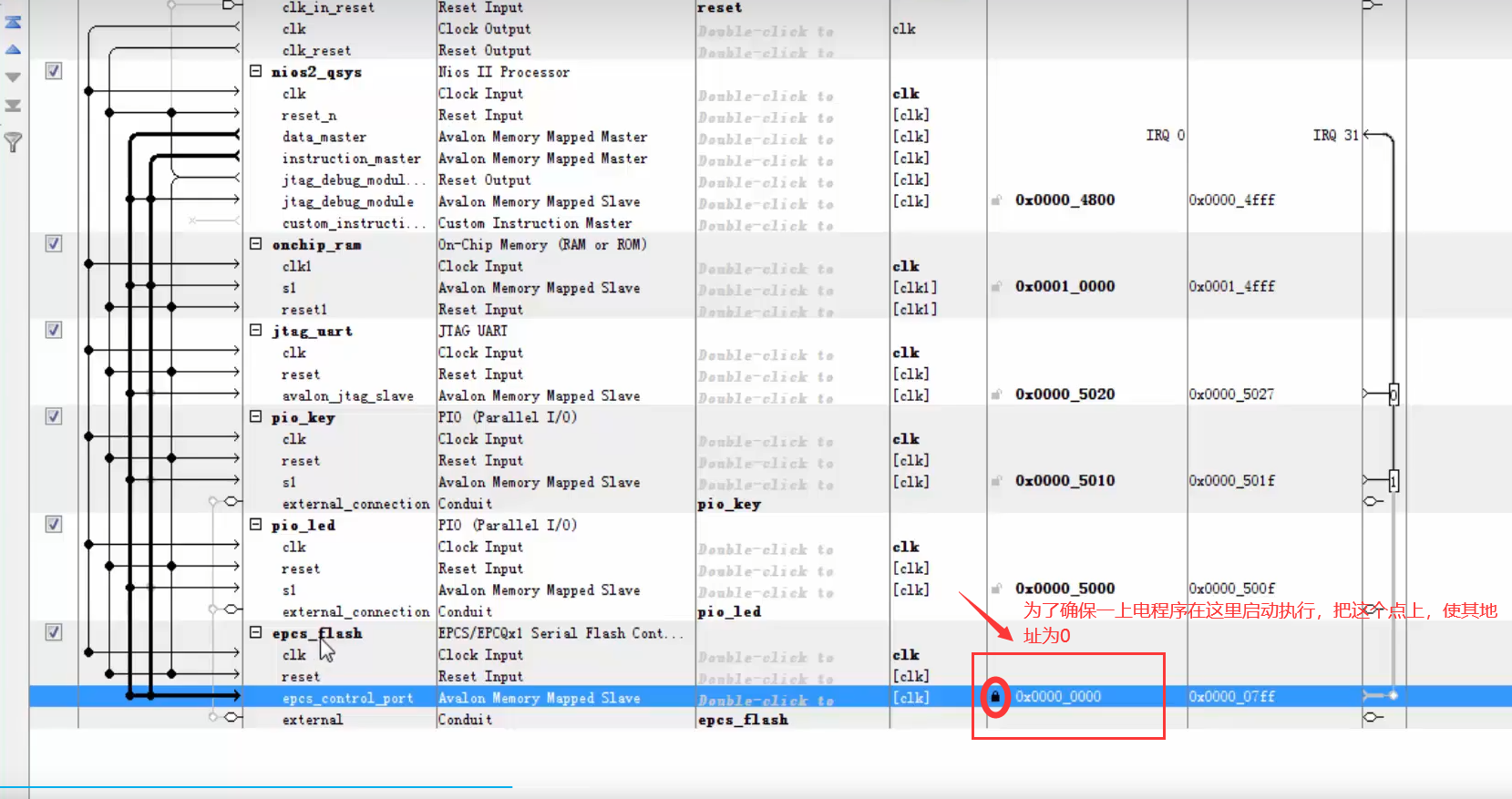

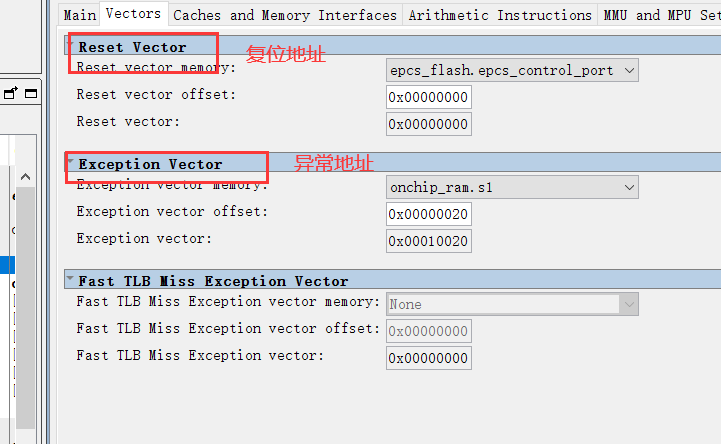

复位地址:芯片一上电程序就开始执行的起始地址,

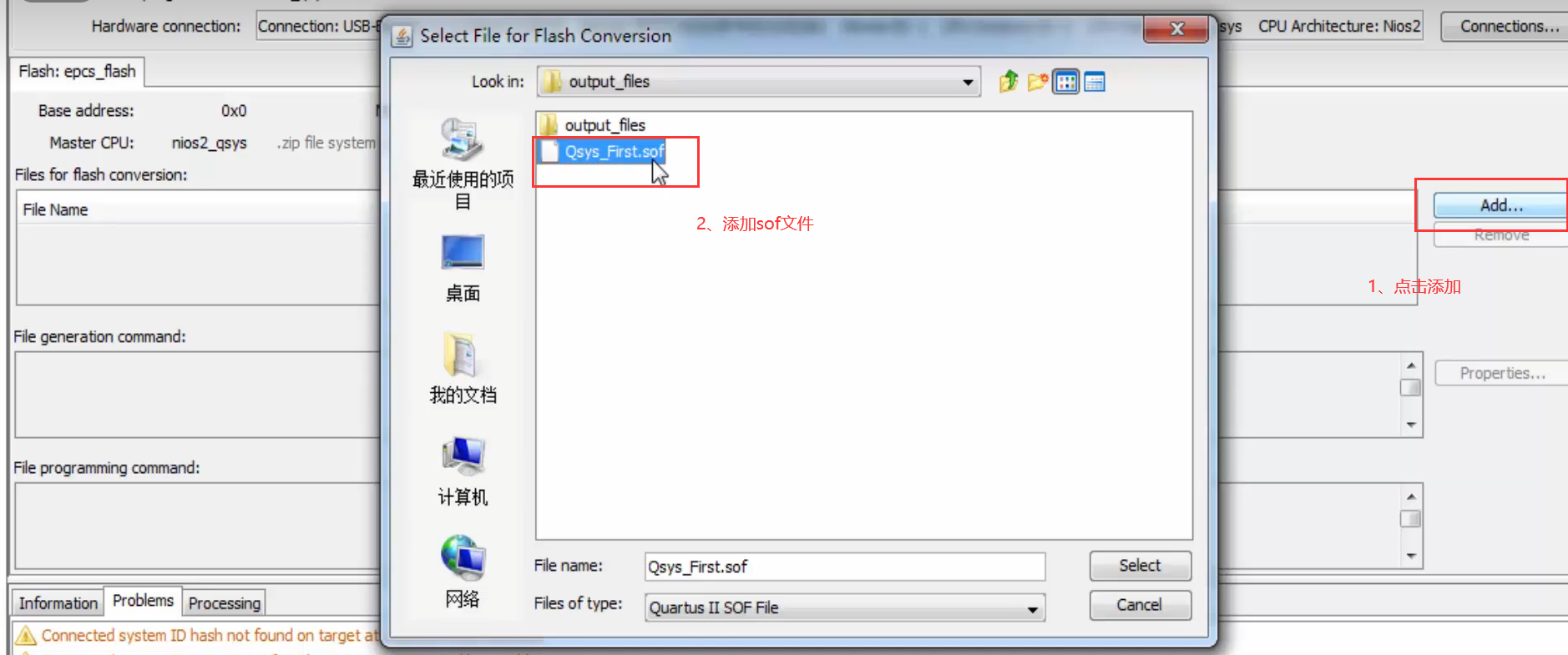

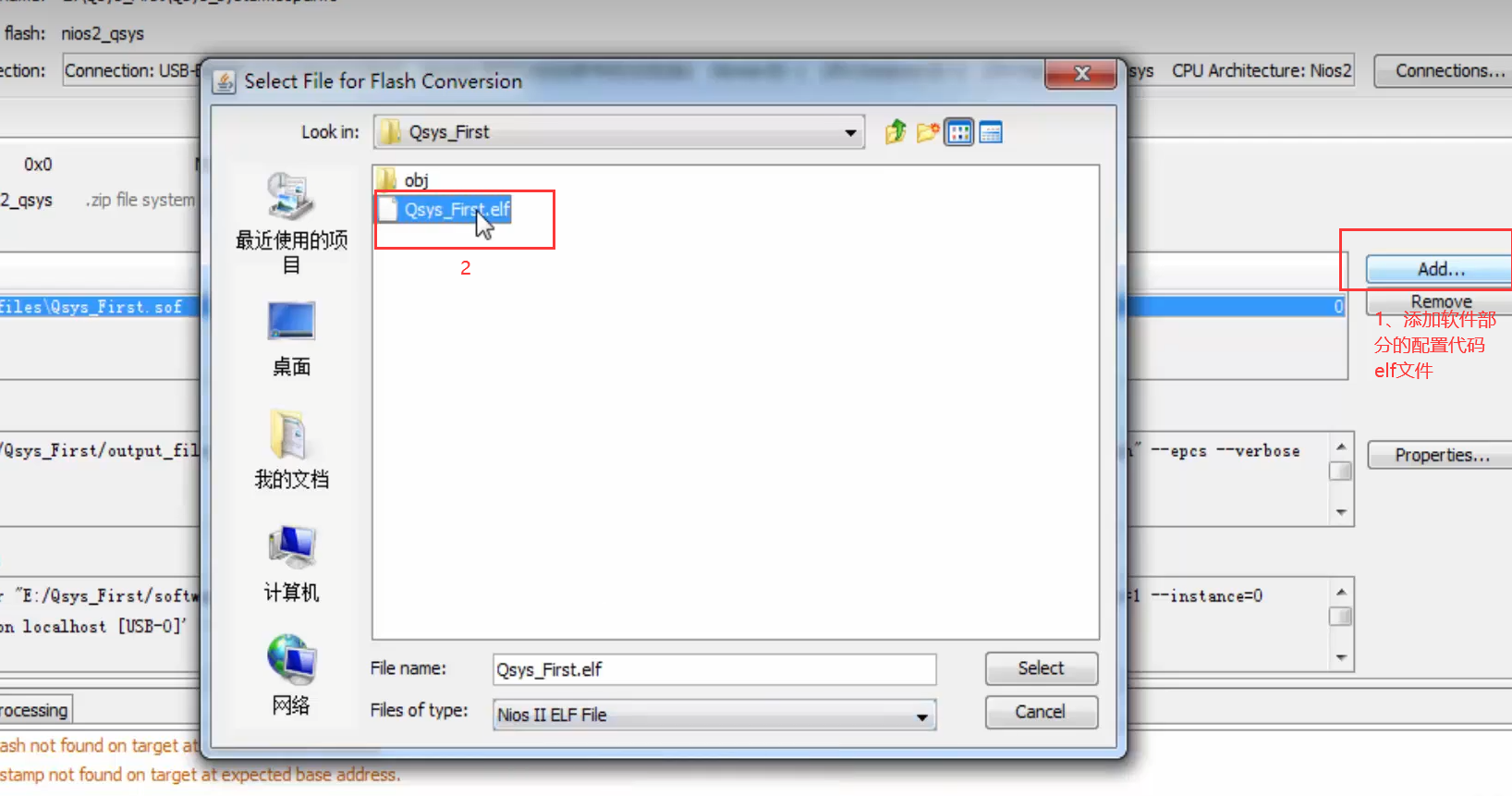

程序烧写:

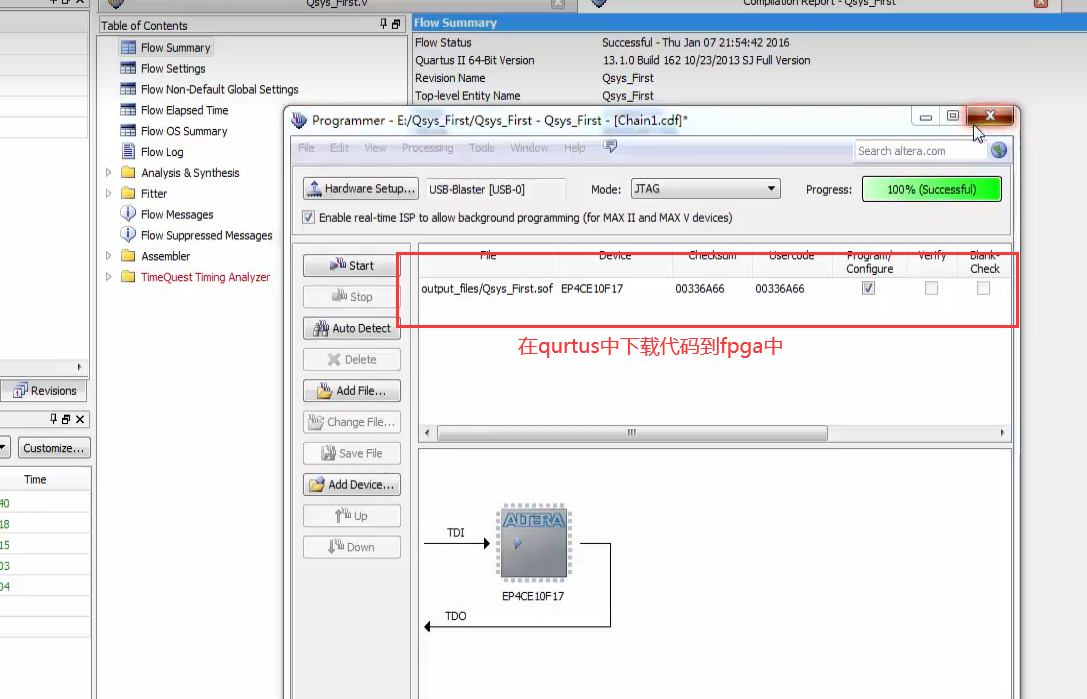

首先呢先在quartus中将硬件框架部分sof烧入到fpga中,然后再eclipse中烧入软件部分代码。

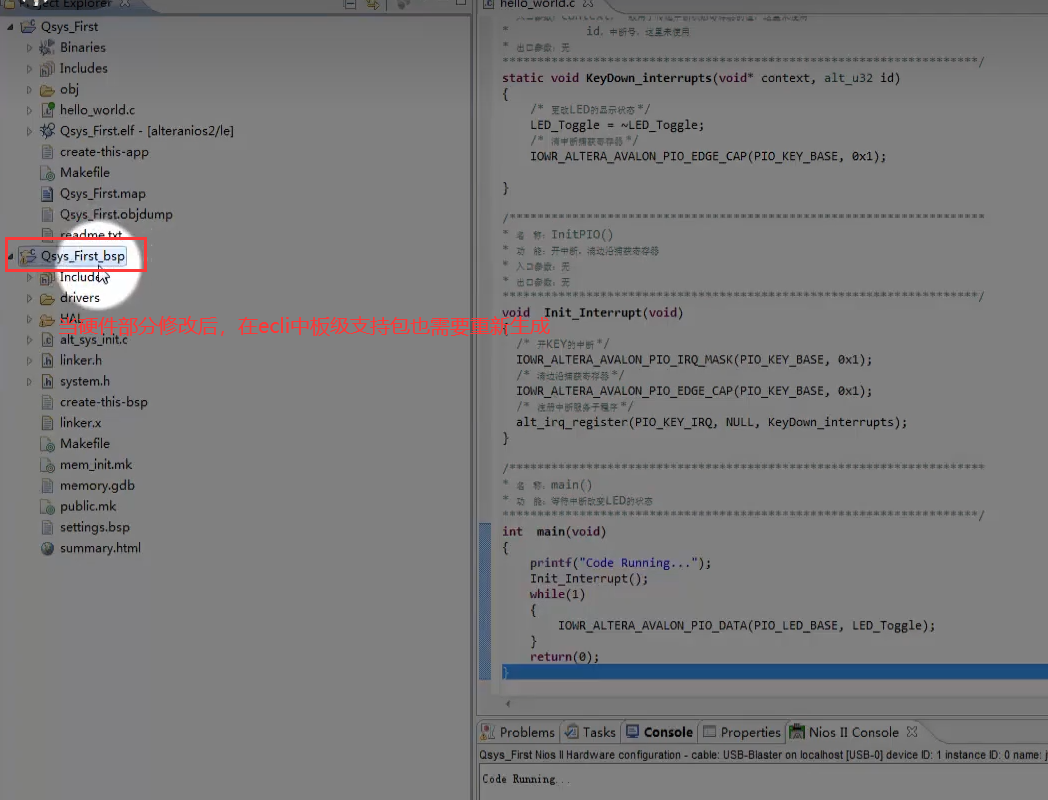

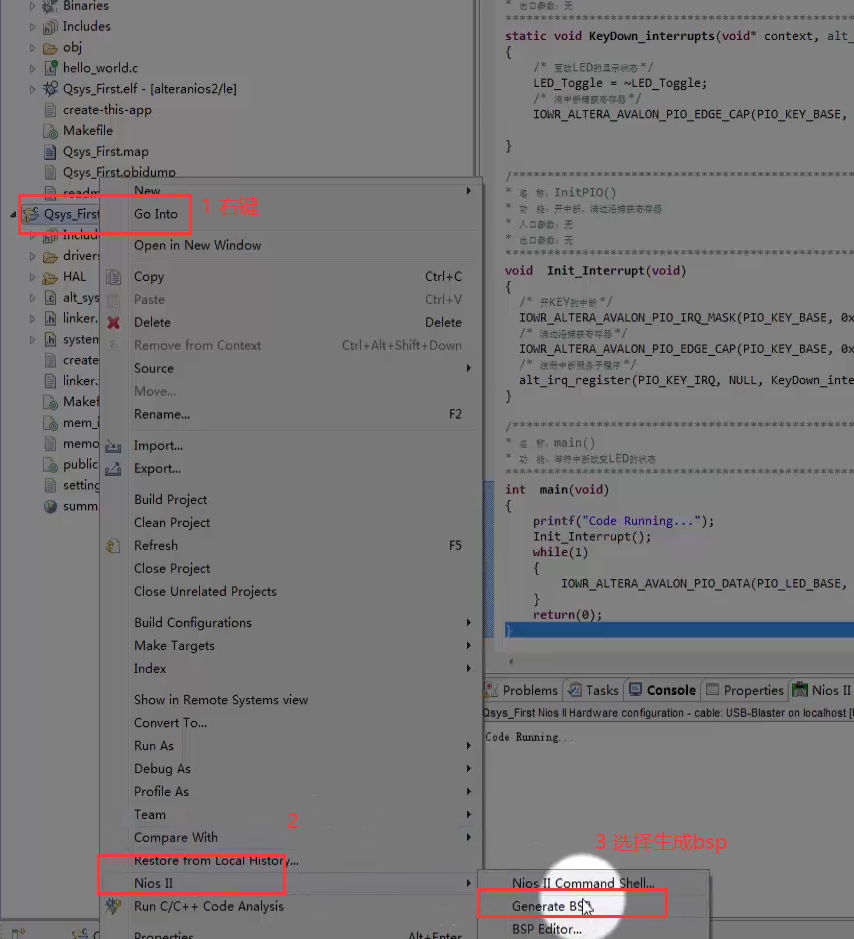

如果修改了硬件部分,需要重新生成板级支持包:

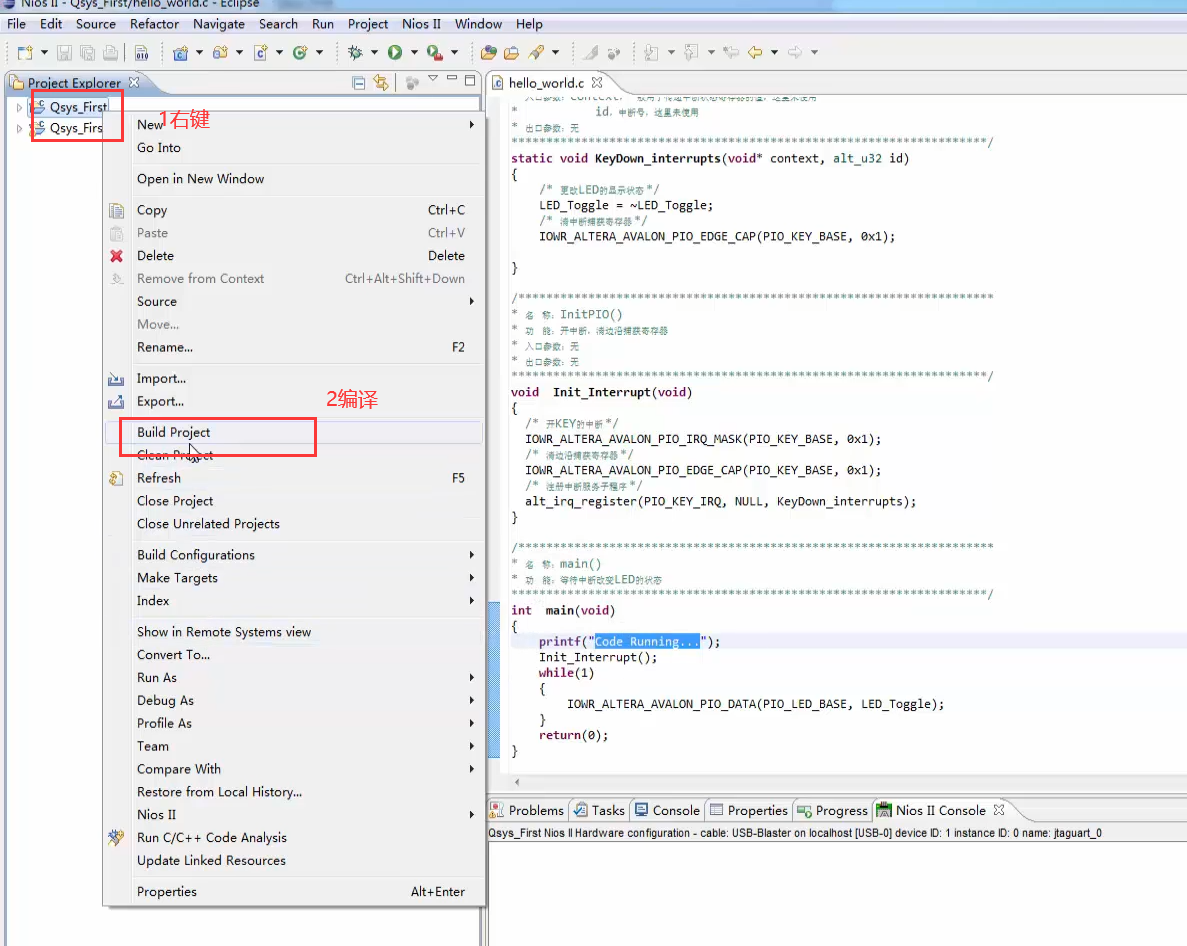

重新生成bsp后,对整个工程重新编译

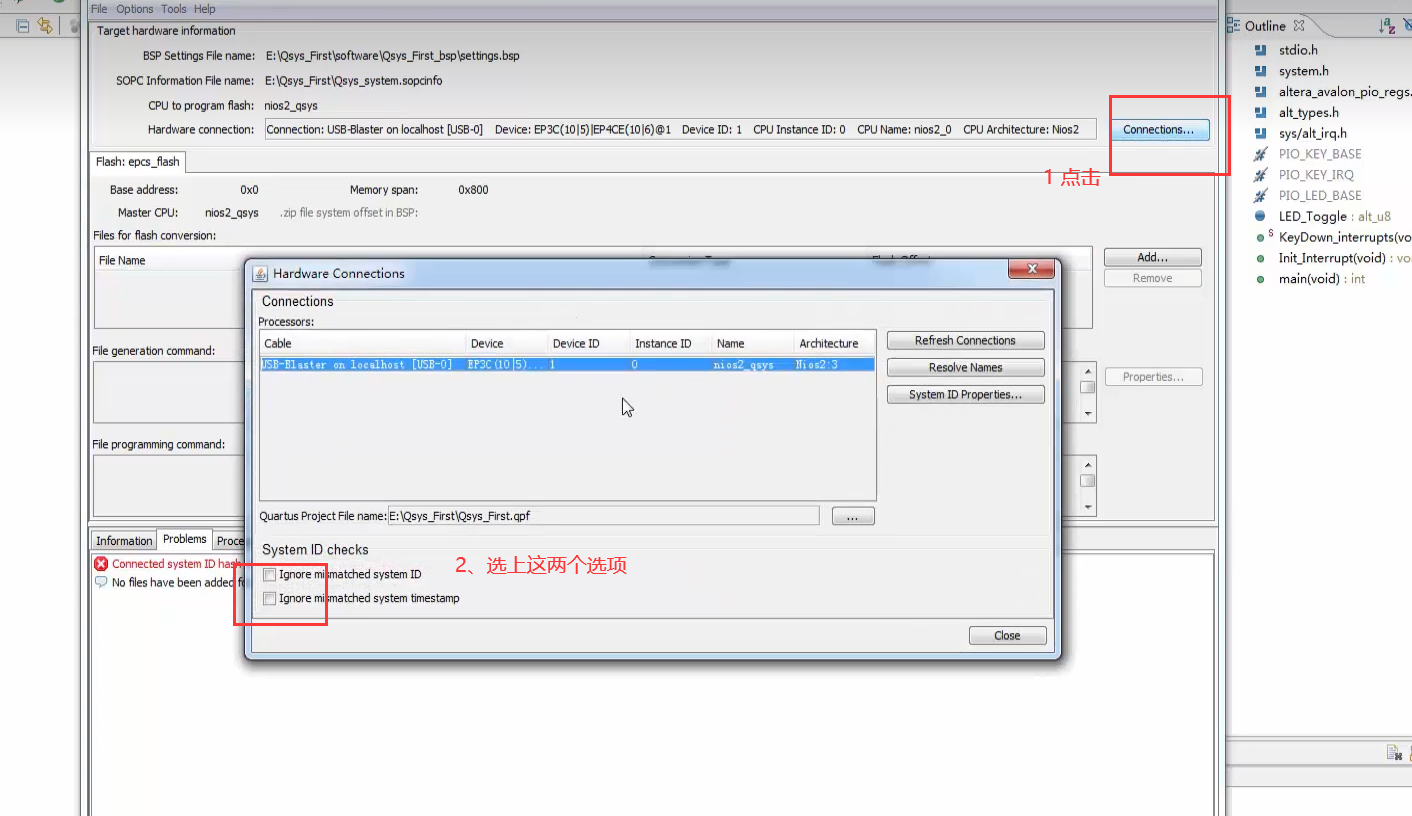

点击ok之后会出现这样的错误:connected system ID hash not found on target at expected base address.

解决的方法:将ignore mismatched system ID和ignore mismatched system timestamp 勾上(因为没有分配systme id,选择忽略即可)

第四讲

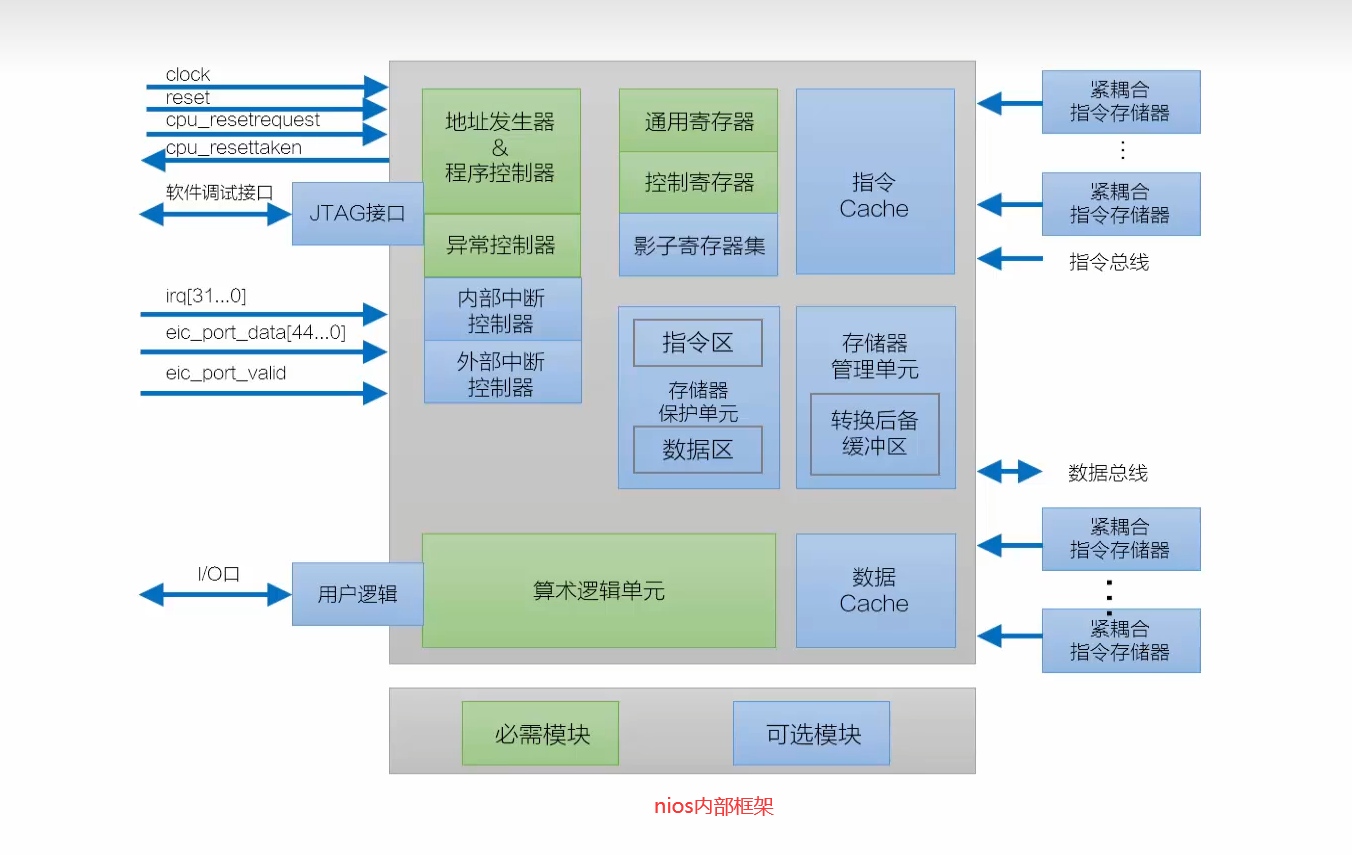

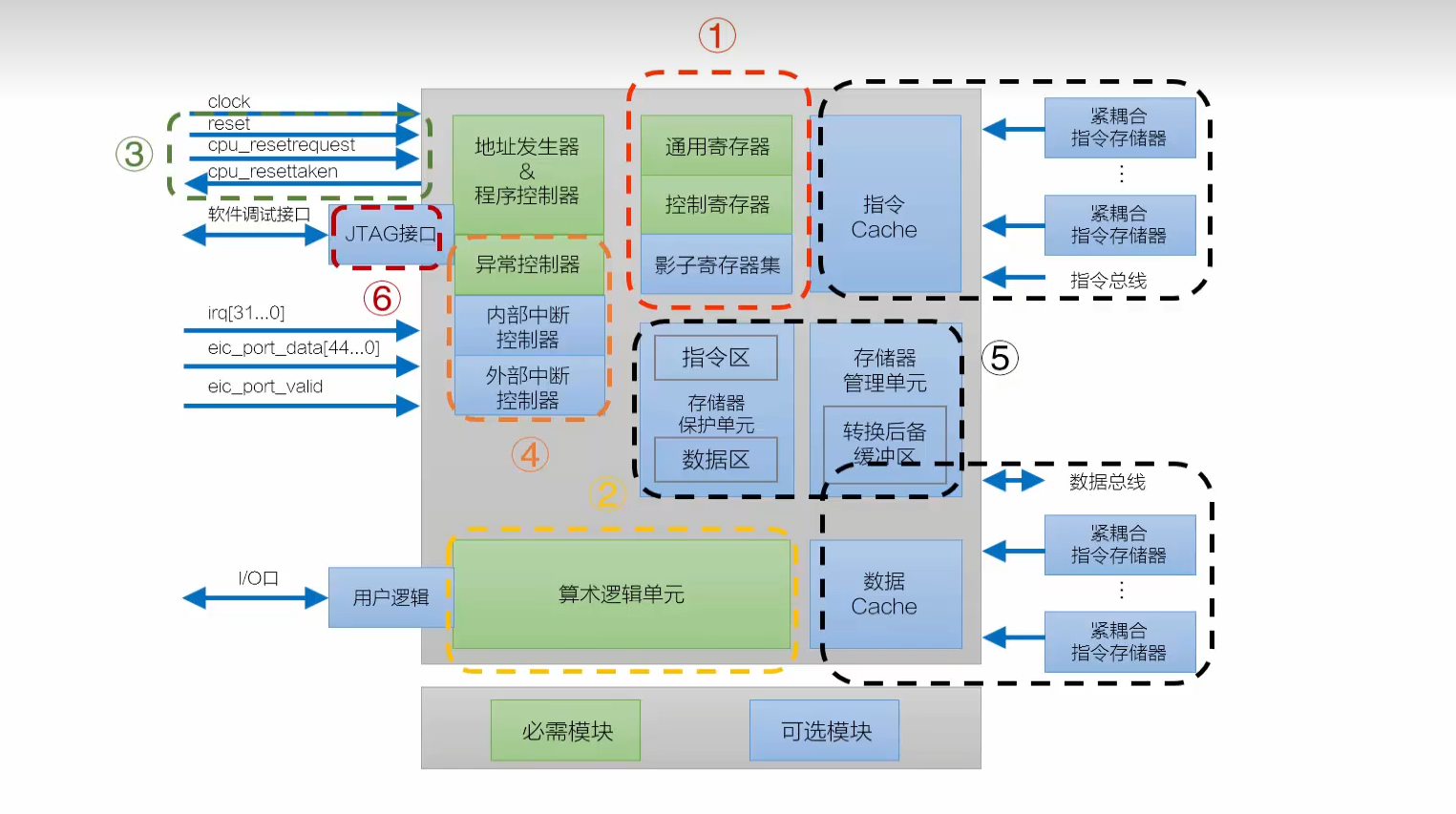

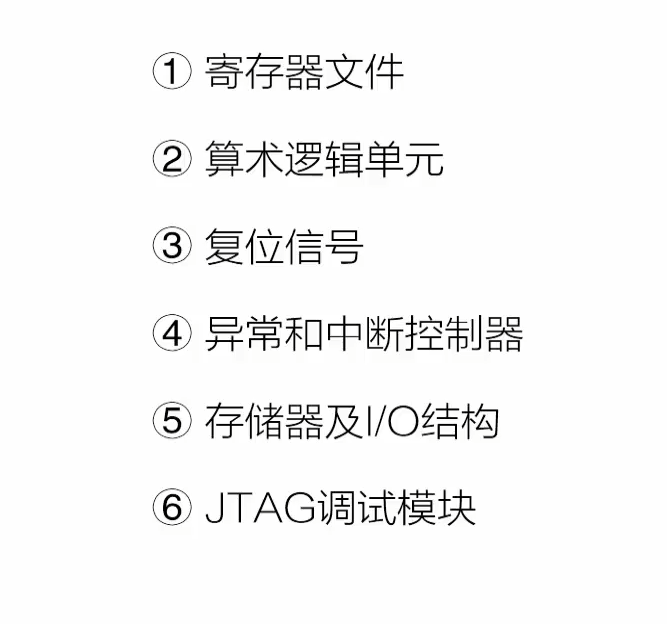

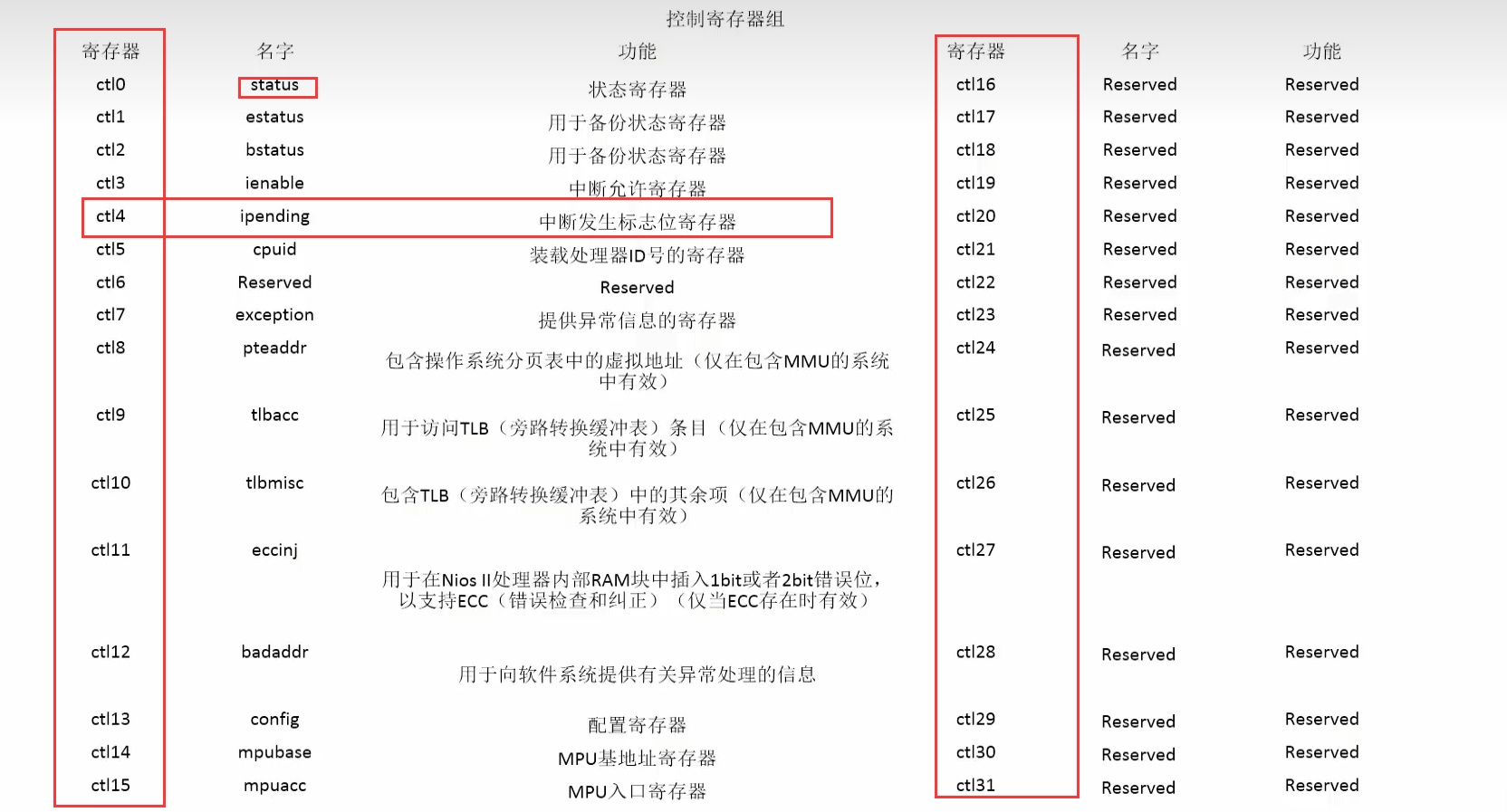

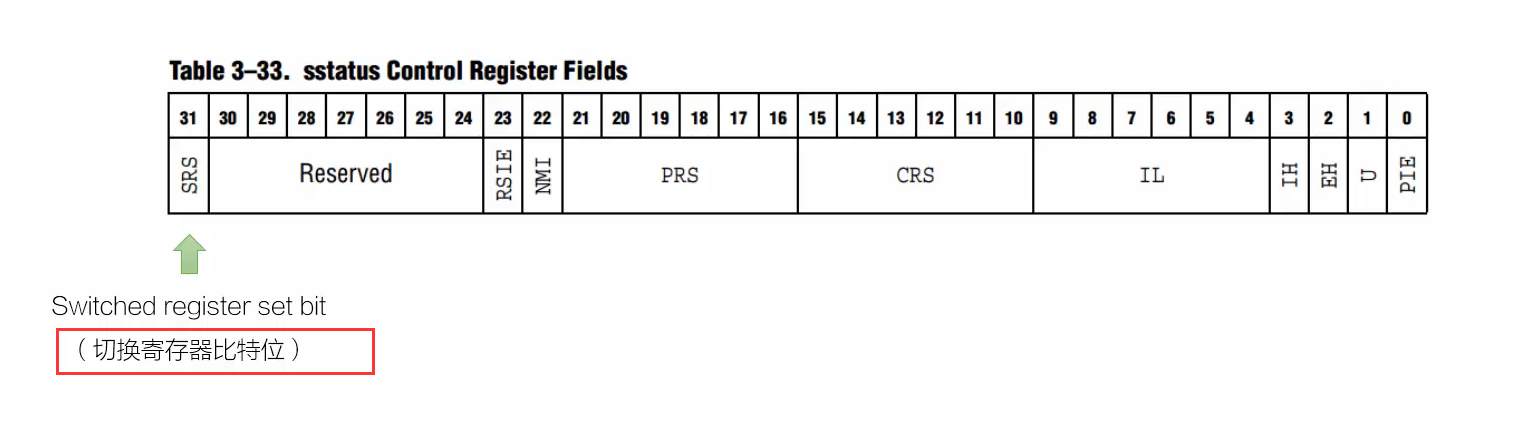

寄存器文件:寄存器文件时nios II处理器内部用于存放数据的一些小型存储区,可以用来暂时存放参与运算的数据和运算结果。包含32个通用寄存器(可以有多种用途,如暂存指令、数据和地址)、32个控制寄存器(控制和确定nioss II 处理器的操作模式和当前执行任务的特性)以及影子寄存器组。

ienable控制寄存器的介绍:中断允许寄存器,每一位控制一个中断通道。eg:第0位为1时表示允许第0号中断发生,如果为0这表示禁止第0号中断禁止。

ipending控制寄存器的介绍:中断发生标志位,每一位反映一个中断。eg:第0位为1表示第0号中断发生,如果位0,则表示第0号未发生中断。

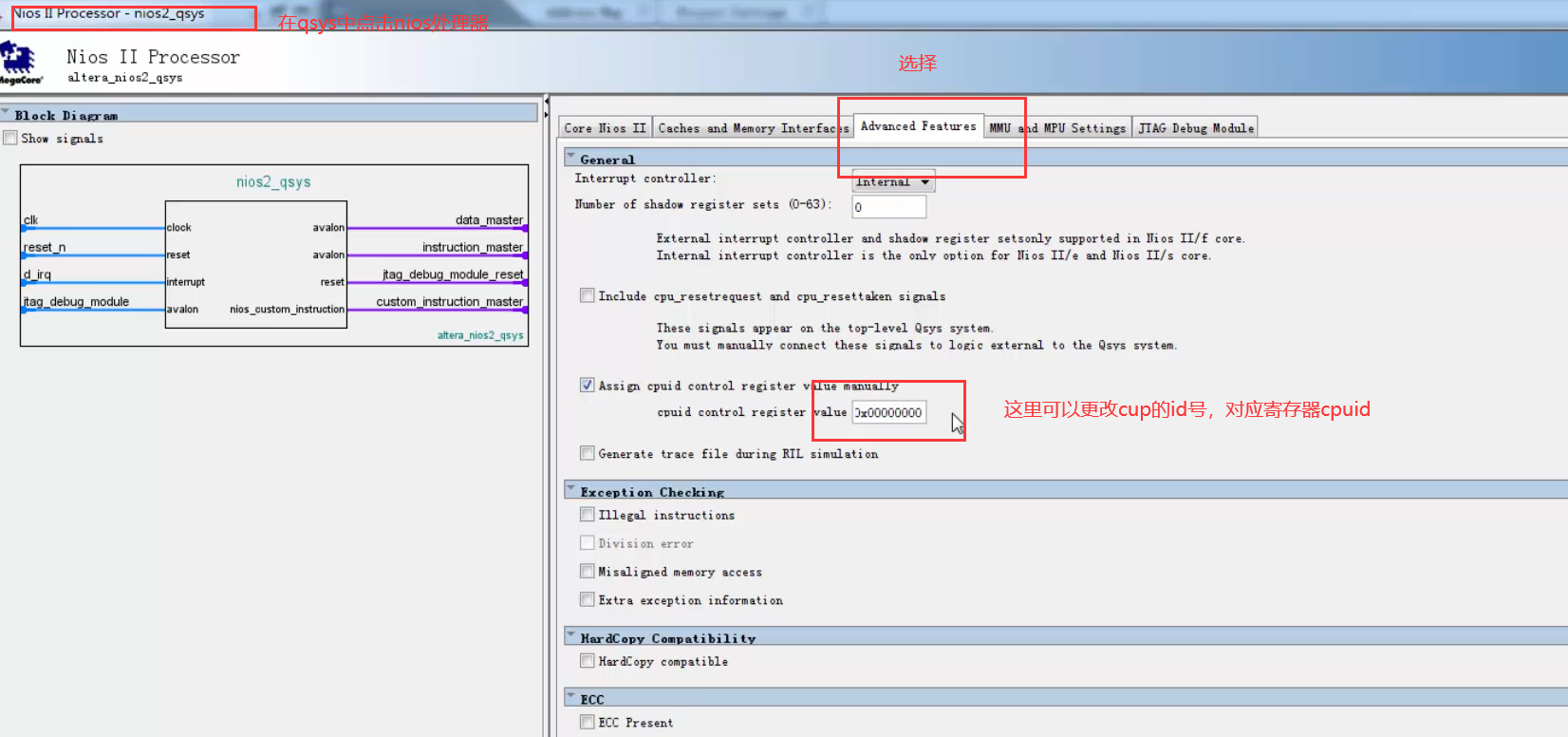

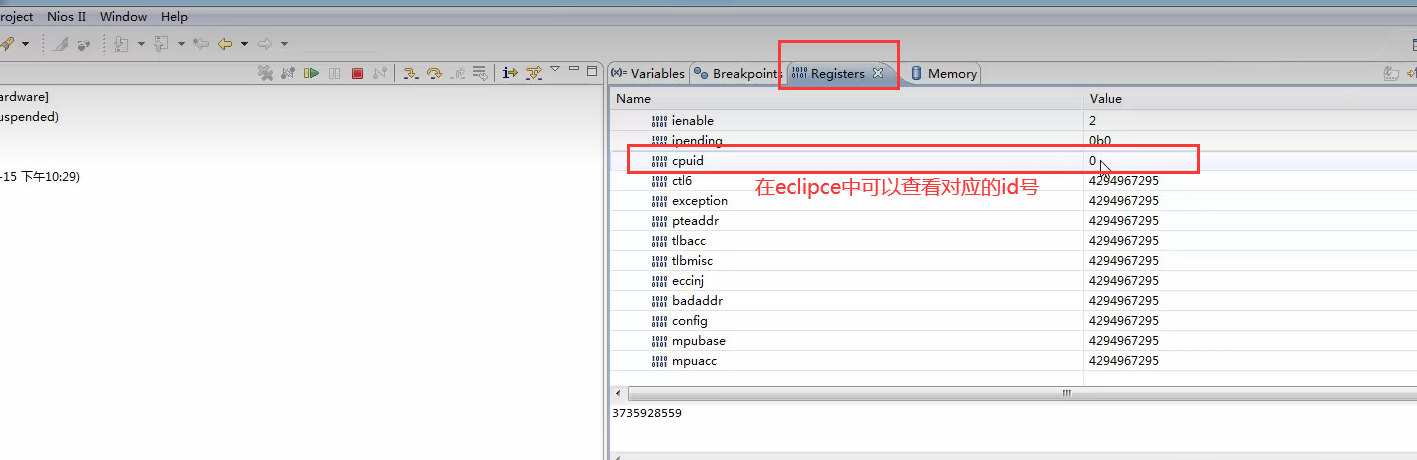

cpuid控制寄存器的介绍:装载处理器的id号,该id号在生成nios II系统的时候产生,id号在多处理器系统中可以作为分辨cpu的标识。

**影子寄存器组介绍:**用来备份通用寄存器和状态寄存器。影子寄存器组通常会和外部中断控制器联合使用。

算数逻辑单元(ALU)

对存储在通用寄存器中的数据操作,ALU从寄存器中取出一个或者两个操作数,经过计算之后并将运算的结果返回寄存器中。nios处理器中支持的逻辑运算

- 算数运算:加减乘除

- 关系运算:有符号和无符号的等于、不等于、大于等于、和小于运算;

- 逻辑运算:与、或、非、异或

- 移位运算:逻辑右移、逻辑左移、算术右移、算术左移、循环右移和循环左移

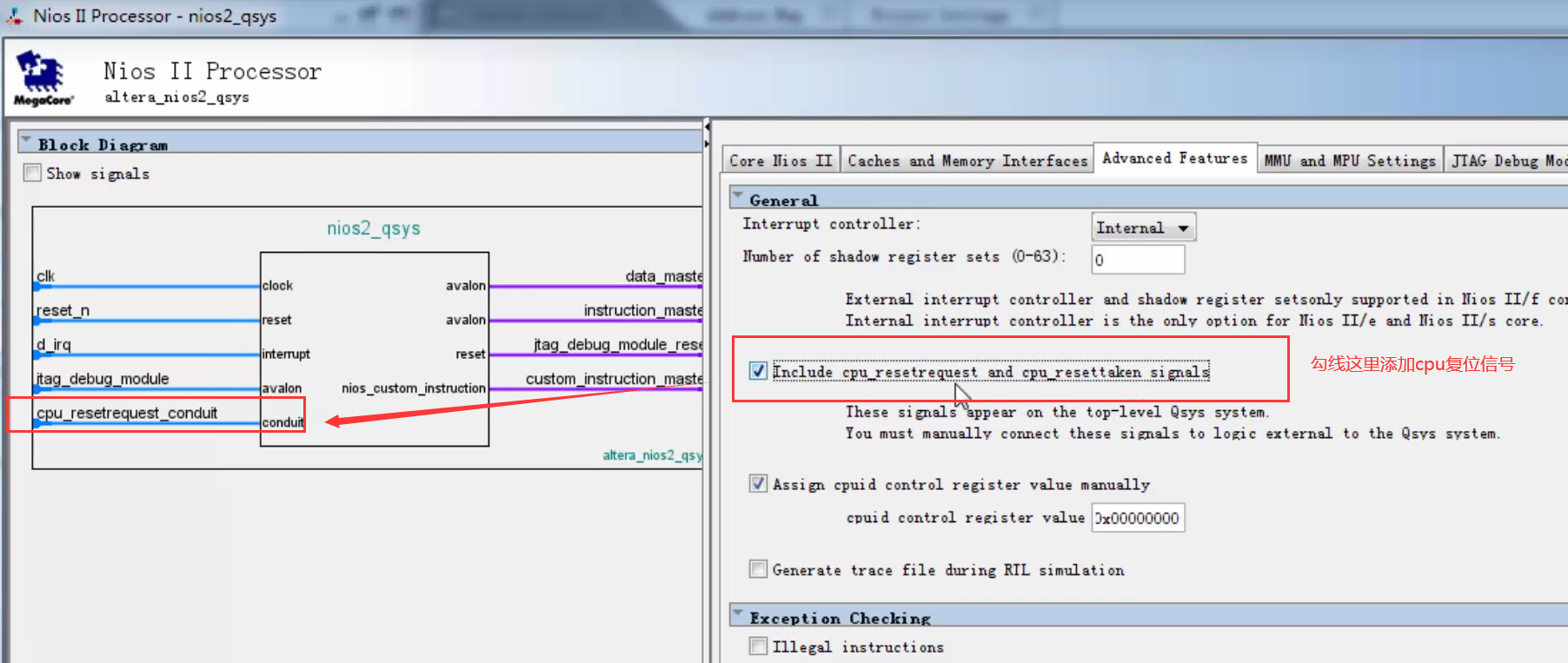

复位信号

reset:全局硬件复位信号,这个复位信号是一个外部输入信号,高电平有效,这个信号可以强制处理器核立即进行复位。

cpu_resetrequest:本地复位信号,高电平有效,它可以只让cpu复位,而nios II系统中的其他元件不受这个复位信号的影响。

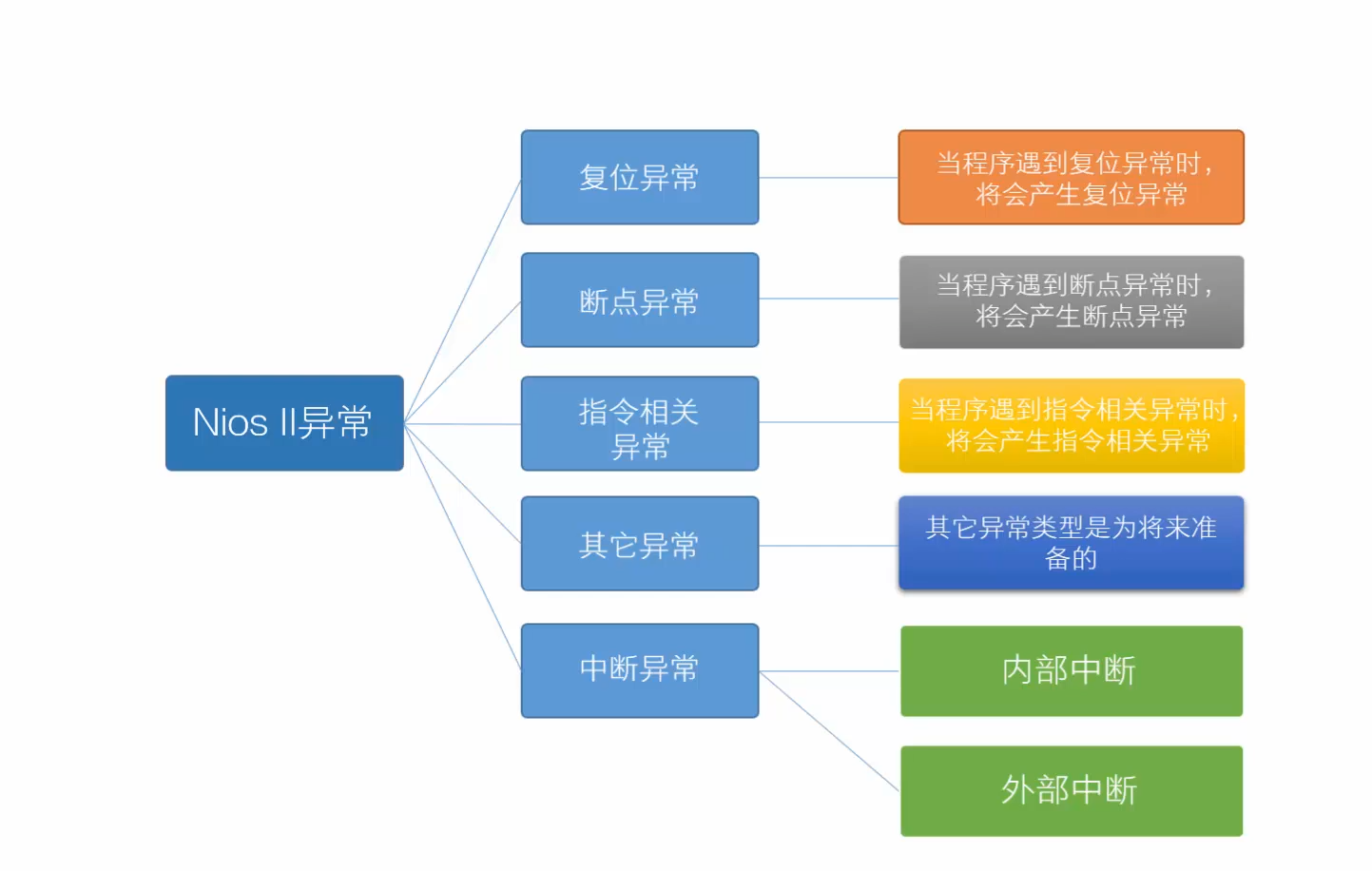

异常和中断

中断异常分为内部中断异常和外部中断异常。

内部中断

具备以下条件,系统才会产生硬件中断:

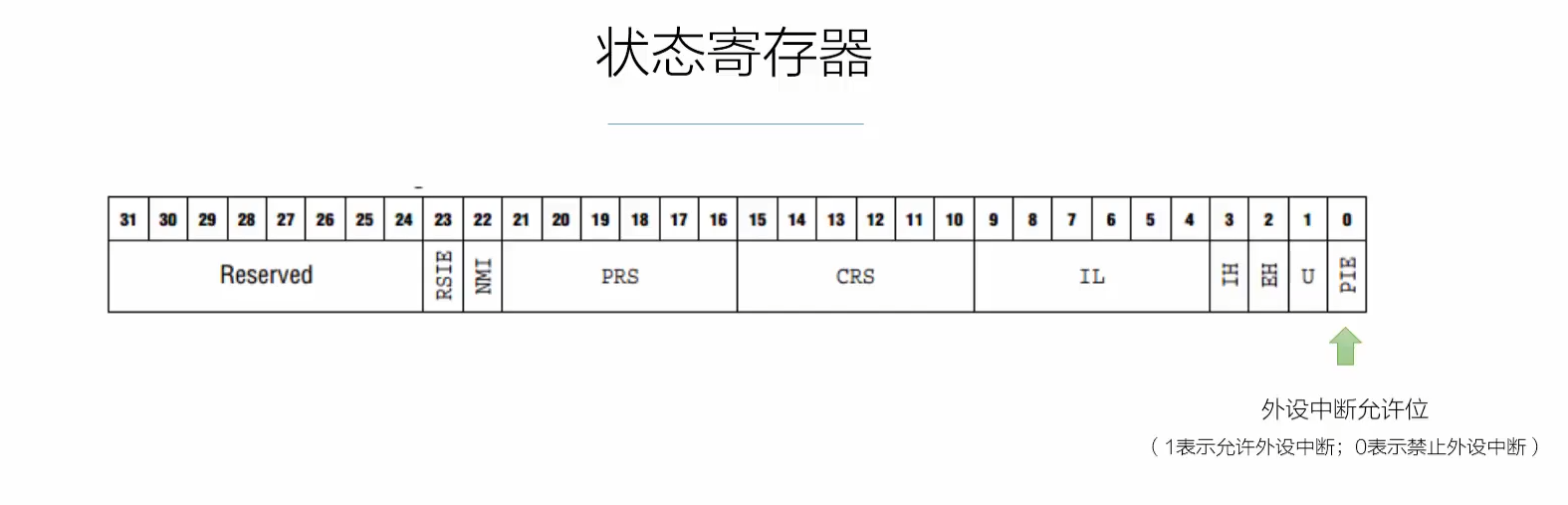

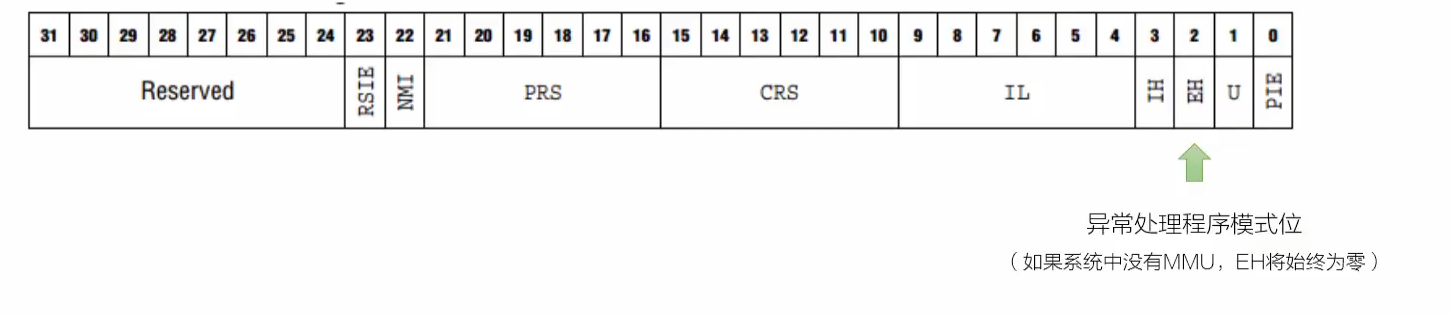

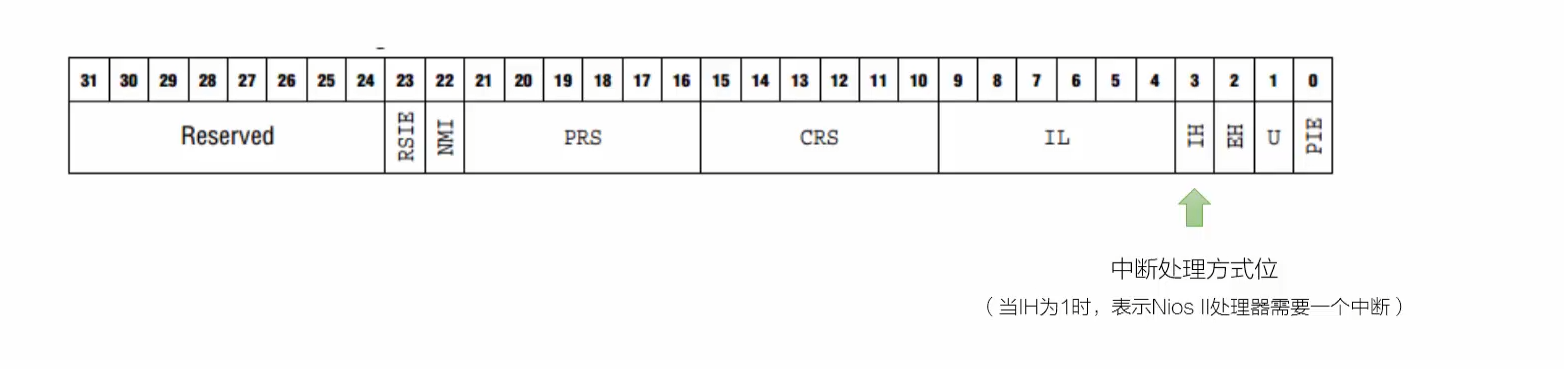

1、status控制寄存器中的PIE位为1;

2、某个中断请求irqn有效;

3、在ienable 寄存器中,该中断源相应位为1;

**中断优先级:**0的优先级最高,1次之,以此类推。

当异常发生后,处理器会依次完成以下工作:

1、把status寄存器内容复制到estatus寄存器中,当保存当前处理器状态

2、清除status寄存器的PIE位为0,禁止所有的硬件中断;

3、把异常返回地址写入ea寄存器(r29);

4、跳转到异常处理地址中。

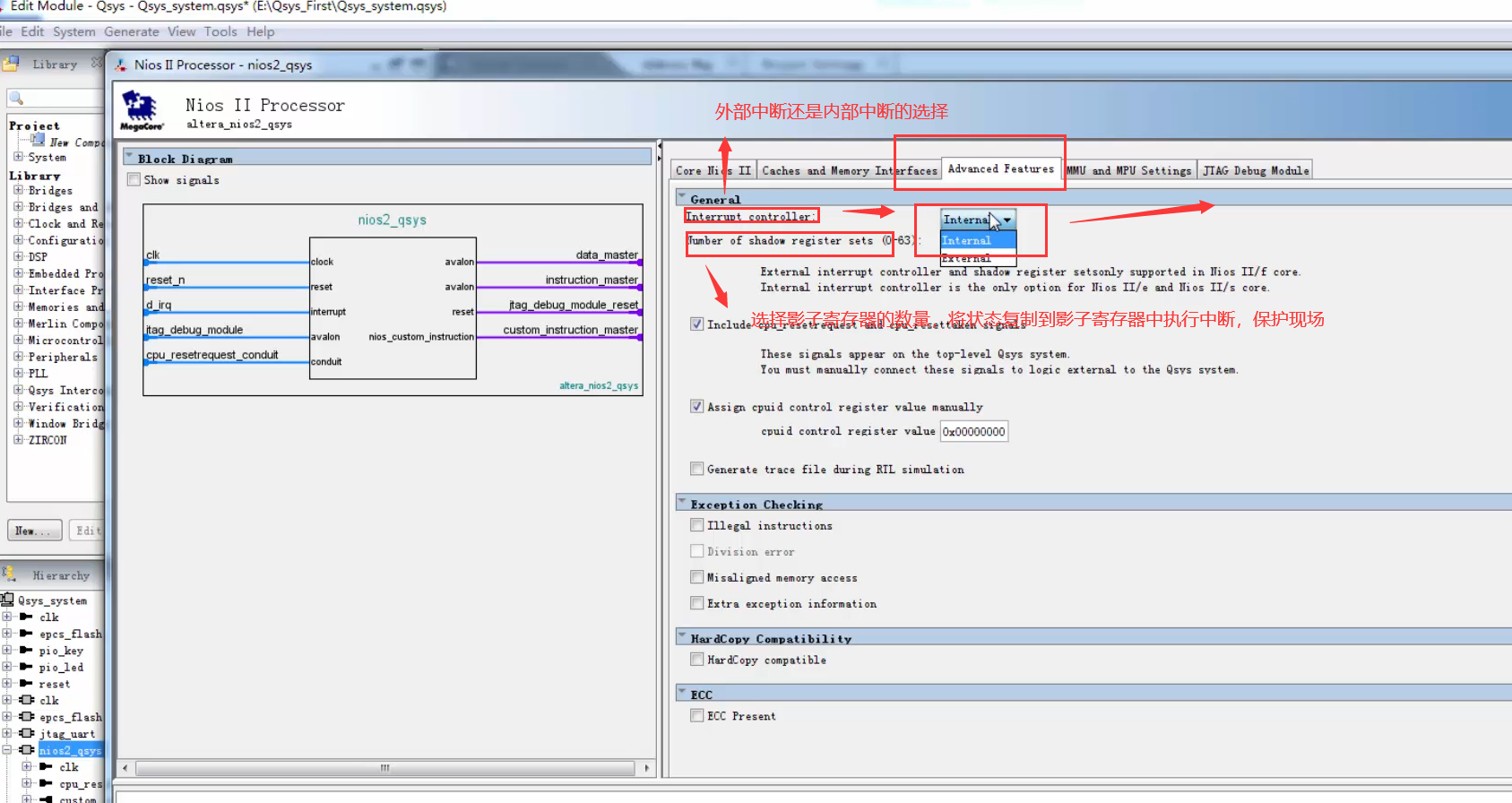

外部中断

外部中断的设置,算估计nios处理器进行设置

其实大部设计采用内部中断即可完成我们设计要求,但是对于实时性高的中断则需要采用外部中断,外部中断支持0到63位,而内部中断只有32位。

影子寄存器组

影子寄存器可以完全的复制寄存器的内容,来完成中断等异常操作,而且因为这个所以外部中断速度比内部中断要快。

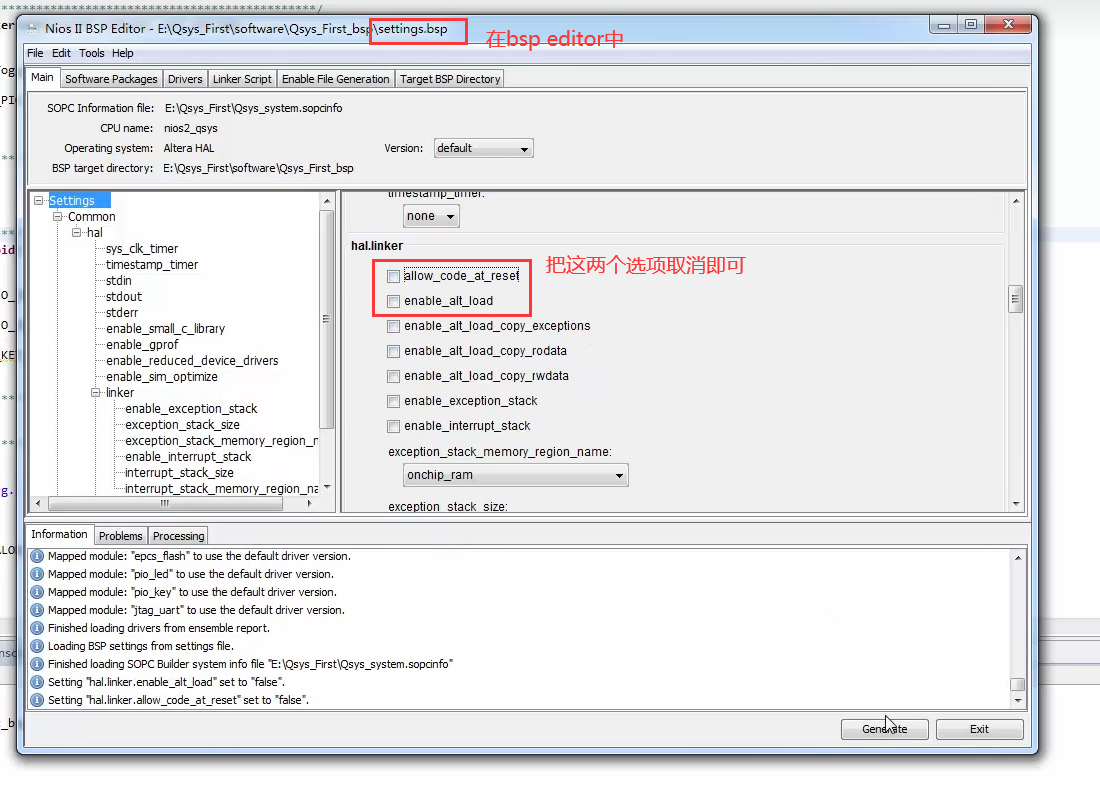

常见的错误

出现launching xxx nios II hardware configuration’has encountered a problem. downloading elf process failed的原因

原因,如果勾选上面两个选项就会导致没有代码搬运这个功能

第五讲

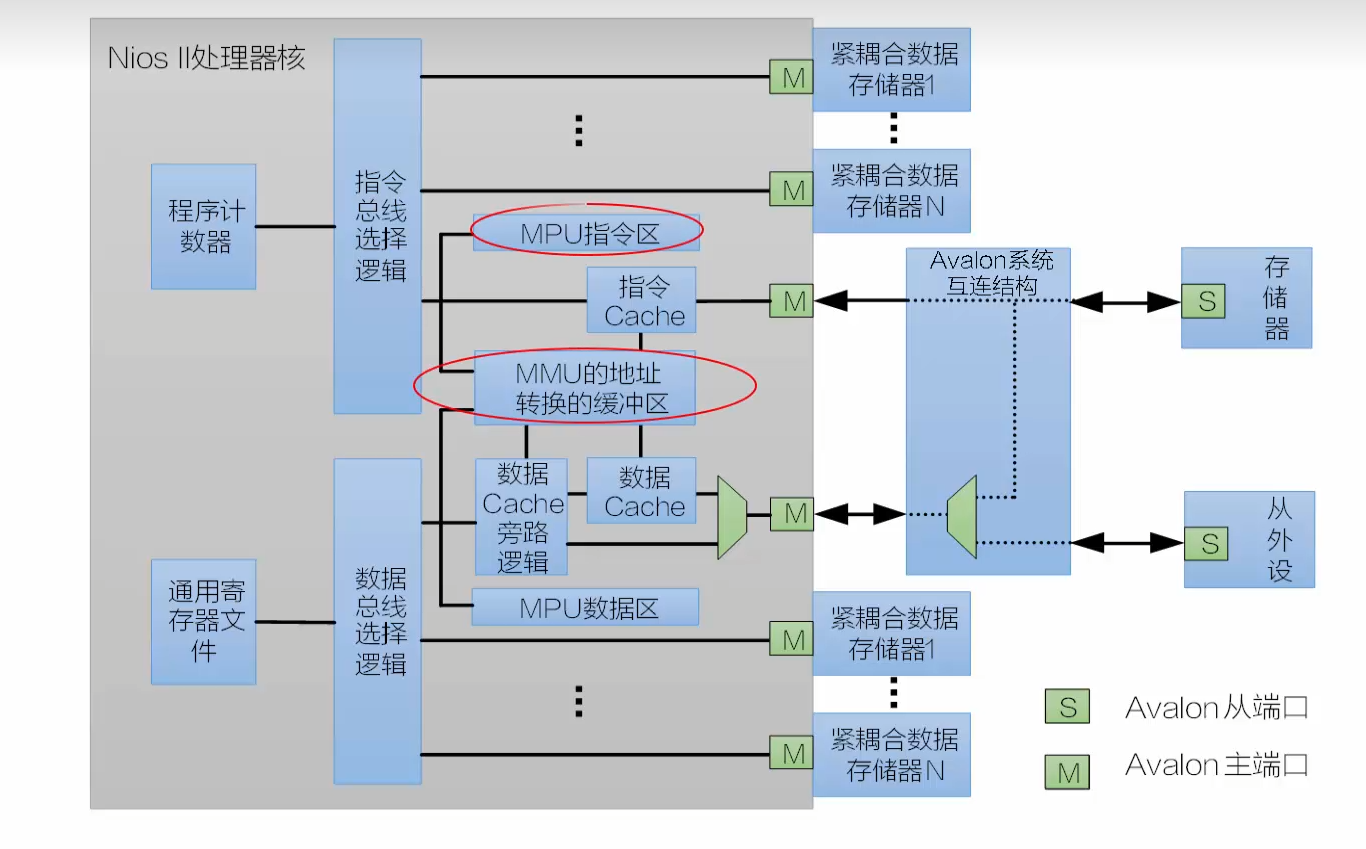

存储器和IO结构

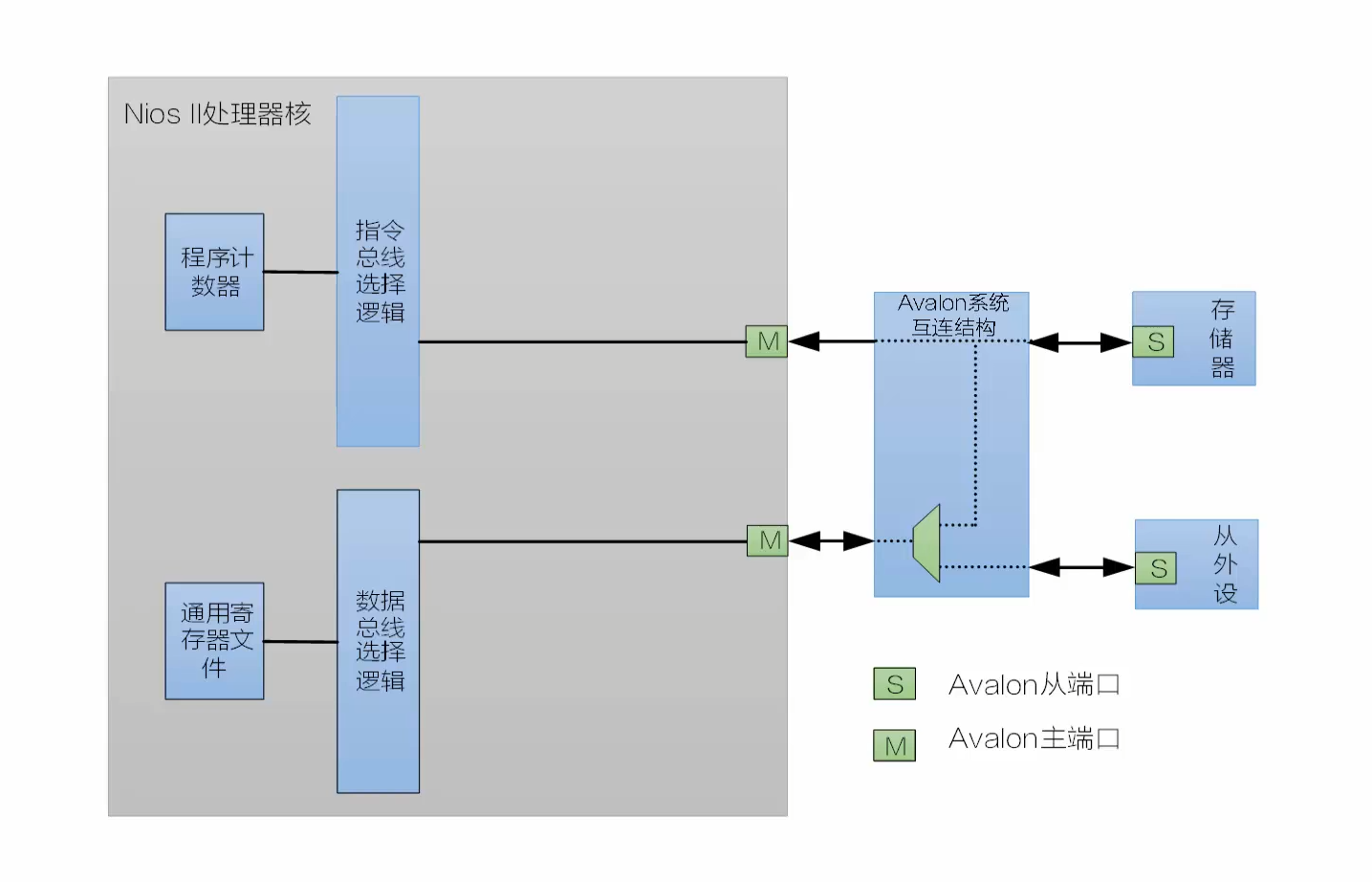

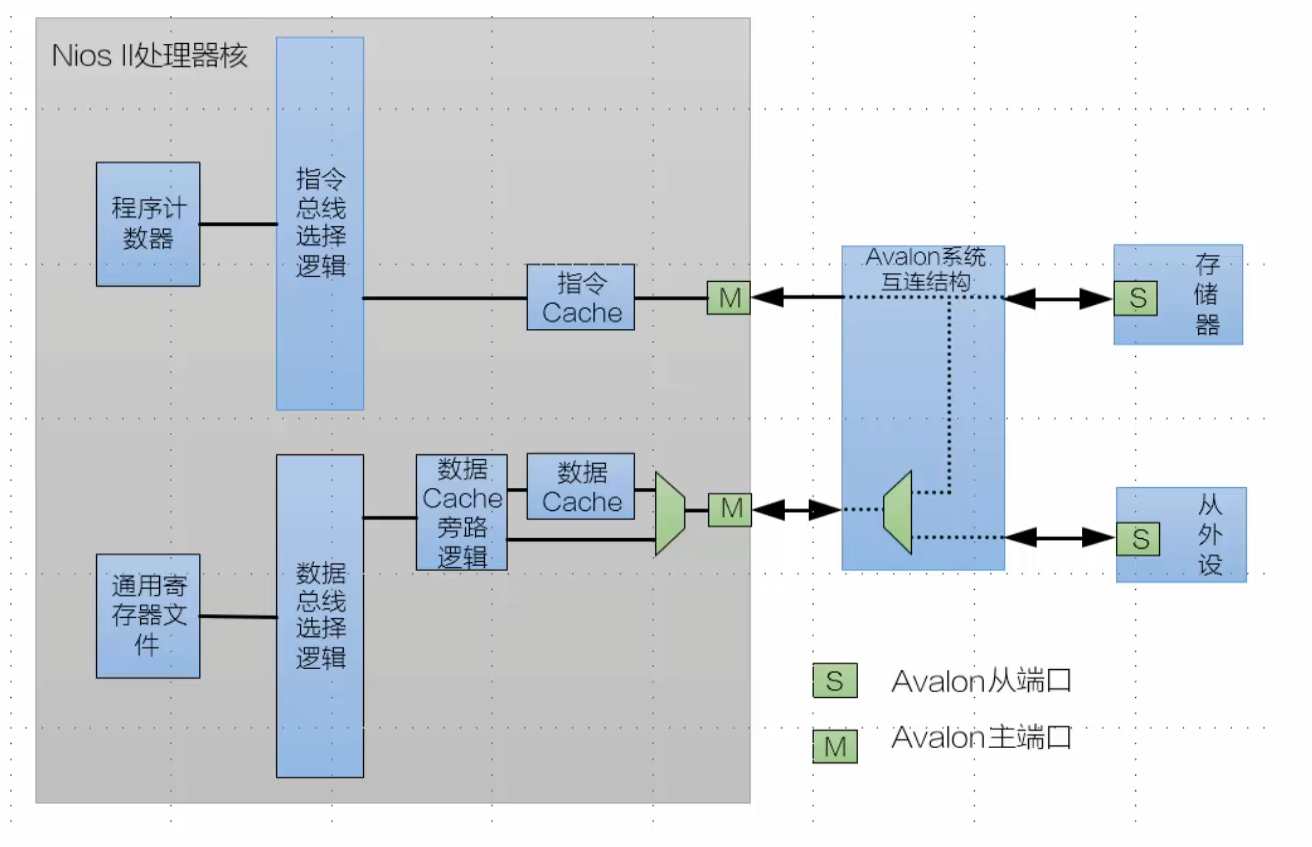

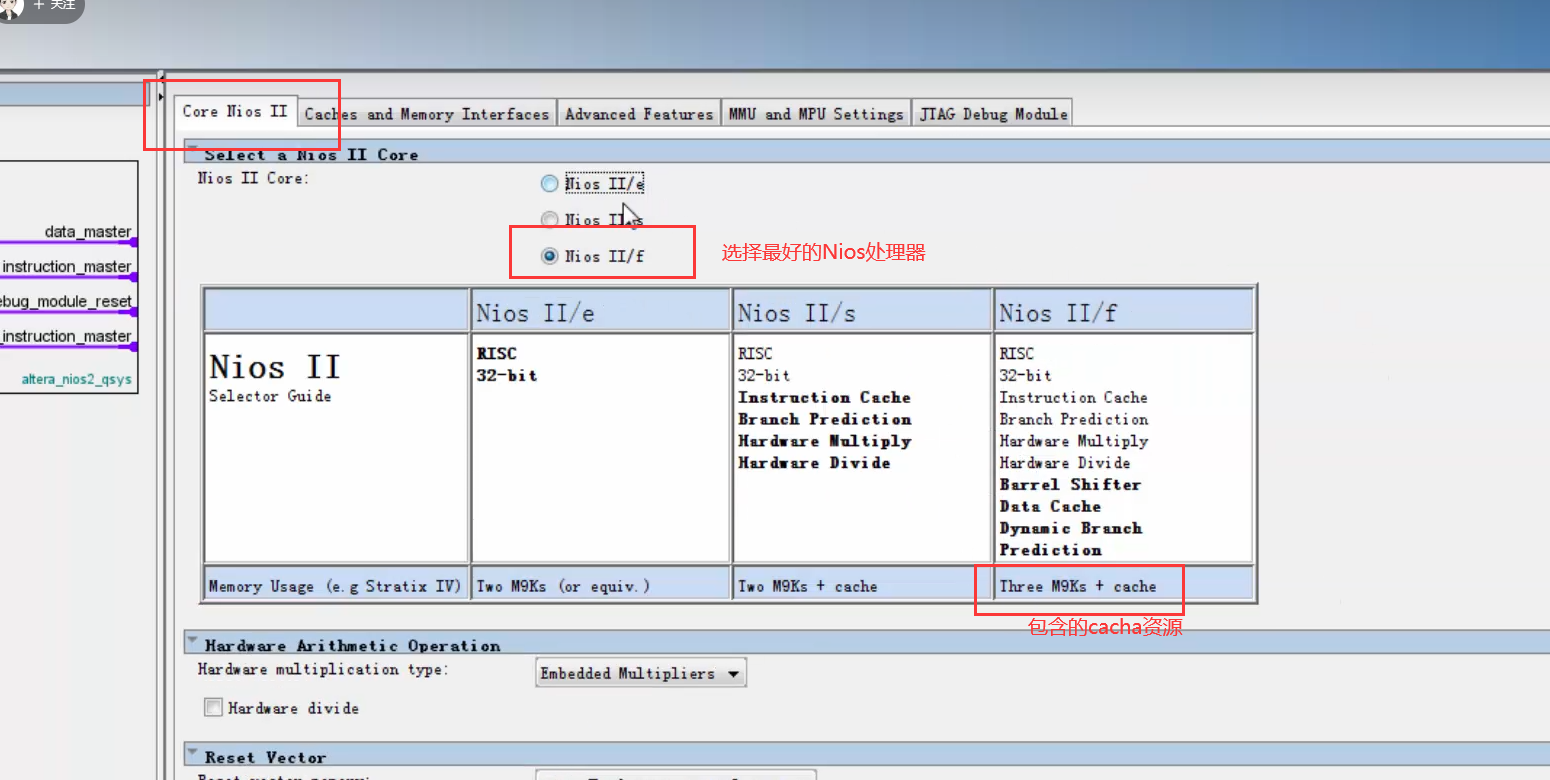

Nios II存储器和IO结构非常的灵活,这就是Nios II处理器系统和传统的微控制器之间的最明显的区别。因为nios II处理器系统可以配置,存储器和外设随着系统的不同而不同,最终使得存储器和IO结构随着系统不同而发生改变。Nios II内核可以使用下面的一种或者多种方式访问存储器和IO

1、指令主端口:Avalon主端口,通过AValon系统互连结构连接到指令寄存器;

2、数据主端口:Avalon主端口,通过AValon系统互连结构连接到指令寄存器;

3、指令高速缓存:Nios II 内核里面的高速缓存;

4、数据高速缓存:Nios II内核里面高速缓存;

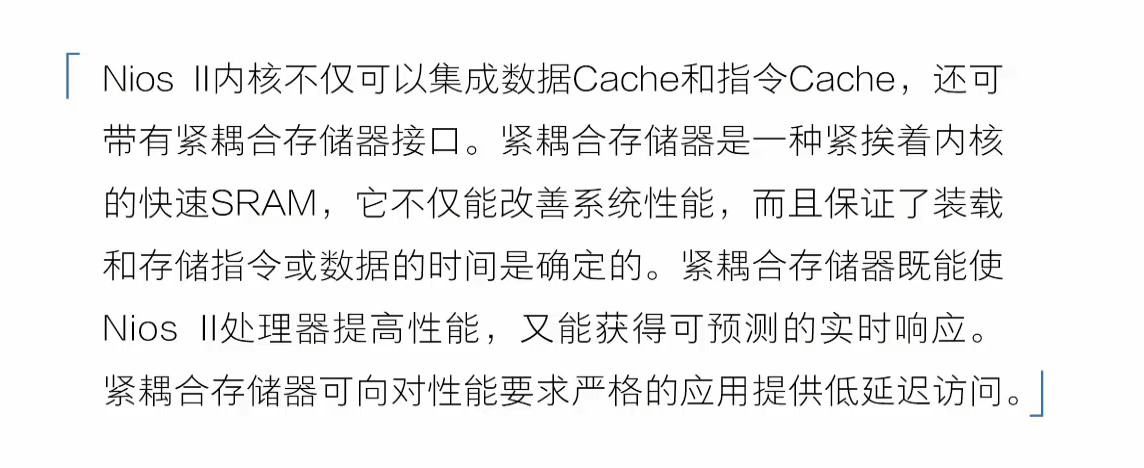

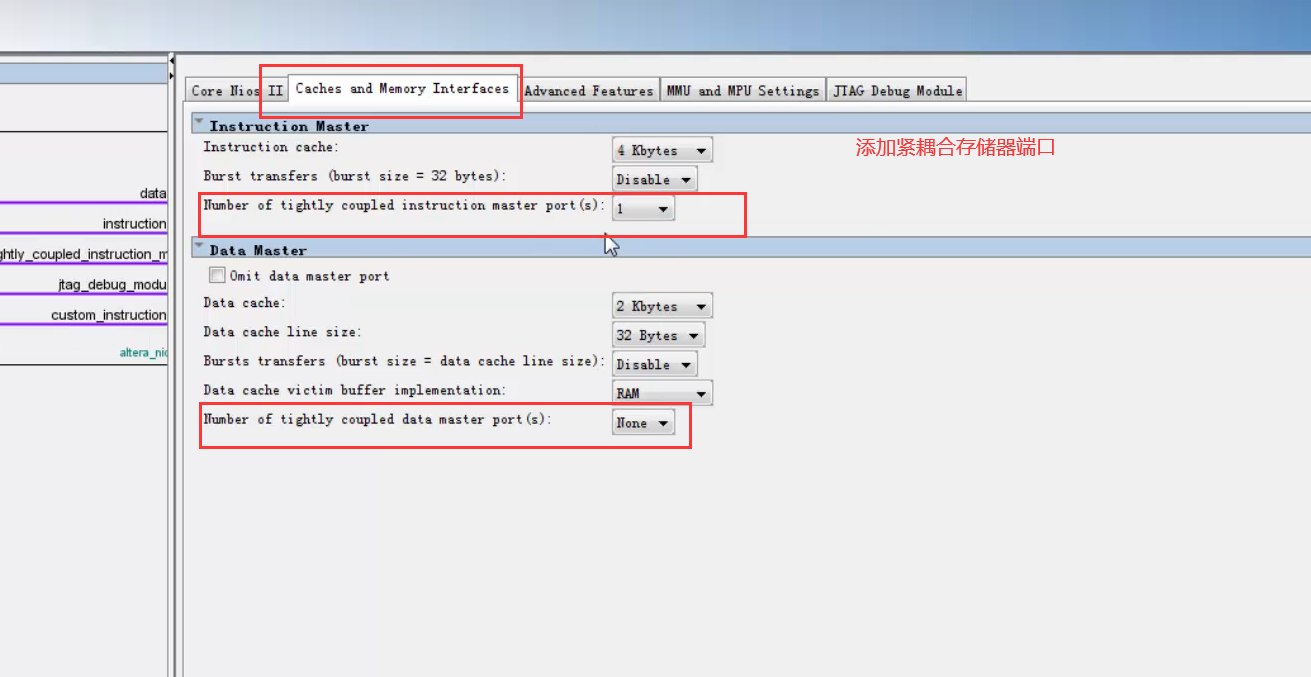

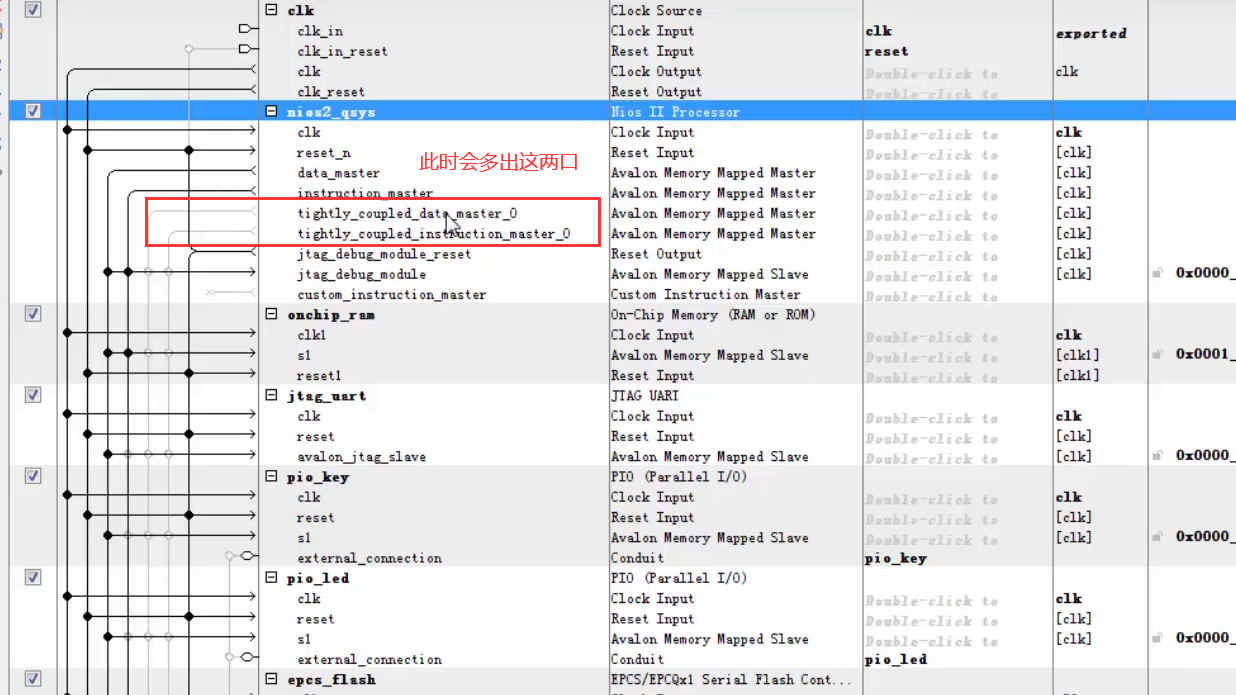

5、紧耦合指令或数据寄存器端口:与Nios II内核外的快速存储器相连

**指令主端口的描述:**指令主端口只执行一个功能,即只对处理器将要执行的指令进行取指,指令主端口不执行任何写操作。

数据主端口:有两个功能

-

当处理器执行装载指令时,从存储器或者外设中读取数据;

-

当处理器执行存储指令时,将数据写入存储器或外设。

补充:哈弗结构就是整个系统的总线明确分为一个数据总线和指令总线,相互独立的。

冯诺伊曼结构:共享数据总线和指令总线的结构。

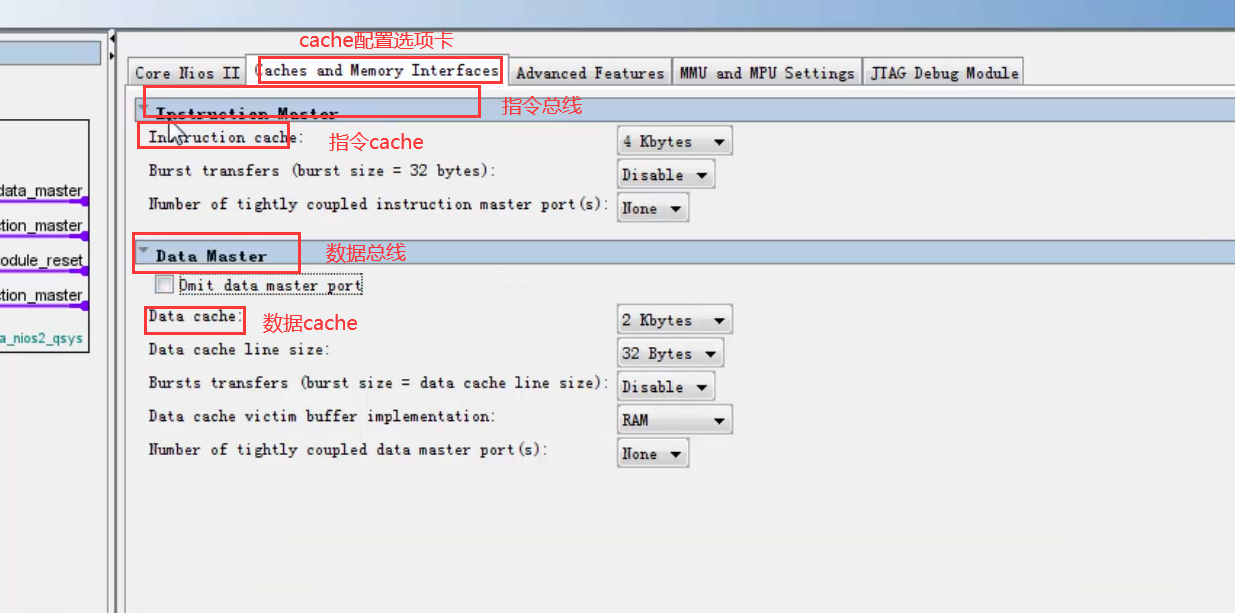

高速缓存(cache)–时间不可预测

如何配置cache:

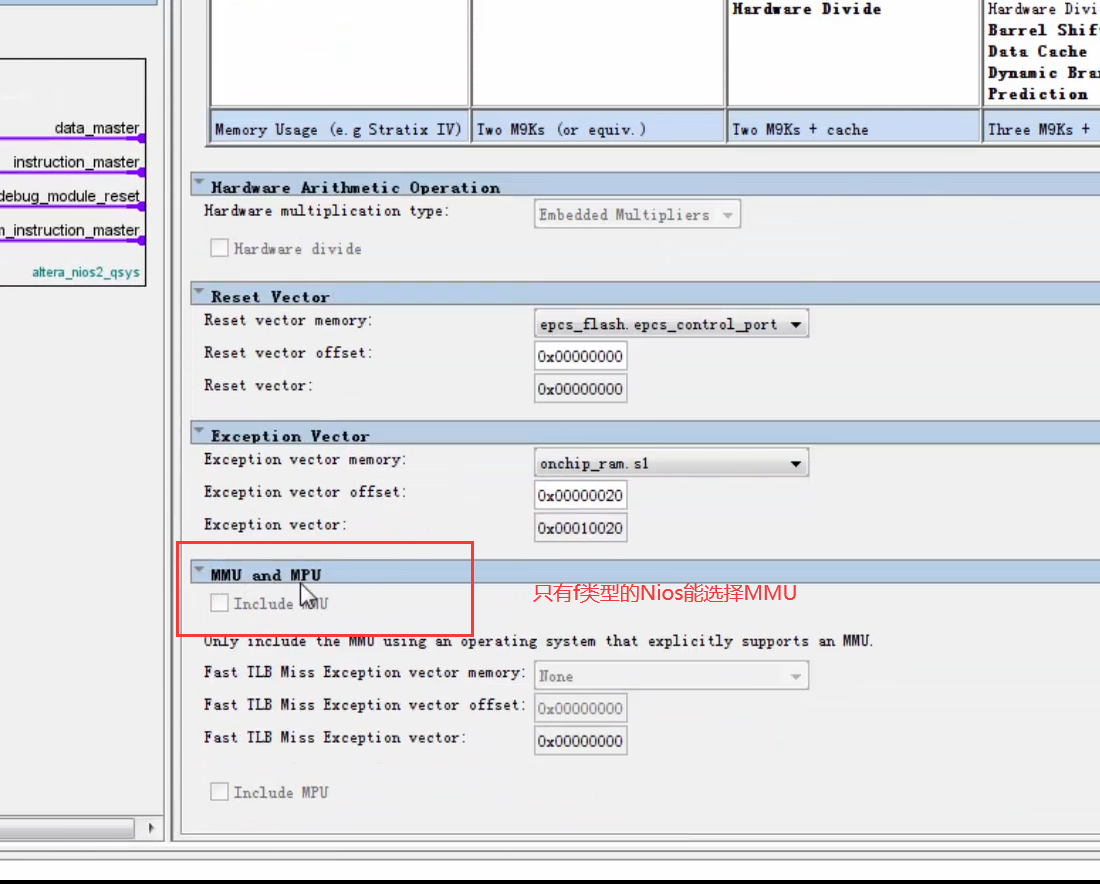

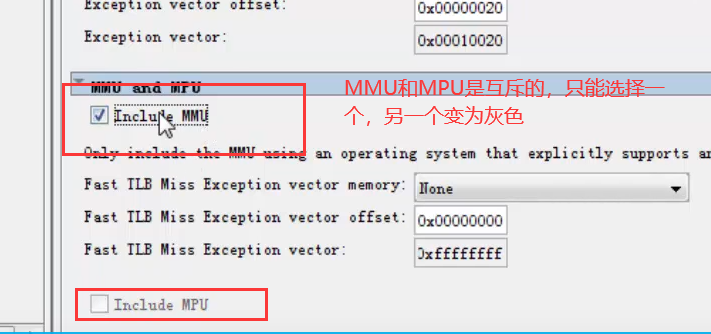

MMU(memory management unit):存储器管理单元,在Nios II/f型的处理器中,可选用MMU用来完成虚拟内存管理这个工作的特定硬件。当然仅仅有硬件是无法实现这一个功能的,还需要一个能够支持虚拟内存的操作系统

MPU(memory protection unit)存储器保护单元:MPU只提供存储器的保护,它是不支持内存映射和管理的

紧耦合指令或数据寄存器端口

添加的方法:

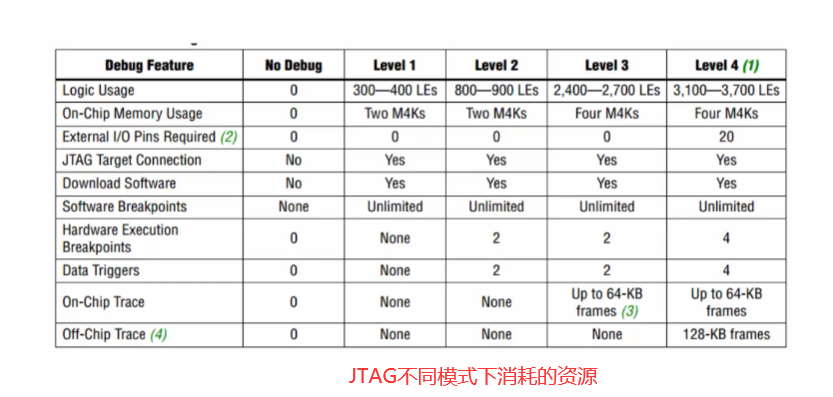

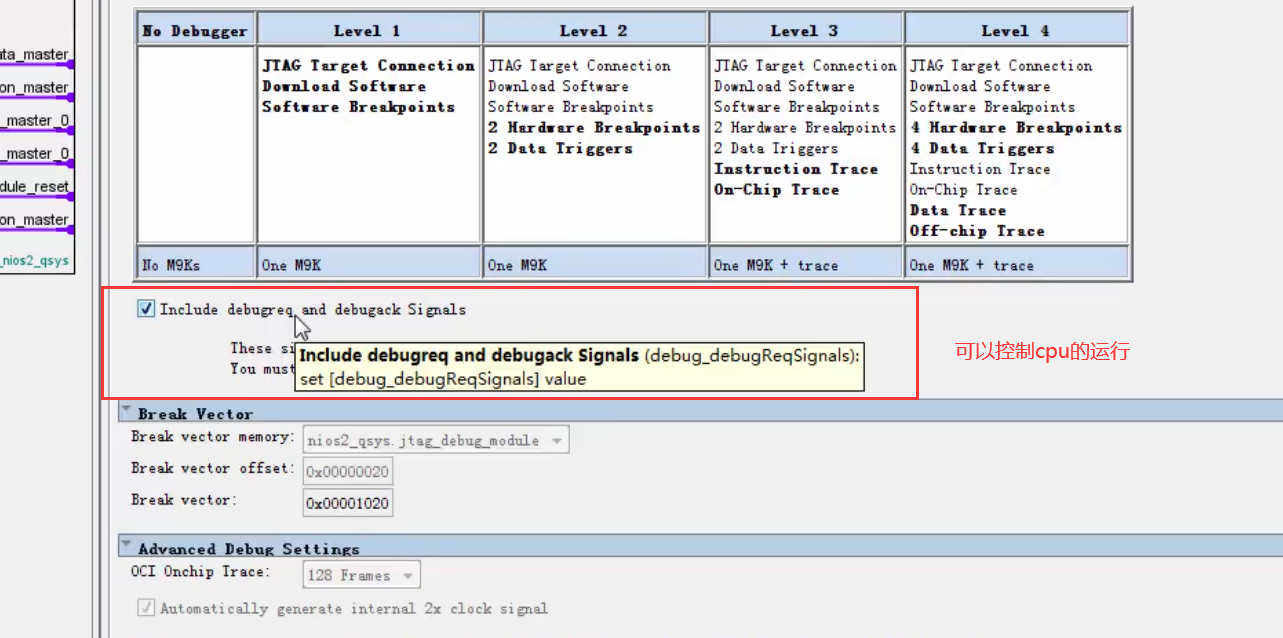

JTAG调试模块

PC上的软件调试工具可以通过JTAG调试模块通信,提供调试和诊断功能

- 把程序下载到存储器中

- 启动和停止程序的执行

- 设置断电和观察点

- 分析寄存器和存储器

- 采集实时的执行跟踪数据

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-hexyIEQL-1667709414497)(https://gitee.com/xzs520xzs/figure_of_typora/raw/master/202211061235539.png)]

--晓凡 2022年11月6日于桂林书- 1

-

相关阅读:

吃鸡大作战:绝密攻略《揭秘吃鸡要领与细节,国际服全方位指南只在此!

知虾数据软件:电商人必备知虾数据软件,轻松掌握市场趋势

数字孪生的技术开发平台

SoC第一个工程hello_world

[C/C++]数据结构 深入挖掘环形链表问题

linux网络协议栈源码分析 - 传输层(TCP的输出)

非关系型数据库-Redis

Reggie外卖项目 —— 小程序开发之短信发送

收藏|0 基础开源数据可视化平台 FlyFish 大屏开发指南

【具身智能】RT-2:视觉-语言-动作模型(VLA)

- 原文地址:https://blog.csdn.net/xzs520xzs/article/details/127713575