-

(4)UART应用设计及仿真验证(整体回顾)

在新公司入职以后,第一个小demo就是设计一个UART模块,支持apb2.0,支持中断上报,支持环回,支持有效数据位可配置,支持校验可配置,支持FIFO水位线可配置,支持波特率可配置等等。UART最早是在补习班的时候接触的,当时学习地很吃力,对它地理解不算深刻。当时实现的只有发送和接收,其实本质上就是完成一组数据的串转并或者并转串,并不涉及其他的内容。即之前看到的几篇博客都是在实现那个,不过当时的一些基础认识对于初学者认识UART是有帮助的。

为了完成实际工程可用的UART模块,这里我把整个的模块设计流程和一些关键点信息做如下总结,供大家交流学习。

(1)详设文档

当我们拿到项目组下发的研制规范文档后,就可以开始分析模块的功能、端口、时序这些基础的内容。所有的这些整理成新的文档就是详设文档。详设文档的一个原则就是,写的越详细越好。整体划分成几个子模块,子模块间的逻辑设计(端口连接),子模块内部的功能定义。(2)模块划分

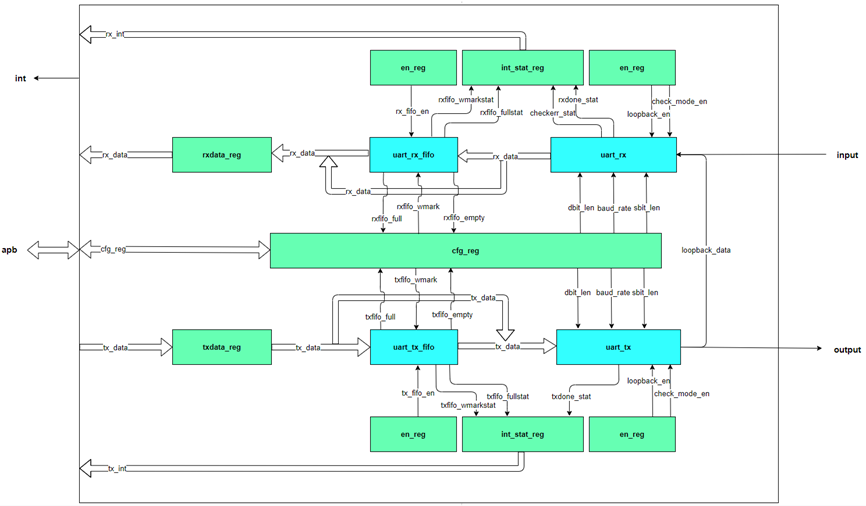

上图是本次的UART模块结构框图,主要分为5个子模块:apb_cfg配置寄存器;rx_fifo接收端fifo;rx接受端口;tx_fifo发送端fifo;tx发送端口。模块的划分依据就是各模块的功能不同。

配置寄存器 -

相关阅读:

Python自动化测试实战 真实项目-Web自动化测试从方案到实战落地(二)

vue-element-admin+springboot登录功能实现

超级签名封号掉签该怎么办

用acme.sh给网站域名,申请免费SSL永久证书(自动续期)

python图

创建第一个鸿蒙开发项目

计算机的分类

【Python学习笔记】第二章循环:while循环,for循环,break和continue语句,死循环,循环的嵌套

05. 聚类---K(k-means)均值

Hashing to elliptic curve算法改进

- 原文地址:https://blog.csdn.net/CAUC_learner/article/details/126249289