-

FPGA VTR quickstart example

VTR Quick Start — Verilog-to-Routing 8.1.0-dev documentation (verilogtorouting.org)

Setting Up VTR

我的 VTR 安装路径:

VTR_ROOT = /vtr/vtr-verilog-to-routingRunning VPR

用VPR工具在特定的FPGA架构上实现一个简单的预合成电路(由lut和Flip-Flops组成)

Running VPR on a Pre-Synthesized Circuit

创建一个工作目录并移动到这个目录下:

mkdir -p /vtr_work/quickstart/vpr_tseng #Make a working directory cd /vtr_work/quickstart/vpr_tseng #Move into the working directory- 1

- 2

指定

tseng电路,存放在:$VTR_ROOT/vtr_flow/benchmarks/blif/tseng.blif指定

EArchFPGA结构,存放在:$VTR_ROOT/vtr_flow/arch/timing/EArch.xml将这些文件传递给VPR工具,并指定路由的通道宽度为100:

--route_chan_wdith 100/vtr/vtr-verilog-to-routing/vpr/vpr /vtr/vtr-verilog-to-routing/vtr_flow/arch/timing/EArch.xml /vtr/vtr-verilog-to-routing/vtr_flow/benchmarks/blif/tseng.blif --route_chan_width 100- 1

这将产生大量的输出,因为VPR实现了电路,应该看到类似的东西:

这表明VPR成功了,以及VPR需要多长时间运行

VPR生成的各种结果文件,这些文件定义了电路实现:

Visualizing Circuit Implementation

通过以下方法可视化电路实现:

重新运行VPR的分析阶段(

--analysis)启用VPR的图形用户界面(

--disp on)这可以通过运行以下命令来实现:

/vtr/vtr-verilog-to-routing/vpr/vpr /vtr/vtr-verilog-to-routing/vtr_flow/arch/timing/EArch.xml /vtr/vtr-verilog-to-routing/vtr_flow/benchmarks/blif/tseng.blif --route_chan_width 100 --analysis --disp on- 1

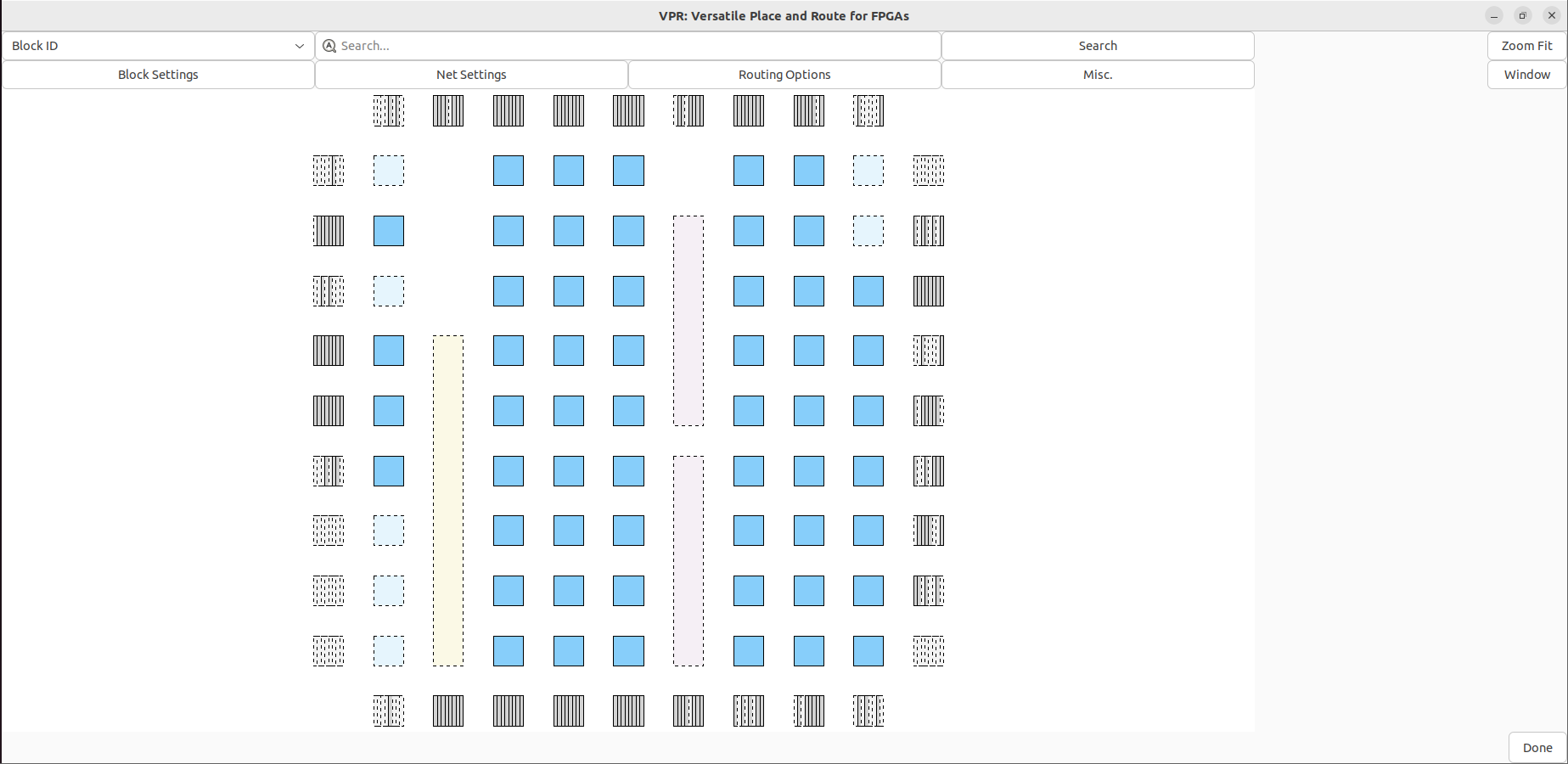

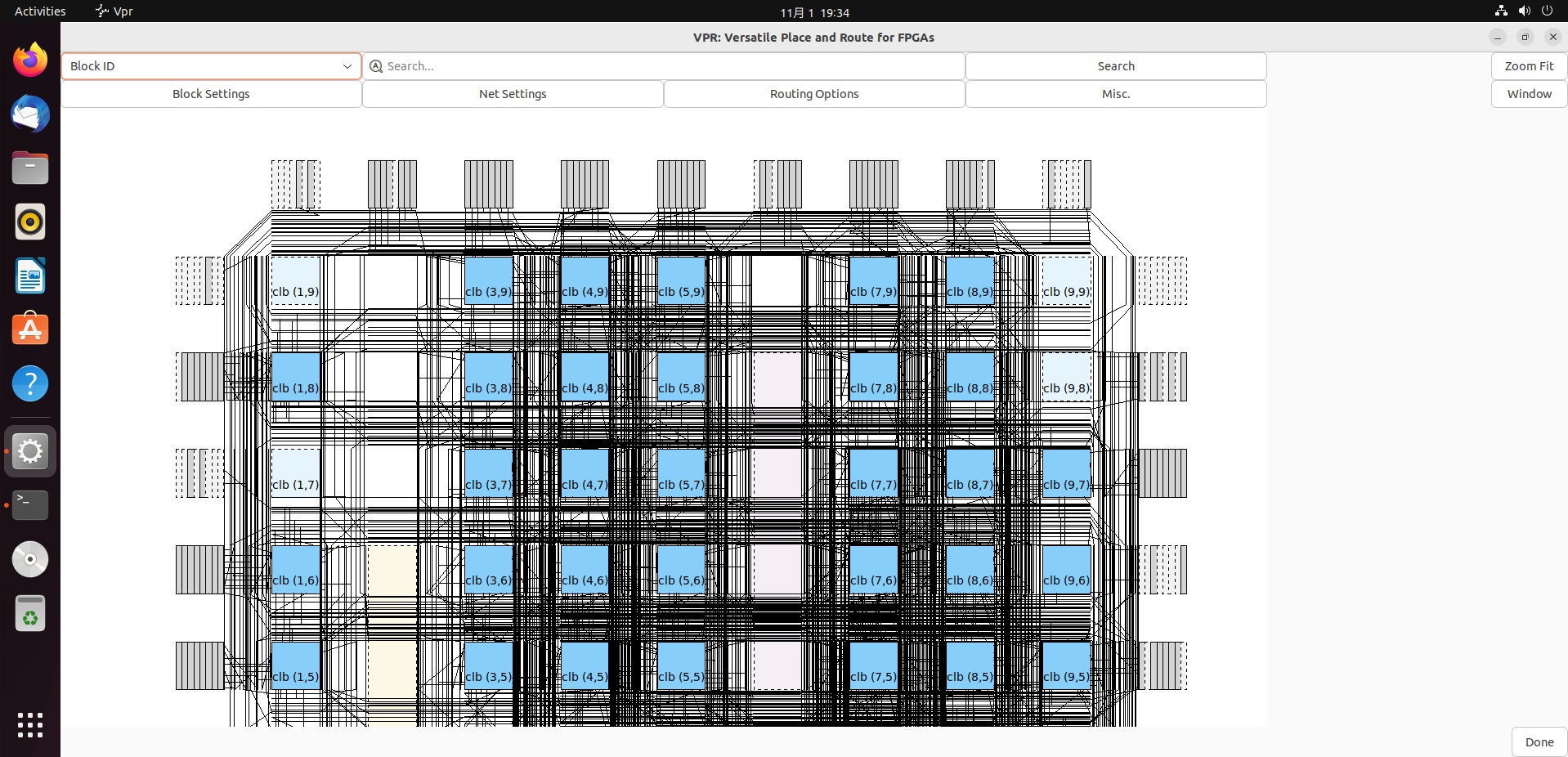

运行结果:

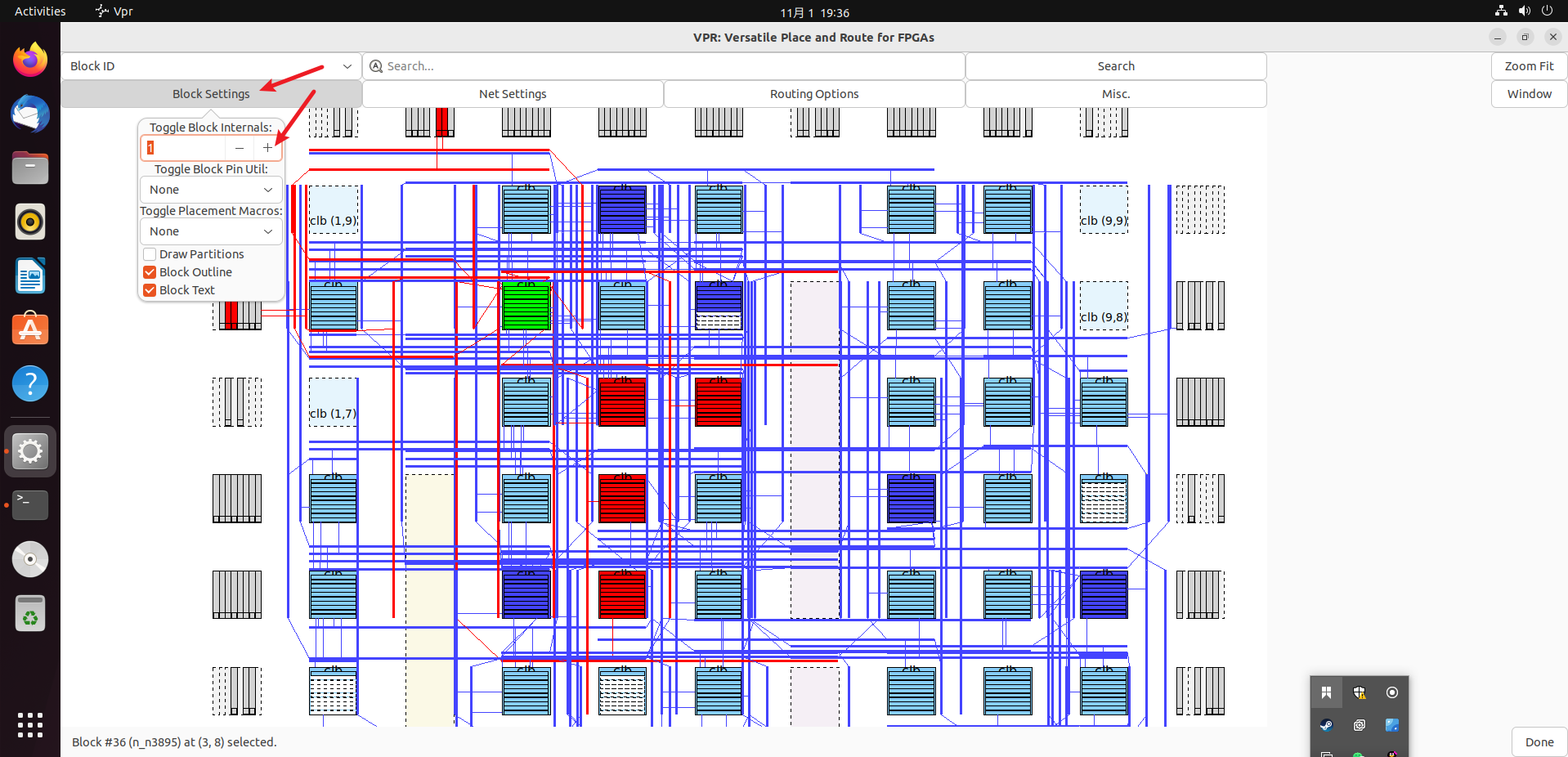

View the connectivity of a block:

View the internals of a logic block:

蓝色输入,红色输出

Running the VTR Flow

在已有的FPGA架构上实现我们自己的电路:

-

首先使用Verilog硬件描述语言(HDL)对电路进行行为描述,快速简洁地定义电路的行为

-

然后,使用VTR流将行为Verilog描述合成到电路网络列表中,并实现到FPGA上

verilog文件:

$VTR_ROOT/doc/src/quickstart/blink.v*这个Verilog代码创建一个顺序的5位寄存器(r_counter),每个时钟周期递增。如果计数低于16,它驱动输出(o_led)高,否则它驱动低

Manually Running the VTR Flow

创建一个工作目录,并移动到这个目录:

mkdir -p /vtr_work/quickstart/blink_manual cd /vtr_work/quickstart/blink_manual- 1

- 2

接下来我们需要运行三组主要的工具:

-

Odin II:执行“synthesis”转换我们的行为Verilog(

.v文件)转换成电路网表(。由逻辑方程和FPGA架构原语(Flip-Flops, adders等)组成 -

ABC:执行“‘logic optimization”,简化电路逻辑,并执行“technology mapping”,将逻辑方程转换为可在FPGA上使用的查找表(LUTs)

-

VPR:执行封装,放置和路由的电路,以实现它的目标FPGA架构

Synthesizing with ODIN II

首先,我们将在Verilog文件上运行ODIN II,将其合成为一个电路网表,提供以下选项:

指定目标FPGA架构:

-a $VTR_ROOT/vtr_flow/arch/timing/EArch.xml指定合成的verilog文件:

-V $VTR_ROOT/doc/src/quickstart/blink.v指定生成的.blif电路网络列表的名称:

-o blink.odin.blifcommand:

/vtr/vtr-verilog-to-routing/ODIN_II/odin_II -a /vtr/vtr-verilog-to-routing/vtr_flow/arch/timing/EArch.xml -V /vtr/vtr-verilog-to-routing/doc/src/quickstart/blink.v -o blink.odin.blif- 1

运行结果:

Optimizing and Technology Mapping with ABC

优化和技术映射我们的电路使用ABC,提供选项:

-c