-

FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

系列文章目录

二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写

五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真

六、FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

七、FPGA学习笔记(七)verilog的深入学习之任务与函数(语法篇3)

Modelsim单独仿真

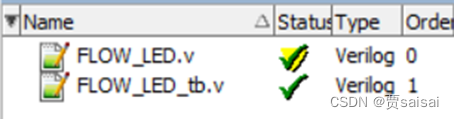

Modelsim中新建项目后,导入编写的Testbench文件和程序文件,点击compile all编译,没有错误后,点击start simulation 开始仿真。

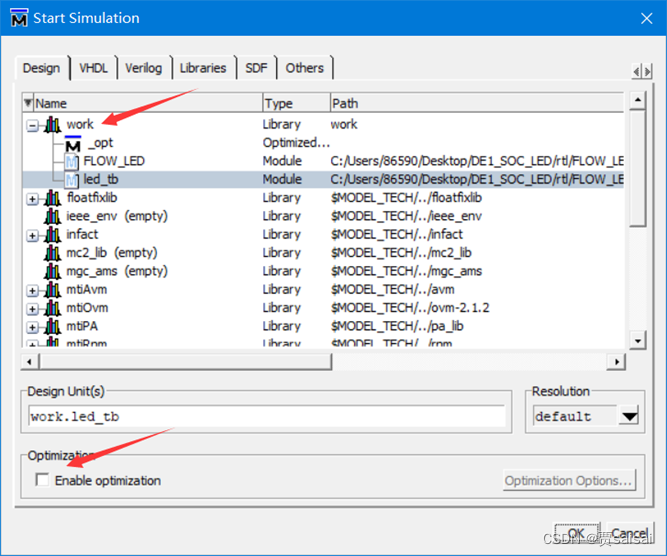

在work中选择编写Testbench时定义的仿真模块,取消勾选使能优化。

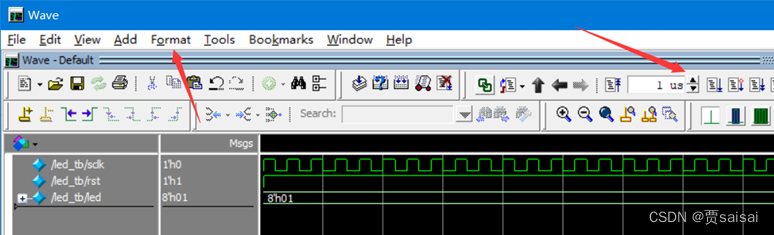

点击Add Wave添加参数的波形。

利用Format可以更改显示格式,利用快捷工具栏修改仿真时间。

Quartus联合仿真

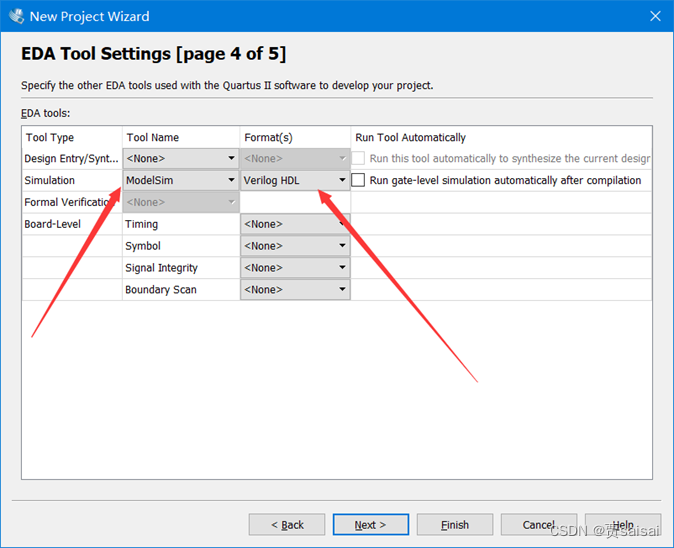

首先,需要在quartus中设置仿真的类型,可以在新建项目时设置

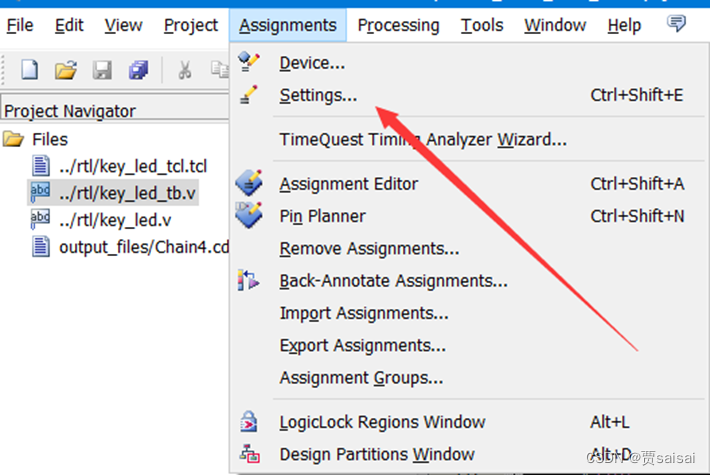

或者可以在Assignments中的Setting中设置

设置modelsim的软件路径

利用Quartus自动生成仿真文件Testbench框架

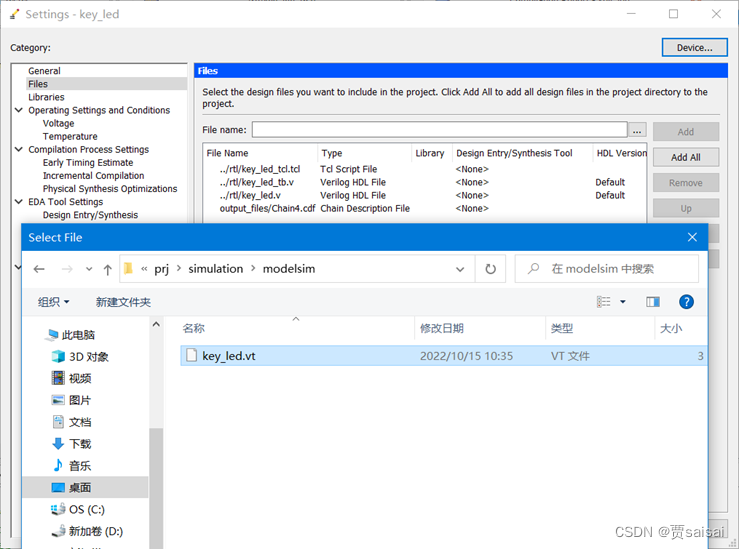

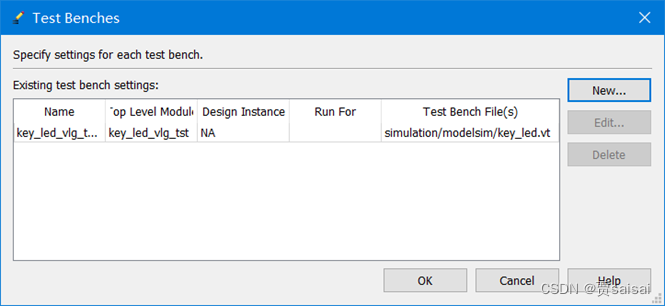

提示没有错误后,在Settings中将生成的仿真文件.vt添加到项目文件中

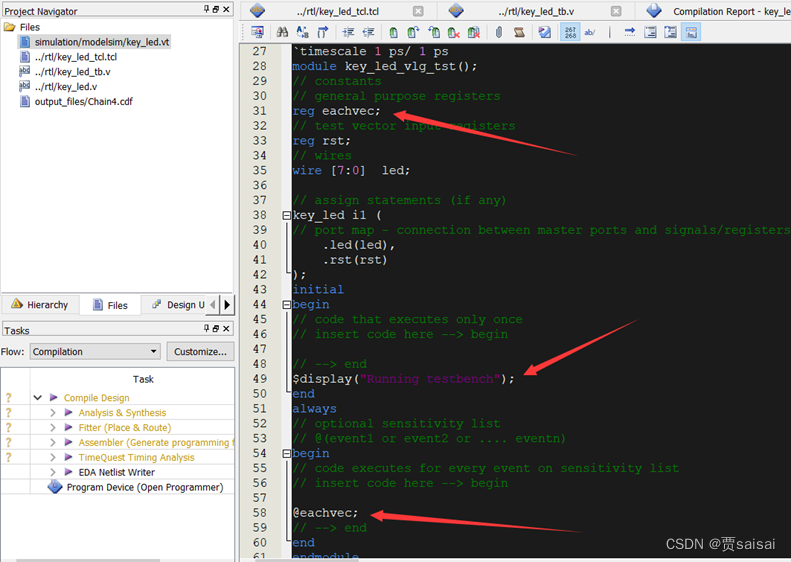

打开.vt文件后,一些红色箭头标注的不需要,然后在里面添加自己需要的内容。

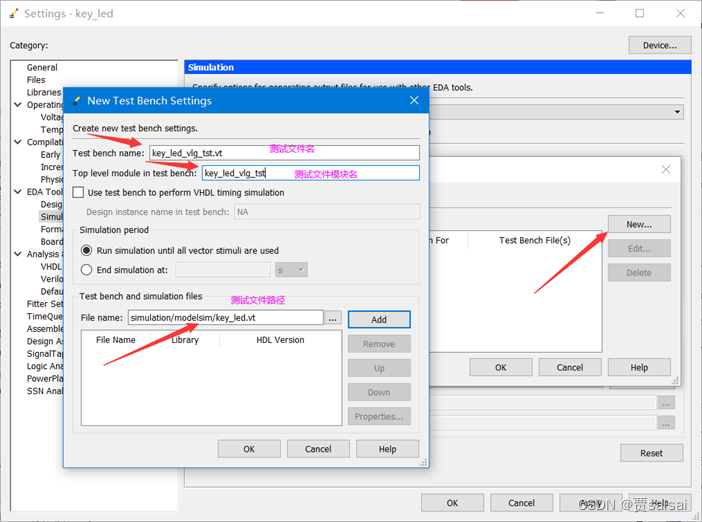

添加完成后设置编译的仿真文件

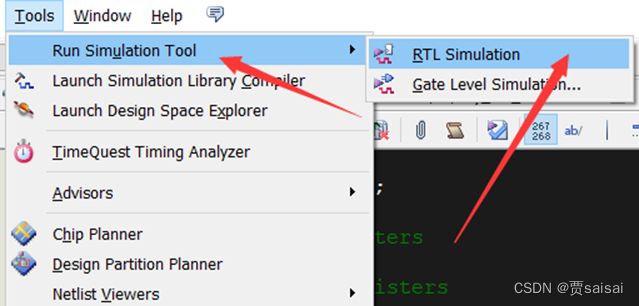

添加完成后开启仿真,quartus就会自动打开modelsim进行仿真。

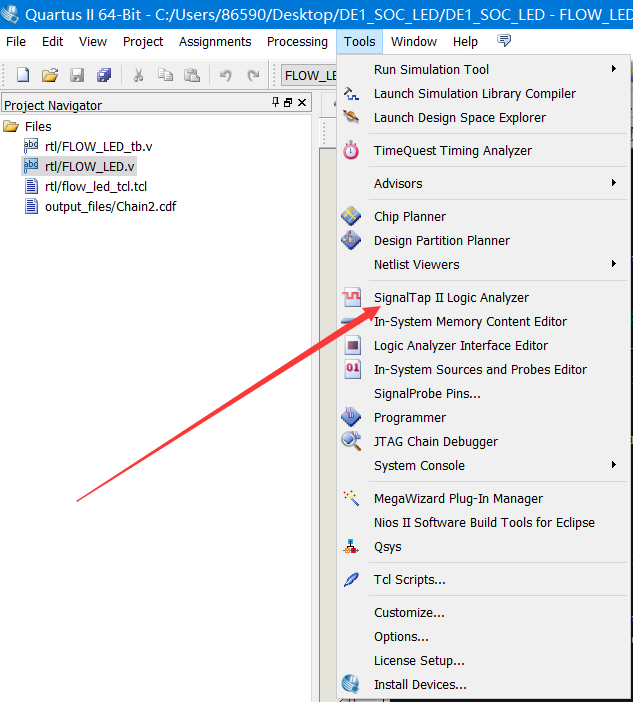

Signal Tap II使用

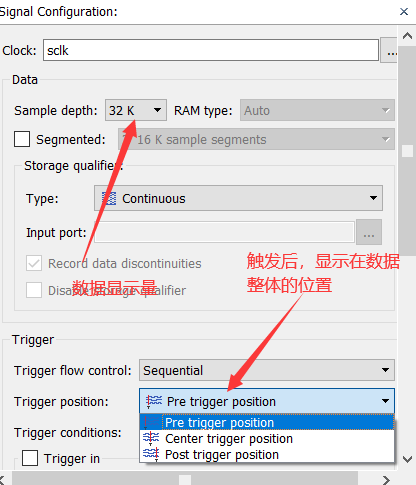

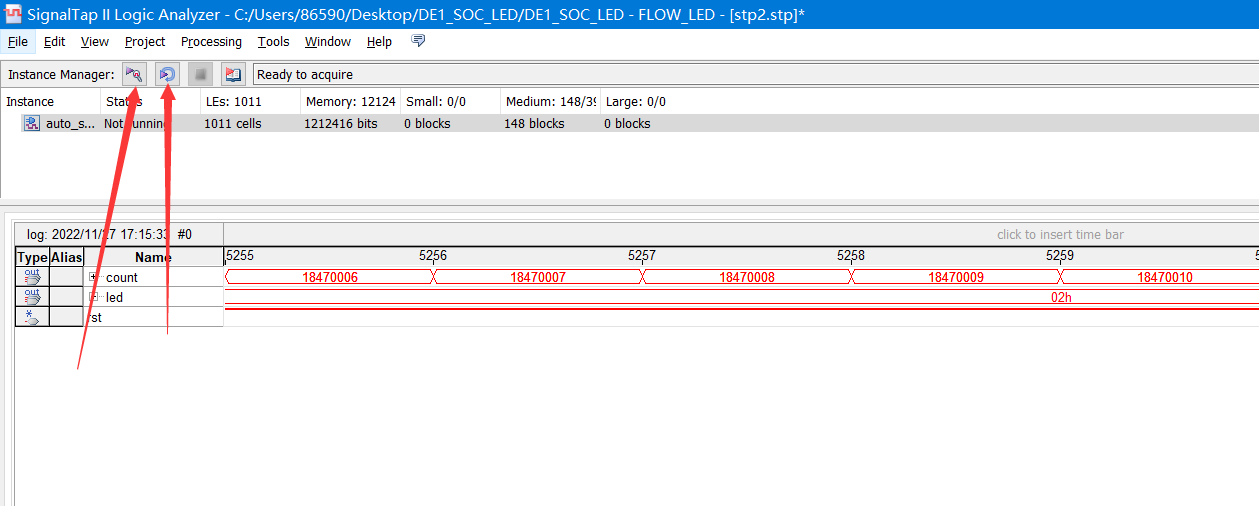

下图是设置的采样时钟,所以如果用这个时钟去采集同样频率的sclk,是采集不到的

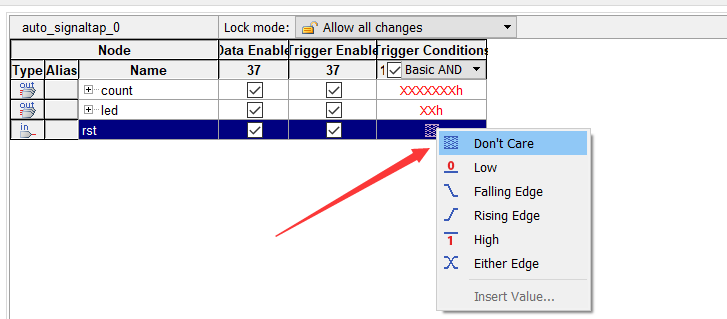

这里就可以选择按键复位的触发方式,在数据显示界面就可以看到实体按键按下前后数据的变化,结合上面的触发后数据显示位置,来观测数据

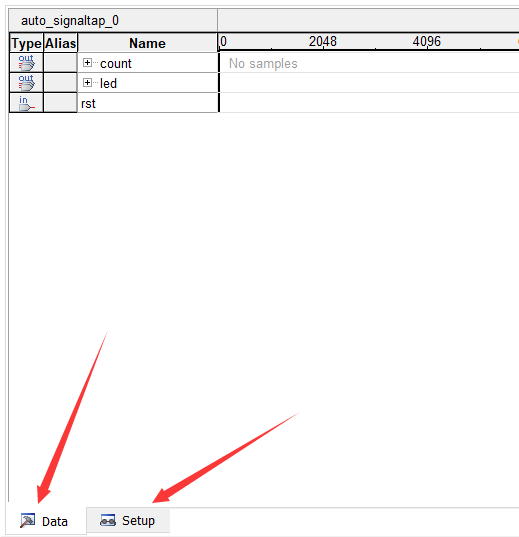

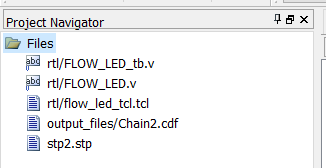

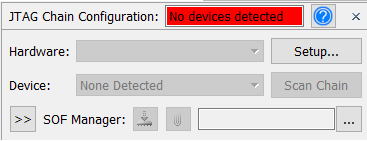

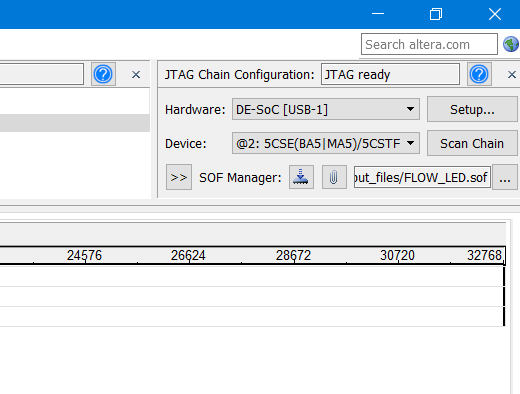

设置和数据显示切换设置完成后,保存到项目中,编译生成下载,也可以在这个界面里下载

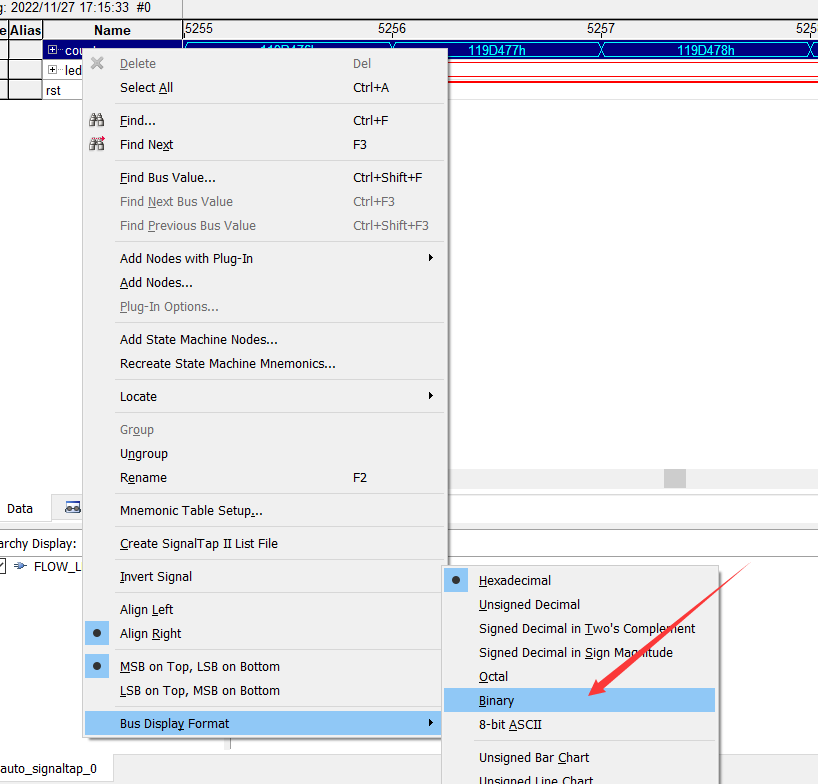

切换数据显示格式:

数据采集开始:

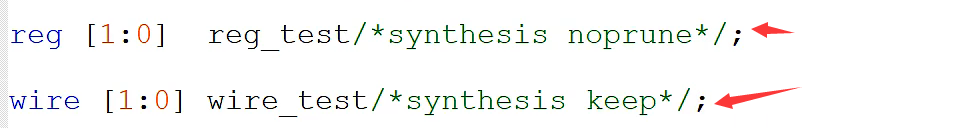

下图中/* */可以防止前面定义的信号被优化(如果编译器发现这两个变量对模块输入输出没有影响,就会优化),这样signal tap才能有这个变量。

当然如果被定义了,但是其他程序没有使用,还是没用没有这个变量

-

相关阅读:

开源一个RAG大模型本地知识库问答机器人-ChatWiki

ChatGPT扇动翅膀后带来的蝴蝶效应

2024年java面试--mysql(3)

【C++】STL — vector的使用 + 模拟实现

【Linux从0到1】第十四篇:HTTP&&HTTPS

视联网四方面优势引领行业技术

多表查询以及外键约束

网上花店销售系统(附源码+课件+讲解+资料+数据库)

20231018 自然常数的存在性

1156 Sexy Primes – PAT甲级真题

- 原文地址:https://blog.csdn.net/zerokingwang/article/details/127336286