-

【UCIe】UCIe Data to Clock

🔥点击查看精选 UCIe 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/127414439】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

1. 简介

CDR (Clock and Data Recovery) 两大功能:时钟恢复,数据恢复。但 UCIe 没有 CDR ,UCIe 自带一对前向时钟线,无需进行时钟恢复,只需进行数据恢复。UCIe 需要 Data to Clock Training

Data to Clock Training 是什么意思?笔者没有特别明白,百度、Google 这个词也没查到比较好的解释。笔者理解,Data to Clock Training 是指通过调整 Data、Clock、Valid Lane 的参考电压等电气参数以及 Clock Phase,使得接收端 Clock 能够尽可能准确地采样在 Data 眼睛张得最开的位置,从而获得符合系统要求的传输性能。

当然,UCIe 不止有 Data to Clock Training,在 Data to Clock Training 之前还有 Valid to Clock Training,其跟 Data to Clock 方法类似,此处按下不表。UCIe 1.0 文档中提到的 Full Data to Clock Training 即包含了 Valid 在内的 Data to Clock Training。

2. 基本原理

UCIe PHY 初始化及训练期间会多次调整电气参数或时钟相位,并进行多次单个时钟相位的单点式 Data to Clock Point Test,或者进行多次不同相位插值扫描式的 Data to Clock Eye Width Sweep Test。发起 Data to Clock Test 的主体可以是 Tx,也可以是 Rx,不同 LSM 状态需求不同。比如

MBTRAIN.VALVREF、MBTRAIN.DATAVREF、MBTRAIN.VALTRAINVREF、MBTRAIN.DATATRAINVREF及MBTRAIN.RXDESKEW状态时调整 Rx 参考电压,则由 Rx 发起 Data to Clock Test。MBINIT.REPAIRMB、MBTRAIN.VALTRAINCENTER、MBTRAIN.DATATRAINCENTER1、MBTRAIN.DATATRAINCENTER2及MBTRAIN.LINKSPEED状态时由 Tx 发起 Data to Clock Test。发起 Data to Clock Test 的一端负责向对端发送 Sideband Msg,与对端沟通要采用的 Data to Clock Training 参数,比如 LFSR (Linear Feedback Shift Register,线性反馈移位寄存器) Pattern、Burst Mode、Error Threshold 等。在得到对端的响应后正式开始 Data to Clock Test。

2.1 测试电路

Data to Clock Test 开始之后,发送端生成并发送测试 Pattern,接收端接收到测试 Pattern 后与其本地参考 Pattern 进行比较。为保证准确发现链路问题,链路收发端采用相同的 LFSR,收发端同步启动 Pattern Generator 并同步推进,每个 UI (Unit Interval) 都要进行比较。在测试完毕后,对 LFSR 进行复位。

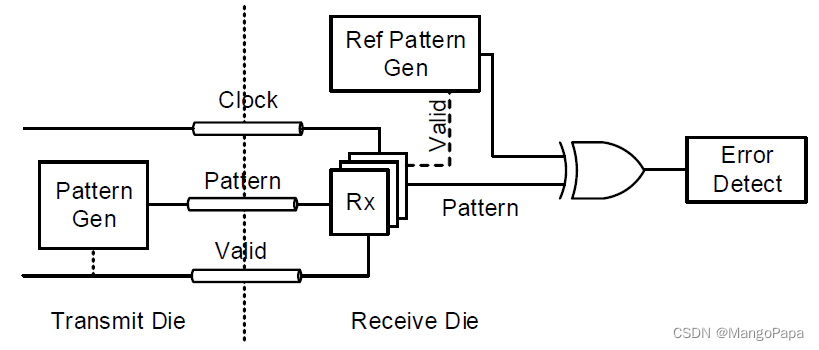

UCIe 接口 Data to Clock 训练及测试电路示意图如下(图 1):

▲图 1:UCIe Data to Clock Test Scheme

2.2 比较方案

接收端需实现以下两种 Test Pattern 的比较方案:

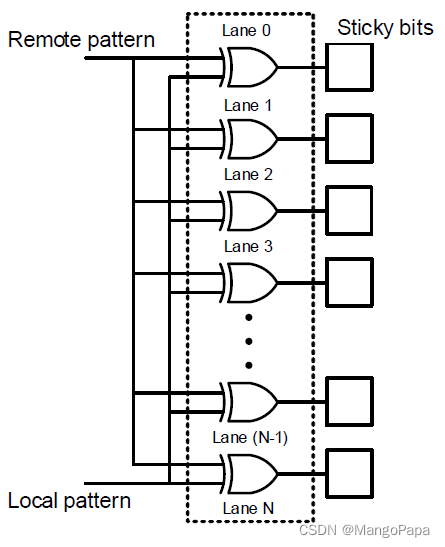

Per Lane Comparison ,逐 Lane 比较(图 2),每一条 Lane (标准封装:16 条 Lane;先进封装:64 条常规 Data Lane + 4 条备用 Lane)单独实现 Pattern 检测电路,并配有一个 Sticky Register Bit。当该 Lane 的 Pattern 比较出错后,其对应的 Sticky Bit 置一,且整个训练过程中都不会清除。通过这种方式,Sideband 通过查询 Sticky Bit 能够知晓到底是哪条 Lane 出了问题,从而完成接下来的 Repair 任务。

▲图 2:UCIe Data to Clock Test Per Lane Comparison

Aggregate comparison ,综合比较(图 3),跟 Per Lane Comparison 类似,但其检测结果并非 Sticky 的,而是实时变化的。所有 Lane 上的比较结果进行 或操作 ,从而对所有检测到的 Compare Error 进行汇总,每出现一个 UI 的错误,位宽 16 bit 的 Error Counter 计数加一。若同一个 UI 内多条 Lane 上出现了 Compare Error,只能统计到一次。该电路是用来统计 BER 的,可通过 Sideband 读取该 Error Counter 的值。若错误 Bit 数目超过设定阈值,则本次 Data to Clock Training 测试失败,即采用当前相位的 Clock 对 Data 进行采样无法满足需求,需要进一步调整。

▲图 3:UCIe Data to Clock Test Aggregated Comparison

2.3 LFSR

UCIe 测试 Pattern 及 Scramble 都是基于 LFSR,LFSR 采用的本原多项式与 PCIe 相同,即 G(X)=X23 + X21 + X16 + X8 + X5 + X2 + 1。每条 Lane 可以采用独立的 LFSR, LFSR Seed 取决于 Lane ID 的 低 3bit ,如表 1 所示。两组备用 Lane 采用的 LFSR 分别与 Lane 2/3 相同。

▼表 1: LFSR Seed

Lane LFSR Seed 0 23’h1DBFBC 1 23’h 0607BB 2, RD0, RD2 23’h1EC760 3, RD1, RD3 23’h18C0DB 4 23’h010F12 5 23’h19CFC9 6 23’h0277CE 7 23’h1BB807 除了每条 Lane 独立一个 LFSR,也可以所有 Lane 共享同一个 LFSR,不同的 Lane 对应 LFSR 不同的抽头点。跟 PCIe 一样,不再赘述。

3. 参考

- UCIe Spec r1.0, Chapter 4,5

- 时钟和数据恢复(CDR)电路原理——基于PLL

- SerDes interface参考设计_CDR设计

- CDR与相位插值器

- UCIe PHY 接口信号

- UCIe PHY LSM 介绍

— END —

🔥 精选往期 UCIe 协议系列文章,请查看【 Chiplet 专栏】🔥

⬆️ 返回顶部 ⬆️

-

相关阅读:

复习下图灵机概念

第十周周报

Redis企业级问题及解决方案

(尊享版)22年国内最牛的Java面试八股文合集,不接受反驳

UG NX二次开发(C++)-UIStyler-如何获取树中节点的子节点

详解数据仓库之拉链表(原理、设计以及在Hive中的实现)

上海亚商投顾:三大指数小幅下跌 光刻机概念股午后走强

Vue中实现3D得球自动旋转

Spring mvc中Controller如何设置接受参数的默认值呢?

重装系统以后怎么还原电脑原本的资料

- 原文地址:https://blog.csdn.net/weixin_40357487/article/details/127414439