-

【数字实验室】在时序逻辑中使用阻塞赋值会怎么样?

【数字实验室】在时序逻辑中使用阻塞赋值会怎么样?

阻塞赋值的使用

如之前介绍所述,建议使用阻塞赋值来描述组合逻辑设计。但是,如果在编码时序逻辑行为时使用阻塞赋值,会发生什么?这是需要解决的最重要的问题之一,对后续讨论很重要。

如果阻塞赋值用于编码时序逻辑的行为,则可以观察到综合结果不是正确的功能设计意图。

接下来介绍使用阻塞赋值对时序电路设计进行编码的几个设计方案。

阻塞赋值和多个“Always”进程

如例6.1所述,在多个“Always” 进程中使用阻塞赋值。程序块“Always”在时钟的正边缘触发,综合器推断时序逻辑。如前所述,所有阻塞赋值都在活动队列中进行计算和更新。读者请参阅之前分享的分层事件队列一文。

如例6.1所述,这两个“Always” 进程并行执行,并以两位串行输入串行输出移位寄存器的形式生成输出。首先,always进程生成一个输出“b_in”从第一个“Always” 进程生成的输出被另一个“Always” 进程用作输入。因此,综合器将其推断为两位串行输入串行输出移位寄存器。

示例6.1的综合逻辑如图6.1所示,并具有输入“a_in”,“clk”和输出“y_out”

例6.1在多个always块中阻塞赋值

例6.1在多个always块中阻塞赋值

图6.1多个always块中阻塞赋值的综合逻辑

图6.1多个always块中阻塞赋值的综合逻辑

同一“always”进程中的阻塞赋值

如果阻塞赋值用于描述时序逻辑,并且在同一“always”程序块中使用多个分配,则预期需求可能与综合逻辑匹配,也可能与综合逻辑不匹配。原因是,在阻塞分配中,所有后续语句(下一个立即数)都被阻塞,除非直到当前语句被执行。这将导致硬件截断,并可能推断出不需要的综合输出。

考虑在示例6.2中描述的设计场景,其意图是创建三位串行输入和串行输出移位寄存器,但是在综合示例6.2之后,它推断为单个触发器。

可综合逻辑如图6.2所示,其输入为“a”、“clk”和输出为“y”。所需的功能是串行输入、串行输出移位寄存器,但上述示例由于使用阻塞赋值而推断出单个触发器。因此,建议在为时序功能编码或描述RTL时使用非阻塞赋值。

例6.2在always”进程中的阻塞赋值

例6.2在always”进程中的阻塞赋值

图6.2同一always进程中阻塞赋值的综合逻辑

图6.2同一always进程中阻塞赋值的综合逻辑

阻塞赋值示例

考虑在示例6.3中描述的设计场景,其意图是创建三位串行输入和串行输出移位寄存器,并且由于块“begin” 和 “end”中使用的阻塞赋值语句,它顺序生成三位串行输入串行输出移位寄存器。

综合逻辑如图6.3所示,其输入为“a”、“clk”和输出“y”。所需的功能是串行输入串行输出移位寄存器,它推断串行输入串行输出移位寄存器。因此,需要记住的重要一点是,程序“always”块中的阻塞赋值语句的顺序是综合中的决定性因素。

例6.3同一always块中的阻塞赋值(排序)

例6.3同一always块中的阻塞赋值(排序)

图6.3阻塞赋值重新排序后的可综合逻辑

图6.3阻塞赋值重新排序后的可综合逻辑

非阻塞赋值

如之前介绍的“分层事件队列”一文所述,非阻塞赋值在活动事件队列中评估,并在NBA队列中更新。非阻塞赋值用于描述时序逻辑。这些指定在程序块“always”中使用,以获得所需的综合结果。所有非阻塞赋值在“always”块内并行执行。

如例6.4所述。非阻塞赋值用于多个“always”块。程序块“always”在时钟的正边沿触发,综合器推断时序逻辑。综合逻辑如图6.4所示。

例6.4不同always块中的非阻塞赋值

例6.4不同always块中的非阻塞赋值

图6.4不同always块中的非阻塞赋值的综合逻辑

图6.4不同always块中的非阻塞赋值的综合逻辑

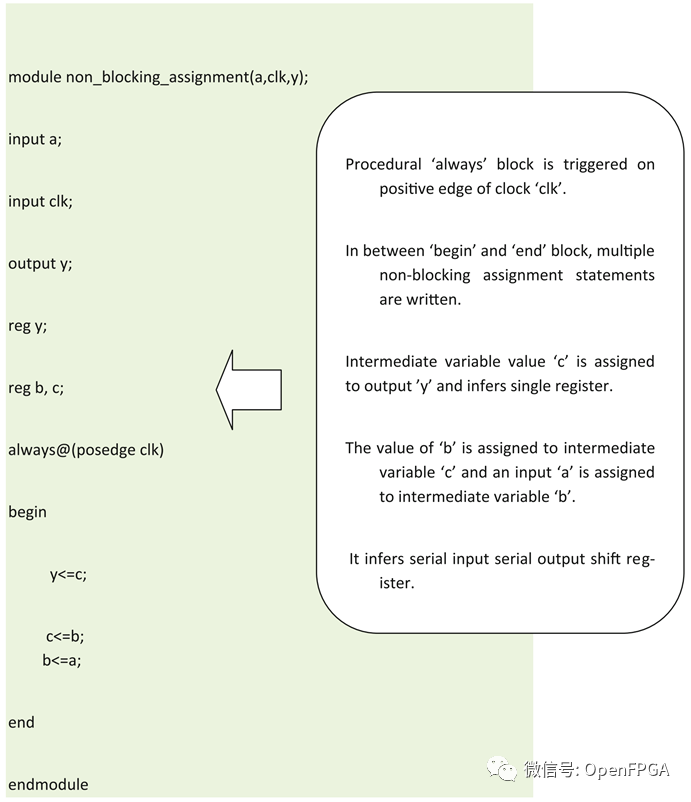

非阻塞赋值示例

如果使用非阻塞赋值来描述时序逻辑,并且在同一“always”程序块中使用多个赋值,则综合器始终推断出所需的预期逻辑。原因是,在非阻塞赋值中,“begin-end”块中写入的所有语句都是“并行”执行的,这就产生了时序逻辑。

考虑示例6.5中描述的设计场景,意图是创建三位串行输入和串行输出移位寄存器,使用非阻塞赋值。

综合逻辑如图6.5所示,其输入为“a”、“clk”和输出“y”。所需的功能是串行输入串行输出移位寄存器,它推断串行输入串行输出移位寄存器。

例6.5同一always块中的非阻塞赋值

例6.5同一always块中的非阻塞赋值

图6.5同一always块中非阻塞赋值的综合逻辑

图6.5同一always块中非阻塞赋值的综合逻辑

非阻塞赋值的排序

考虑在示例中描述的设计方案,其意图是创建三位串行输入和串行输出移位寄存器,并使用非阻塞赋值。

上一节中的实例,在本例6.6中重新排序。

综合逻辑如图6.5所示,其输入为“a”、“clk”和输出“y”。所需的功能是串行输入串行输出移位寄存器,它推断串行输入串行输出移位寄存器。所以,重要的一点是要记住,过程“always”块中非阻塞赋值语句的顺序不是推断逻辑的决定性因素。

例6.6在同一always块中具有顺序更改的非阻塞赋值

例6.6在同一always块中具有顺序更改的非阻塞赋值

总结

不总结了,例子很多建议自己测试。

-

相关阅读:

视频讲解|基于模型预测算法的含储能微网双层能量管理模型【mpc】

逐秒追加带序号输入当前时间:fgets fputs sprintf fprintf

动态sql和分页

【毕业设计】深度学习试卷批改系统 - opencv python 机器视觉

heap use after free

Vue2_lesson4_el与data的两种方式

有人知道这个动作模型是哪里的吗?叫什么?

[C++] 超详细分析 C++内存分布、管理(new - delete) ~ C 和 C++ 内存管理关系 ~ 内存泄漏 ~

java毕业设计乐儿乐社区生鲜团购系统源码+lw文档+mybatis+系统+mysql数据库+调试

kali download+安装teamviewer

- 原文地址:https://blog.csdn.net/Pieces_thinking/article/details/126737105