-

FPGA结构分析——ODDR,网口储备点2

前言:关于IDDR时序说明可见本篇FPGA结构分析——IDDR,网口储备点1“”,本篇就ODDR进行说明

1.什么是 ODDR? ODDR的作用是什么?使用场景?

2. ODDR结构是什么样?都有哪些端口?端口属性都是什么?

3.ODDR原语结构,参数属性说明?

4. ODDR时序是什么样 ?1.什么是 ODDR? ODDR的作用是什么?使用场景?

ODDR全称output double date rate,ODDR将FPGA fabric侧的同步数据传输到 IOB侧,在FPGA侧时钟的上升沿和下降沿都传输数据,通常使用在并转串数据设计中,如网口的GMII信号转换为RGMII信号。

2. ODDR结构是什么样?都有哪些端口?端口属性都是什么?

端口说明:

C:同步时钟输入端口

CE:时钟使能端口,高电平有效

D1、D2:并行数据输入端口

S/R:置位复位管脚

Q:串并转化后的数据输出端口,在时钟C端的上升沿输出D1数据,下降沿输出D2数据。如果两路输入信号一路固定为 1,另外一路固定为 0,那么输出的信号实际上是时钟信号,这也是时钟输出使用较多的方式之一。3.ODDR原语结构,参数属性说明?

原语结构:

ODDR #( .DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE" .INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1 .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" ) ODDR_inst ( .Q(Q), // 1-bit DDR output .C(C), // 1-bit clock input .CE(CE), // 1-bit clock enable input .D1(D1), // 1-bit data input (positive edge) .D2(D2), // 1-bit data input (negative edge) .R(R), // 1-bit reset .S(S) // 1-bit set );- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

参数说明:

DDR_CLK_EDGE:设置ODDR相对于时钟端口的边沿工作模式,共两种模式,在第4小节会具体说明;

INIT:Q端初始值;

SRTYPE:置/复位引脚同步/异步方式。4. ODDR时序是什么样 ?

ODDR有两种输出模式,在原语中由DDR_CLK_EDGE参数进行设置,分别为“OPPOSITE_EDGE”、“SAME_EDGE”。

OPPOSITE_EDGE模式的时序图如下图所示,CLK的上升沿和下降沿都用来采集数据,在FPGA fabric侧需要两个反相时钟同步D1、D2,使用不方便,故较少使用。

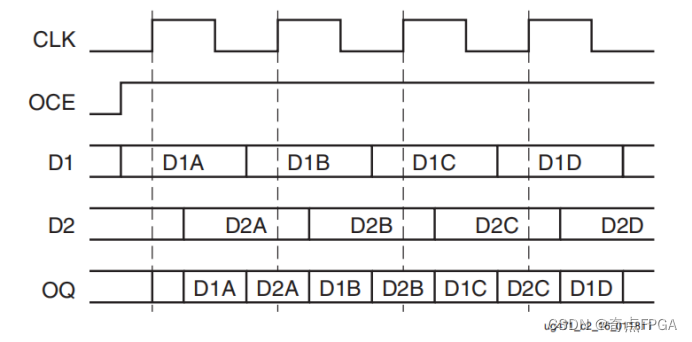

SAME_EDGE模式的时序图如下图所示,D1、D2都在CLK的相同的上升沿被采集,此种模式使用较多。

-

相关阅读:

mysql binlog自动删除与手动删除

MVC,MVP,MVVM的理解和区别

Opt算法

快速排序的非递归形式和一个小应用

MySQL数据库索引以及使用唯一索引实现幂等性

【目标检测】图像裁剪/标签可视化/图像拼接处理脚本

JSP居民信息采集系统yeclipse开发mysql数据库bs框架java编程jdbc详细设计

计算机网络常见的名词解释

MySql 数据库【事务】

Bond配置文件配置

- 原文地址:https://blog.csdn.net/weixin_42470069/article/details/126620817