-

FPGA - 7系列 FPGA内部结构之Memory Resources -03- 内置纠错功能

内置纠错概述

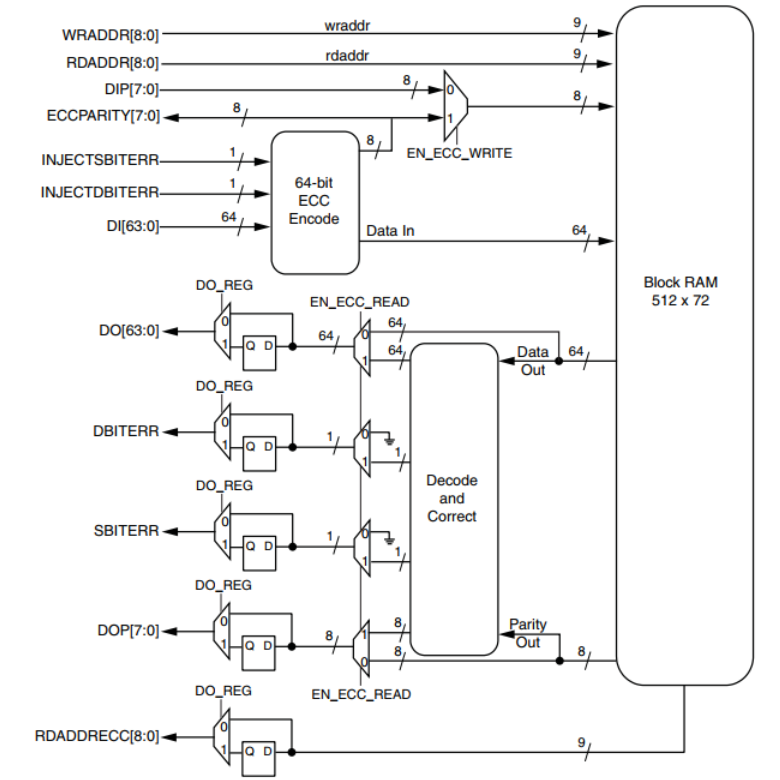

使用 72 位宽 RAM 中的额外 8 位,简单双端口模式下的 RAMB36E1 可配置为具有内置汉明码纠错功能的单个 512 x 64 RAM。 该操作是透明的。

在每次写操作期间会生成八个保护位 (ECCPARITY),并与 64 位数据一起存储到内存中。 这些 ECCPARITY 位在每次读取操作期间用于纠正任何一位错误,或检测(但不纠正)任何双位错误。ECCPARITY 位在 WRCLK 的每个上升沿被写入存储器并输出到 FPGA 逻辑。 ECCPARITY 输出位上没有可用的可选输出寄存器。

在每次读取操作期间,从存储器中读取 72 位数据(64 位数据和 8 位奇偶校验位)并馈送到 ECC 解码器。 ECC 解码器生成两个状态输出(SBITERR 和 DBITERR),用于指示三种可能的读取结果:无错误、已纠正单位错误、检测到双位错误。 在标准 ECC 模式下,读操作不会纠正内存阵列中的错误,它只会在 DO 上呈现纠正后的数据。 为了提高 FMAX,由 DO_REG 属性控制的可选寄存器可用于数据输出 (DO)、SBITERR 和 DBITERR。

ECC 配置选项可用于简单双端口模式下的 36Kb 块 RAM (RAMB36E1) 或 36Kb FIFO (FIFO36E1)。 RAMB36E1 具有注入错误的能力。 RAMB36E1 能够回读存储当前读出数据的地址。 此功能更好地支持修复位错误或使该地址的内容无效以供将来访问。 FIFO36E1 支持标准 ECC 模式并具有错误注入能力。 FIFO36E1 不支持 ECC 仅编码模式并且不输出正在读取的地址位置。

7 系列 FPGA 块 RAM ECC 还支持 READ_FIRST 和 WRITE_FIRST 模式,其方式与 SDP 模式相同。

ECC 模式

在标准 ECC 模式(EN_ECC_READ = TRUE 和 EN_ECC_WRITE = TRUE)中,编码器和解码器均启用。 在写入期间,64 位数据和 8 位 ECC 生成的奇偶校验存储在数组中。 外部奇偶校验位被忽略。 在读取过程中,72 位解码数据和奇偶校验被读出。

编码器和解码器可以在简单双端口模式下单独访问以供外部使用 RAMB36E1。 单独使用编码器,需要通过DI口发送数据,ECCPARITY输出口可以采样。 要单独使用解码器,禁用编码器,将数据写入 Block RAM,并从 Block RAM 中读出更正的数据和状态位。

要在 ECC 仅解码模式下使用解码器,请设置 EN_ECC_WRITE = FALSE 和 EN_ECC_READ = TRUE。

编码器有两种使用方式:

- 要在标准 ECC 模式下使用编码器,请设置 (EN_ECC_WRITE = TRUE 和 EN_ECC_READ = TRUE)。 在这种模式下,不支持 ECC 奇偶校验。

- 要使用仅编码器模式,请设置(EN_ECC_WRITE = TRUE 和 EN_ECC_READ = FALSE)。 在这种模式下,支持 ECC 奇偶校验。

使用 ECC 模式时 Block RAM 的功能描述如下:

- Block RAM 端口仍然具有独立的地址、时钟和使能输入,但一个端口是专用写端口,另一个是专用读端口( 简单的双端口)。

- DO 表示校正后的读取数据。

- DO 保持有效,直到下一次有效的读取操作。

- 允许同时对不同的读/写地址进行解码和编码; 但是,不允许同时对同一读/写地址进行解码和编码。

- 在ECC 配置中,块RAM 可以处于READ_FIRST 或WRITE_FIRST 模式。

Block RAM ECC 架构的顶层视图

Block RAM 和 FIFO ECC 原语

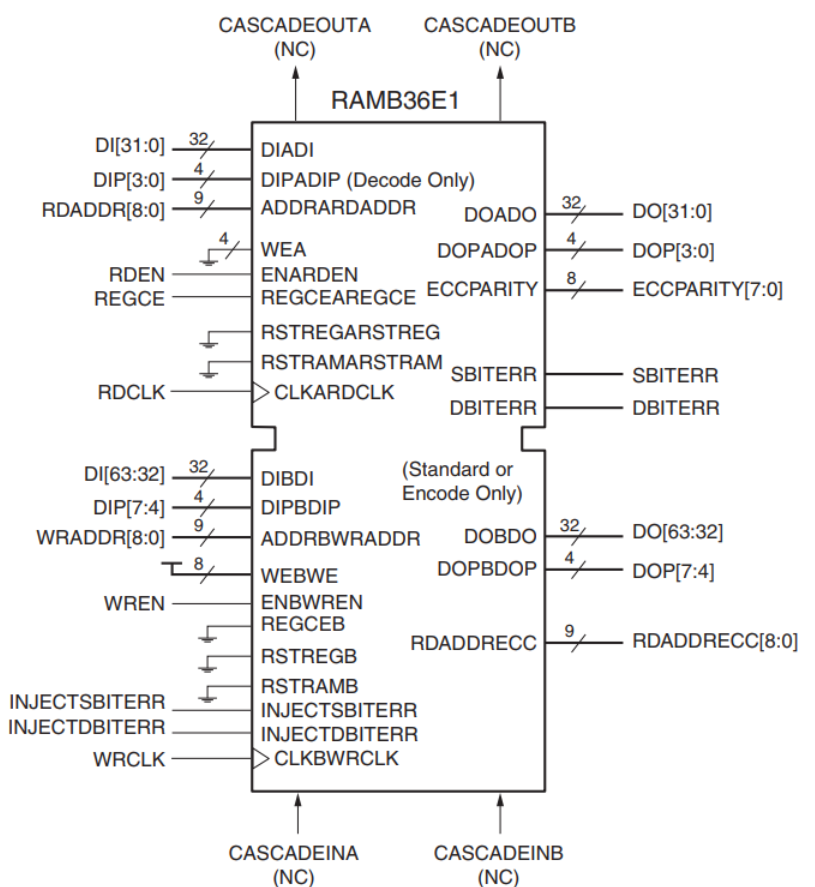

下图显示了 Block RAM (RAMB36E1) ECC 原语。 只有简单双端口 (SDP) 模式下的 RAMB36E1 支持 ECC。

下图显示了 FIFO36E1 ECC 原语。 FIFO36_72 模式只支持标准 ECC 模式,不支持 RDADDRECC 输出。

Block RAM 和 FIFO ECC 端口说明

下表列出并描述了 Block RAM ECC I/O 端口名称。

Port Name Signal Description DIADI[31:0] 在 ECC 模式下由 ADDRBWRADDR 寻址的端口 A 数据输入。 DIPADIP[3:0] 在 ECC 模式下由 ADDRBWRADDR 寻址的端口 A 数据奇偶校验输入。 DIBDI[31:0] 由 ADDRBWRADDR 寻址的端口 B 数据输入。 DIPBDIP[3:0] 由 ADDRBWRADDR 寻址的端口 B 数据奇偶校验输入。 ADDRARDADDR [15:0] 端口 A 地址输入总线。 在 RAM_MODE = SDP 中,这是 RDADDR 总线。 在 ECC 模式下,仅使用位 [14:6]。 ADDRBWRADDR[15:0] 端口 B 地址输入总线。 在 RAM_MODE = SDP 中,这是 WRADDR 总线。 在 ECC 模式下,仅使用位 [14:6]。 WEA[3:0] 端口 A 字节宽的写使能。 在 RAM_MODE = SDP 中不使用。 在 ECC 模式下,将 WEA 连接到 GND。 WEBWE[7:0] 端口 B 字节宽写使能 (WEBWE [3:0])。 在 RAM_MODE = SDP 中,这是字节范围的写使能。 在 ECC 模式下,将此端口连接到逻辑高电平。 ENARDEN 端口 A 启用。 在 RAM_MODE = SDP 或 ECC 中,这是 RDEN。 ENBWREN 端口 B 启用。 在 RAM_MODE = SDP 或 ECC 中,这是 WREN。 RSTREGARSTREG 同步输出寄存器设置/复位由 SRVAL_A (DO_REG = 1) 初始化。 RSTREG_PRIORITY_A 确定 REGCE 的优先级。 在 RAM_MODE = SDP 中,这是 RSTREG。 在 ECC 模式下,将RSTREGARSTREG 连接到GND。 RSTREGB 同步输出寄存器设置/复位由 SRVAL_B (DO_REG = 1) 初始化。 RSTREG_PRIORITY_B 确定 REGCE 的优先级。 在 SDP (ECC) 模式下,将 RSREGB 连接到 GND。 RSTRAMARSTRAM 同步输出锁存器设置/复位由 SRVAL_A (DO_REG = 0) 初始化。 在 RAM_MODE = SDP 中,这是 RSTRAM。 在 ECC 模式下,连接到 GND。 RSTRAMB 同步输出锁存器设置/复位由 SRVAL_B (DO_REG = 0) 初始化。 在 SDP (ECC) 模式下,将 REGCEB 连接到 GND。 CLKARDCLK 端口 A 时钟输入。 在 RAM_MODE = SDP 中,这是 RDCLK。 CLKBWRCLK 端口 B 时钟输入。 在 RAM_MODE = SDP 中,这是 WRCLK。 REGCEAREGCE 端口 A 输出寄存器时钟使能 (DO_REG = 1)。 在 RAM_MODE SDP 和 ECC 中,这是 REGCE。 REGCEB 端口 B 输出寄存器时钟使能 (DO_REG = 1)。 在 ECC 模式下,将 REGCEB 连接到 GND。 CASCADEINA 端口 A 级联输入。 仅用于 RAM_MODE = TDP。 CASCADEINB 端口 B 级联输入。 仅用于 RAM_MODE = TDP。 CASCADEOUTA 端口 A 级联输出。 仅用于 RAM_MODE = TDP。 CASCADEOUTB 端口 B 级联输出。 仅用于 RAM_MODE = TDP。 DOADO[31:0] 由 ADDRARDADDR 寻址的端口 A 数据输出总线。 DOPADOP[3:0] 由 ADDRARDADDR 寻址的端口 A 奇偶校验输出总线。 DOBDO[31:0] 端口 B 由 ADDRARDADDR 寻址的数据输出总线。 DOPBDOP[3:0] 端口 B 奇偶校验输出总线由 ADDRARDADDR 寻址。 ECC Port Names (Not used if RAM_MODE = TDP) INJECTSBERR 如果使用 ECC,则注入单位错误。 在写入期间置位时,在特定的 Block RAM 位位置创建单位错误。 回读该位置时,Block RAM ECC 逻辑会纠正此错误。 错误在位 DI[30] 中产生。 INJECTDBERR 如果使用 ECC,则注入双位错误。 在写入期间置位时,在两个特定的 Block RAM 位位置创建双位错误。 回读该位置时,Block RAM ECC 逻辑会标记一个双位错误。 当 INJECTSBERR 和 INJECTDBERR 信号同时置位时,就会注入双位错误。 错误在位 DI[30] 和 DI[62] 中产生。 ECCPARITY[7:0] ECC 编码器输出总线,用于仅编码模式下使用的 ECC。 SBITERR ECC 单位错误输出状态。 DBITERR ECC 双位错误输出状态。 RDADDRECC[8:0] ECC 读取地址。 指向当前读出的数据的地址指针。 数据和相应的地址在同一个周期内可用。 FIFO ECC 端口名称和说明

Port Name Direction Signal Description DI[63:0] Input 数据输入总线 DIP[7:0] Input 数据输入奇偶校验总线。 使用标准模式时不使用。 WREN Input 写使能。 当 WREN = 1 时,数据写入内存。 当 WREN = 0 时,禁止写入。 RDEN Input 读使能。 当 RDEN = 1 时,从内存中读取数据。 当 RDEN = 0 时,读取被禁用。 RSTREG Input 使用 Block RAM ECC 原语时不支持。 始终连接到 GND。 RSTRAM Input 使用 Block RAM ECC 原语时不支持。 始终连接到 GND。 RST Input FIFO 计数器和标志的异步复位。 必须在三个时钟周期内断言复位。 复位不会影响 DO 或 ECC 信号。 WRCLK Input 写操作的时钟。 RDCLK Input 读操作的时钟。 INJECTSBITERR Input 在写入期间置位时,在特定的 Block RAM 位上产生单位错误。 回读该位置时,Block RAM ECC 逻辑会纠正此错误。 错误在位 DI[30] 中产生。 INJECTDBITERR Input 在写入期间置位时,在两个特定的 Block RAM 位上产生双位错误。 回读该位置时,Block RAM ECC 逻辑会标记一个双位错误。 当两个 INJECTBITERR 信号同时置位时,会注入一个双位错误。 错误在位 DI[30] 和 DI[62] 中产生。 DO[63:0] Output 数据输出总线 DOP[7:0] Output 数据输出奇偶校验总线。 SBITERR Output 单位错误状态。 DBITERR Output 双位错误状态。 ECCPARITY[7:0] Output 不支持。 FULL Output FIFO 满标志。 ALMOSTFULL Output FIFO 几乎满标志。 EMPTY Output FIFO 空标志。 ALMOSTEMPTY Output FIFO 几乎为空标志。 RDCOUNT Output FIFO 数据读取指针。 WRCOUNT Output FIFO 数据写指针。 WRERR Output 当 FIFO 已满时,任何额外的写操作都会生成一个错误标志。 RDERR Output 当 FIFO 为空时,任何额外的读取操作都会生成错误标志。 Block RAM 和 FIFO ECC 属性

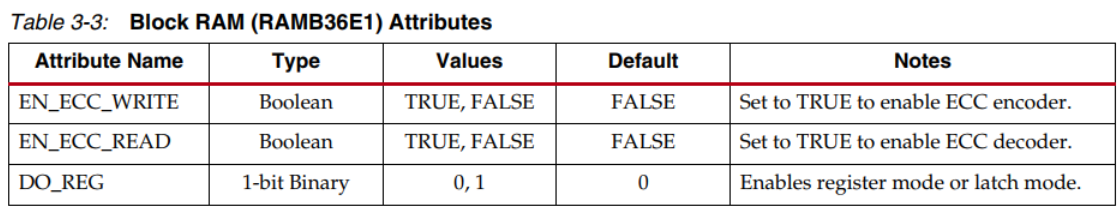

除了解码和纠正逻辑中的内置寄存器外,RAMB36E1 原语允许使用由 DO_REG 属性控制的可选流水线寄存器,以产生更高的性能和一个额外的延迟。 下表列出了 Block RAM 和 FIFO ECC 属性。

ECC 操作模式

ECC 操作分为三种类型:标准、仅编码和仅解码。 标准 ECC 模式同时使用编码器和解码器。

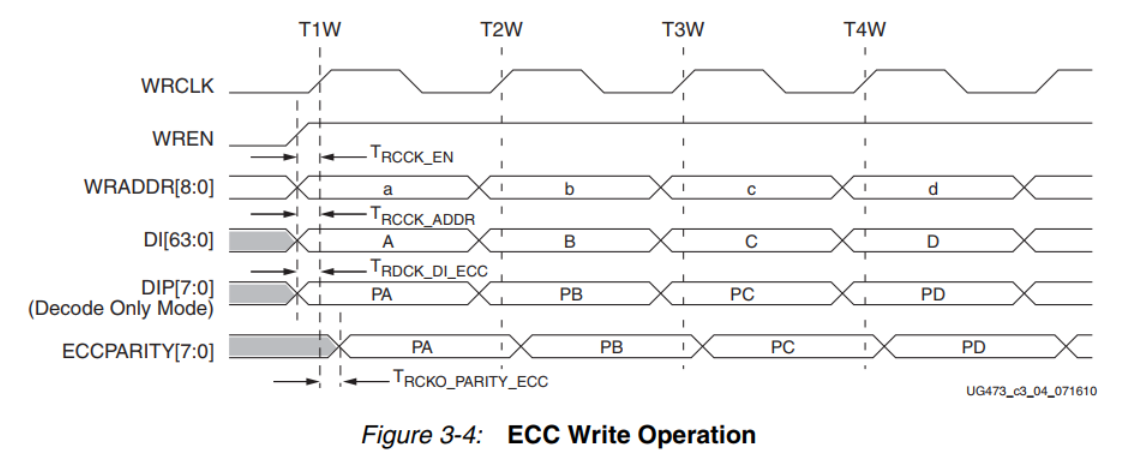

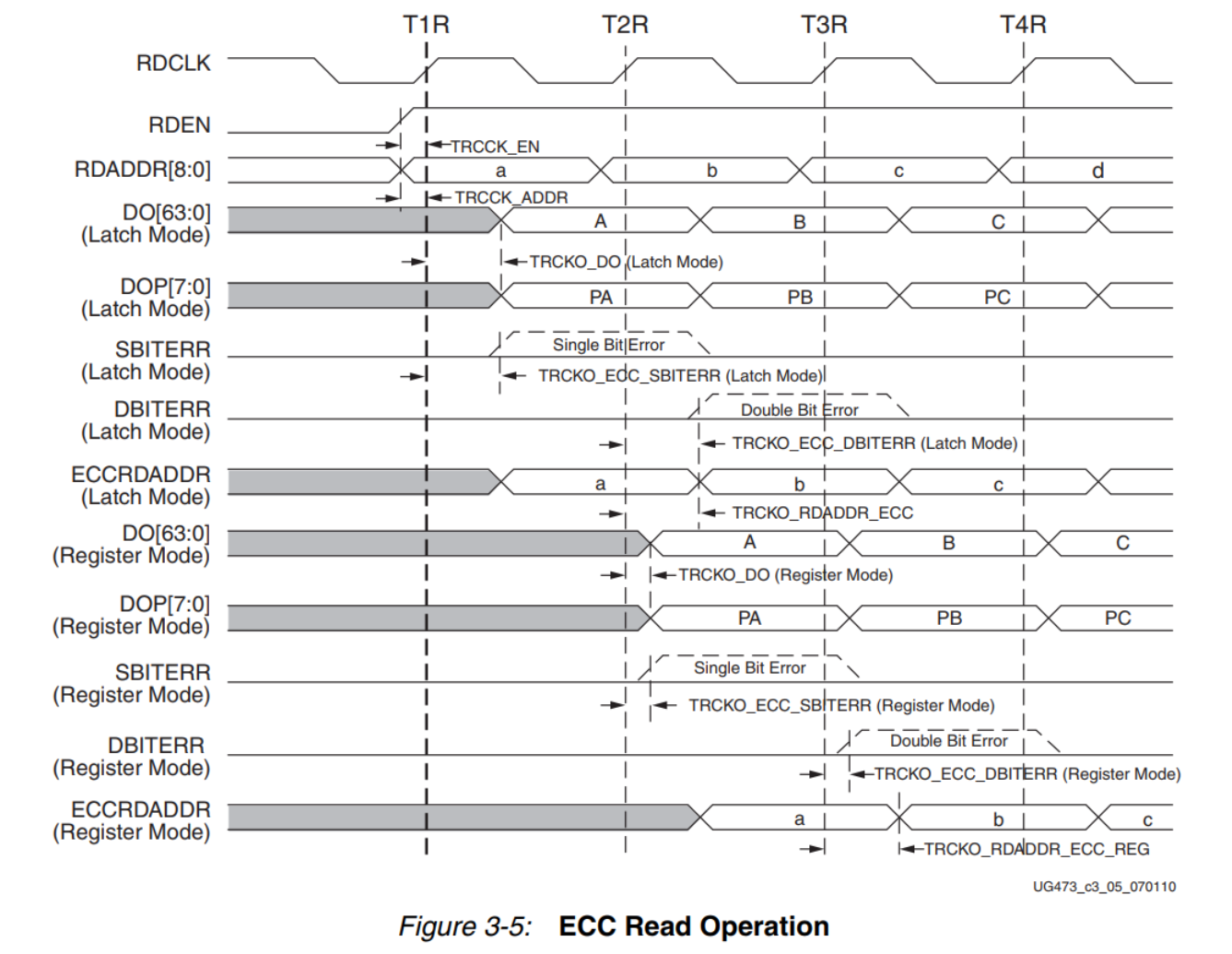

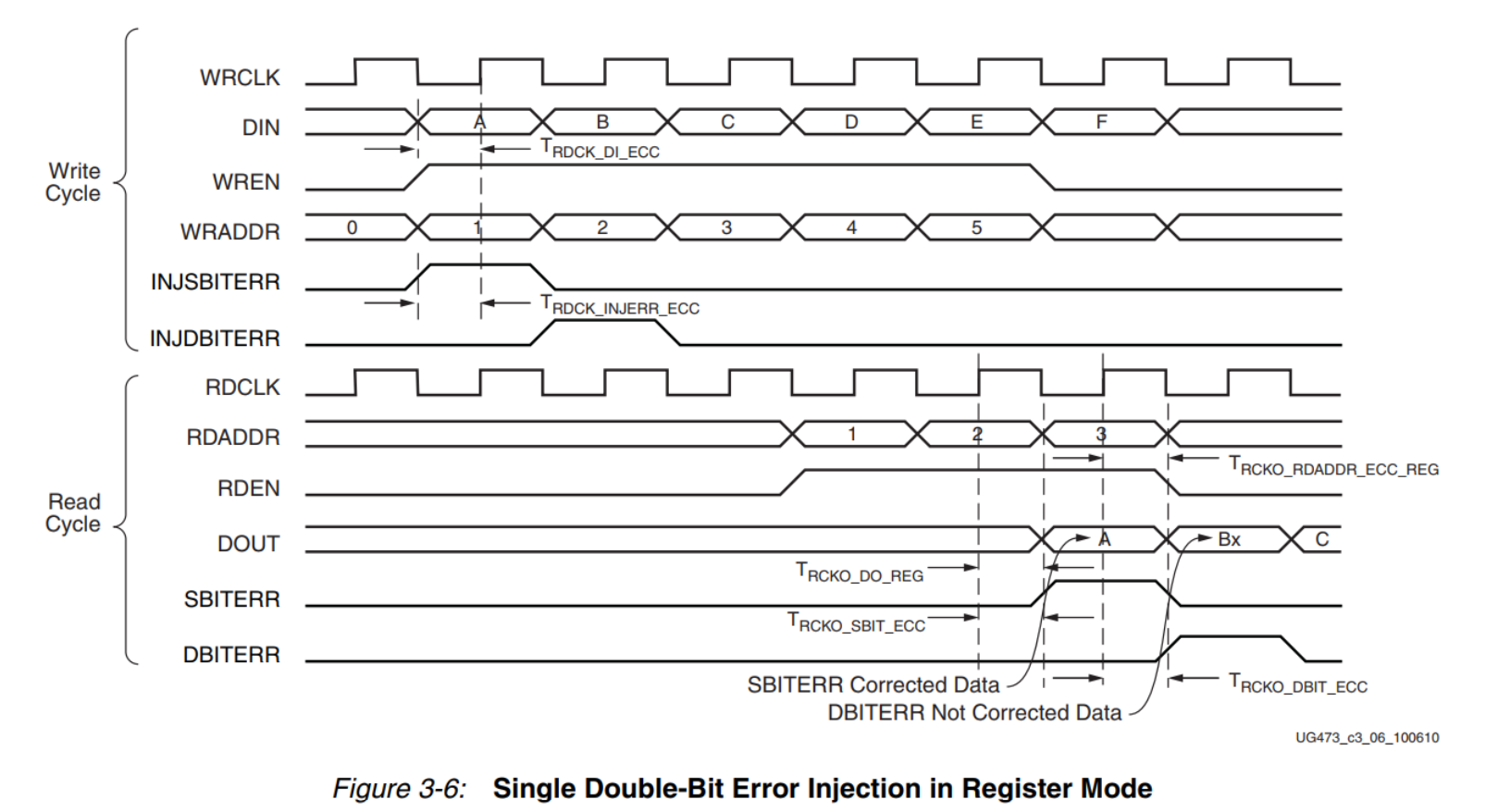

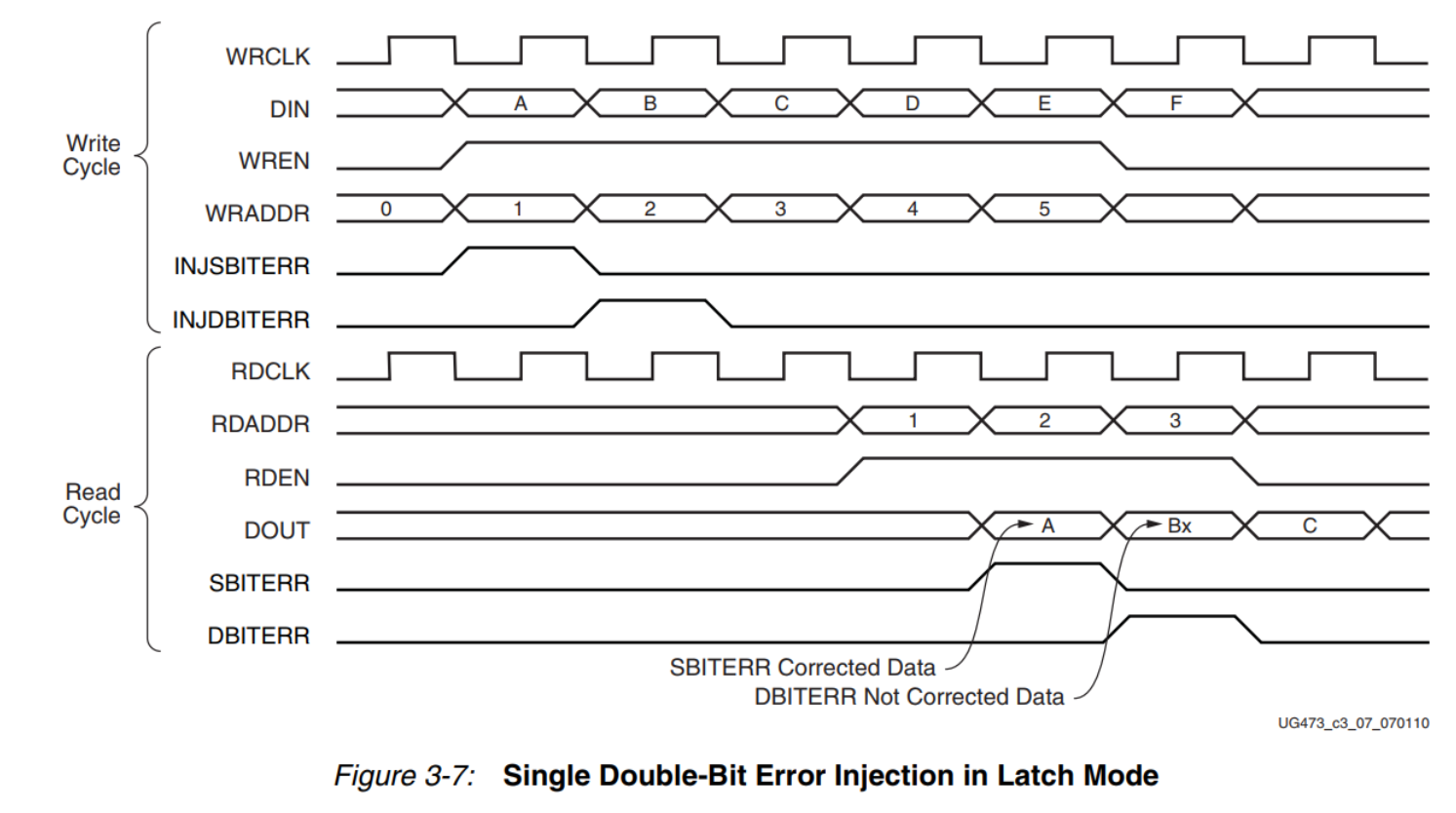

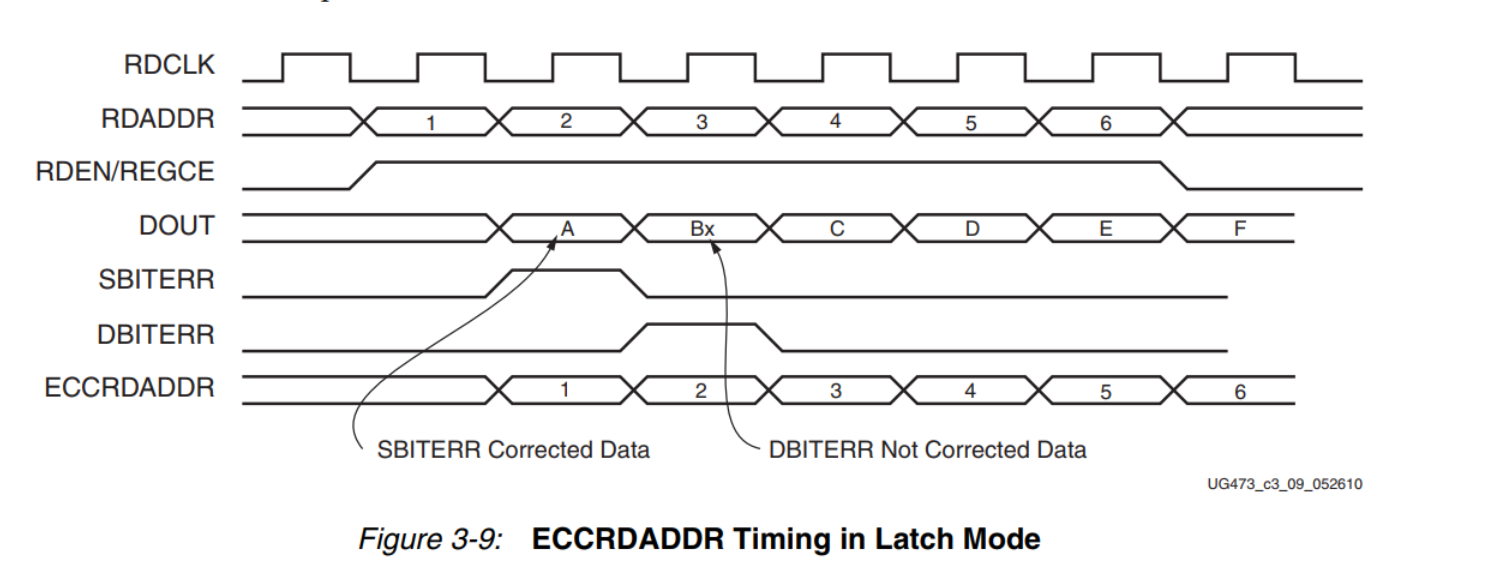

图 3-4 到图 3-9 显示了 Block RAM 和 FIFO 中 ECC 操作的各种模式。 由用户提供 Block RAM WRADDR 和 RDADDR 地址输入。FIFO WRADDR 和 RDADDR 地址由写计数器和读计数器在内部生成。

数据(DOUT)和对应地址(ECCRDADDR)在同一阶段提供使用。

数据(DOUT)和对应地址(ECCRDADDR)在同一阶段提供使用。

数据 (DOUT) 和相应的地址 (ECCRDADDR) 在同一阶段提供使用。

标准ECC

由属性设置ECC

E N _ E C C _ R E A D = T R U E E N _ E C C _ W R I T E = T R U E EN\_ECC\_READ = TRUE\\ EN\_ECC\_WRITE = TRUE EN_ECC_READ=TRUEEN_ECC_WRITE=TRUE

标准 ECC 写入

如图 3-4 所示。

在时间 T1W,DI[63:0] = A 被写入内存位置 a。 内部生成对应的 8 位 ECC 奇偶校验 PA(十六进制),附加到 64 个数据位后,写入内存。 写入后,奇偶校验值 PA 立即出现在输出 ECCPARITY[7:0]。 因为 ECC 奇偶校验是在内部生成的,所以不使用 DIP[7:0] 引脚。 在标准 ECC 模式下,不支持 ECC 奇偶校验。

类似地,在时间 T2W 和 T3W,DI[63:0] = B 和 C,连同它们相应的奇偶校验位 PB(十六进制)和 PC(十六进制)被写入存储单元 b 和 c。 PB 和 PC 在 T2W 和 T3W 之后不久出现在输出 ECCPARITY[7:0]。

标准 ECC 读取

如图 3-5 所示。

在时间 T1R,内部读取地址位置 a 的 72 位存储器内容,包括 64 位数据 A 和 8 位奇偶校验 PA(十六进制)。 如果没有错误,则在 DO[63:0] 和 DOP[7:0] 处输出原始数据和奇偶校验。 如果数据或奇偶校验中存在单位错误,则纠正错误,并且 SBITERR 为高。 如果数据和奇偶校验存在双位错误,则错误不会被纠正。 输出原始数据和奇偶校验,DBITERR 为高。如果属性 DO_REG 设置为 0,则在 T1R 之后不久,DO[63:0] = A 和 DOP[7:0] = PA。

类似地,在时间 T2R 和 T3R,地址位置 b 和 c 处的存储器内容在 DO[63:0] 和 DOP[7:0] 处被读取和解码。 如果在数据集 A 上检测到单位或双位错误,SBITERR/DBITERR 输出也可以在 T1R 之后切换。图 3-7 显示了在时钟沿 T1R 和 在时钟沿 T2R 之后,在锁存模式下在数据 B 上检测到双位错误 (DBITERR)。

如果属性 DO_REG 设置为 1,则在 T2R 之后不久,DO[63:0] = A 和 DOP[7:0] = PA。

类似地,在时间 T3R 和 T4R,地址位置 b 和 c 处的存储器内容在 DO[63:0] 和 DOP[7:0] 处被读取和解码。 如果在数据集 A 上检测到单比特或双比特错误,SBITERR/DBITERR 输出也可以在 T2R 之后切换。图 3-6 显示在时钟沿 T2R 和 在时钟沿 T3R 之后,在寄存器模式中检测到数据 B 上的双位错误 (DBITERR)。

仅 ECC 编码

由属性设置

E N _ E C C _ R E A D = F A L S E E N _ E C C _ W R I T E = T R U E EN\_ECC\_READ = FALSE\\ EN\_ECC\_WRITE = TRUE EN_ECC_READ=FALSEEN_ECC_WRITE=TRUE

ECC 仅编码写入

在时间 T1W,DI[63:0] = A 被写入内存位置 a。 内部生成对应的 8 位 ECC 奇偶校验 PA(十六进制),附加到 64 个数据位后,写入内存。 写入后,奇偶校验值 PA 立即出现在输出 ECCPARITY[7:0]。 因为 ECC 奇偶校验是在内部生成的,所以不使用 DIP[7:0] 引脚。

类似地,在时间 T2W 和 T3W,DI[63:0] = B 和 C,连同它们相应的奇偶校验位 PB(十六进制)和 PC(十六进制)被写入存储单元 b 和 c。 PB 和 PC 在 T2W 和 T3W 之后不久出现在输出 ECCPARITY[7:0]。

ECC 仅编码读取

ECC 仅编码读取与普通块 RAM 读取相同。 64 位数据出现在 DO[63:0],8 位奇偶校验出现在 DOP[7:0]。 不会发生单位错误纠正,并且错误标志 SBITERR 和 DBITERR 从未被断言。

仅 ECC 解码

由属性设置

E N _ E C C _ R E A D = T R U E E N _ E C C _ W R I T E = F A L S E EN\_ECC\_READ = TRUE\\EN\_ECC\_WRITE = FALSE EN_ECC_READ=TRUEEN_ECC_WRITE=FALSE

在 ECC 仅解码中,仅启用 ECC 解码器。 ECC 编码器被禁用。仅解码模式用于注入单位或双位错误以测试 ECC 解码器的功能。 ECC 奇偶校验位必须使用 DIP[7:0] 引脚从外部提供。

仅使用 ECC 解码来注入单位错误

- 在时间 T1W、T2W、T3W、DI[63:0] = A、B、C 出现单位错误且 DIP[7:0] = PA(十六进制)、PB (hex)、PC (hex),将 A、B 和 C 的相应 ECC 奇偶校验位写入内存位置 a、b 和 c。

- 在时间T1R、T2R、T3R,地址a、b和c的内容被读出并根据需要进行校正。

- 锁存模式:DO[63:0] = A, B, C, DOP[7:0] = PA, PB, PC 在 T1R、T2R、T3R 之后不久。

- 寄存器模式:DO[63:0] = A, B, C, DOP[7:0] = PA, PB, PC 在 T2R、T3R、T4R 之后不久。

- SBITERR 与相应的 DO/DOP 数据对齐。

ECC 解码器还纠正奇偶校验位中的单位错误

- 在时间 T1W、T2W、T3W、DI[63:0] = A、B、C 出现双位错误且 DIP[7:0] = PA(十六进制)、PB(十六进制)、PB(十六进制)时, A、B 和 C 的相应 ECC 奇偶校验位被写入内存位置 a、b 和 c。

- 在时间T1R、T2R、T3R,地址a、b、c 的原始内容被读出并检测到双位错误。

- 锁存模式:DO[63:0] = A、B、C 有双位错误,DOP[7:0] = PA、PB、PC 在 T1R、T2R、T3R 之后不久。

- 寄存器模式:DO[63:0] = A, B, C 有双位错误,DOP[7:0] = PA, PB, PC 在 T2R, T3R, T4R 之后不久。

- DBITERR 与相应的 DO/DOP 数据对齐。

ECC解码器还检测奇偶校验位何时发生双位错误,以及数据位中何时发生单位错误以及相应奇偶校验位中何时发生单位错误。

ECC 时序特性

图 3-4 至图 3-7 还显示了各种 ECC 时序参数。因为写时钟和读时钟相互独立,所以图 3-4 中的所有写时序都以 WRCLK 为参考。 图 3-5 中的所有读取时序均以 RDCLK 为参考。

标准 ECC 写时序

参见图 3-4。

- 在时间TRCCK_EN,在时间T1W 之前,写使能在Block RAM 的WREN 输入处变为有效。

- 在时间T1W 之前的TRCCK_ADDR 时间,写入地址a 在块RAM 的WRADDR[8:0] 输入处变为有效。 FIFO 不需要 WRADDR 输入。

- 在时间TRDCK_DI_ECC(标准ECC),在时间T1W 之前,写入数据A(十六进制)在块RAM 的DI[63:0] 输入处变为有效。

- 在时间TRCKO_ECC_PARITY(标准ECC),在时间T1W 之后,ECC 奇偶校验数据PA(十六进制)在块RAM 的ECCPARITY[7:0] 输出管脚处变为有效。

标准 ECC 读时序

请参见图 3-5。

- 在时间TRCCK_EN,在时间T1R 之前,读使能在块RAM 的RDEN 输入处变为有效。

- 在时间TRCCK_ADDR,在时间T1R 之前,写入地址a 在块RAM 的RDADDR[8:0] 输入处变为有效。 FIFO 不需要 RDADDR 输入。

DO_REG = 0

- 在时间TRCKO_DO(锁存模式),时间T1R 之后,数据A(十六进制)在Block RAM 的DO[63:0] 输出引脚上变为有效。

- 在时间 TRCKO_DOP(锁存模式),时间 T1R 之后,数据 PA(十六进制)在 Block RAM 的 DOP[7:0] 输出引脚上变为有效。

- 在时间 TRCKO_ECC_SBITERR(锁存模式),在时间 T1R 之后,如果在数据集 A 上检测到并纠正了单比特错误,则 SBITERR 被置位。

- 在时间 TRCKO_ECC_DBITERR(锁存模式),时间 T2R 之后,如果在数据集 B 上检测到双位错误,则断言 DBITERR。

DO_REG = 1

- 在时间TRCKO_DO(寄存器模式),时间T2R 之后,数据A(十六进制)在Block RAM 的DO[63:0] 输出引脚上变为有效。

- 在时间TRCKO_DOP(寄存器模式),时间T2R 之后,数据PA(十六进制)在块RAM 的DOP[7:0] 输出引脚上变为有效。

- 在时间 TRCKO_ECCR_SBITERR(寄存器模式),时间 T2R 之后,如果在数据集 A 上检测到并纠正了单比特错误,则断言 SBITERR。

- 在时间 TRCKO_ECCR_DBITERR(寄存器模式),时间 T3R 之后,如果在数据集 B 上检测到双位错误,则断言 DBITERR。

仅编码 ECC 写入时序

请参见图 3-4。

- WREN 和WRADDR 的建立/保持时间与标准ECC 相同。

- 在时间TRDCK_DI_ECC(仅编码ECC),在时间T1W 之前,写入数据A(十六进制)在块RAM 的DI[63:0] 输入处变为有效。

- 在时间TRCKO_ECC_PARITY(仅编码ECC),在时间T1W 之后,ECC 奇偶校验数据PA(十六进制)在Block RAM 的ECCPARITY[7:0] 输出引脚上变为有效。

仅编码 ECC 读取时序

- 仅编码 ECC 读取时序与正常 Block RAM 读取时序相同。

仅解码 ECC 写入时序

- 仅解码 ECC 写入时序与正常 Block RAM 写入时序相同。

仅解码 ECC 读取时序

- 仅解码 ECC 读取时序与标准 ECC 读取时序相同。

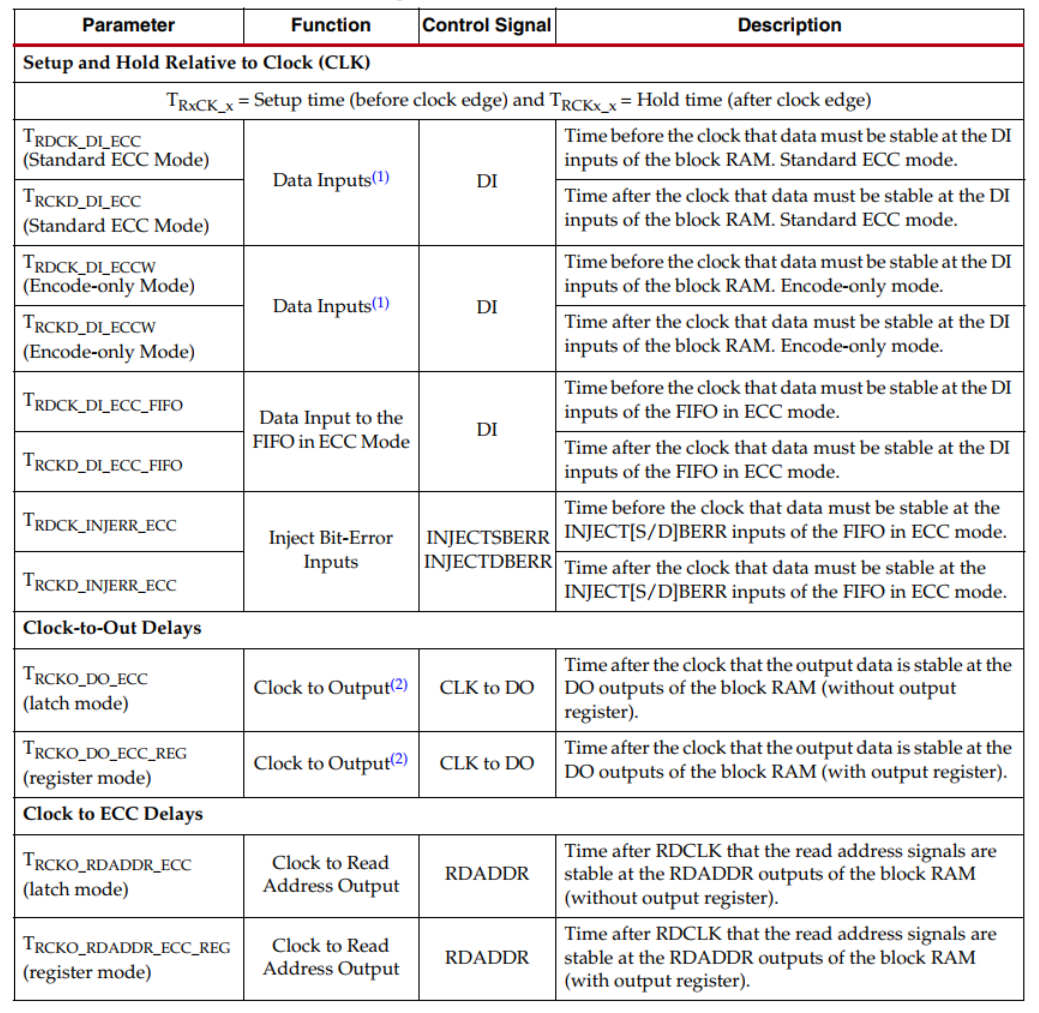

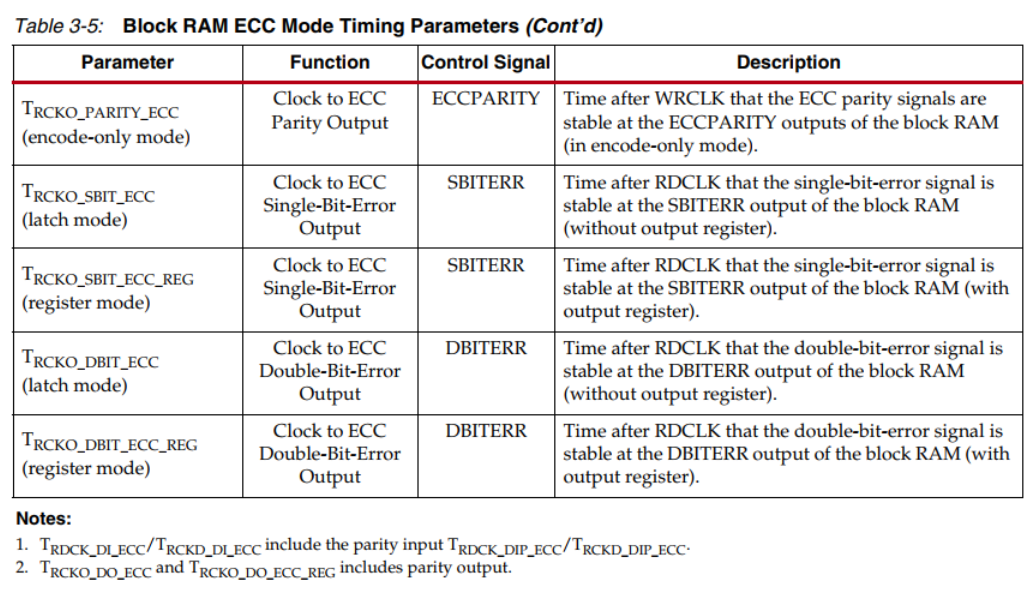

Block RAM ECC 模式时序参数

下表显示了 7 系列 FPGA 的 Block RAM ECC 模式时序参数。

为 64 位字创建 8 个奇偶校验位

使用块 RAM 外部的逻辑(大量 XOR 电路),可以为 64 位字创建 8 个奇偶校验位。 但是,使用仅 ECC 编码器模式,可以通过将任何 64 位字写入单独的 Block RAM 来自动创建 8 个奇偶校验位,而无需额外的逻辑。 编码后的 8 位 ECC 奇偶校验数据立即可用,或者可以读出完整的 72 位字。

-

相关阅读:

vite和webpack

【C++ Primer Plus学习记录】数组的替代品vector、array

基于抽象语法树的神经网络模型(ASTNN)简介

Swagger配置

Qt读写ini

阿里云国际站:密钥管理服务

【JavaEE】Java多线程编程案例 -- 多线程篇(3)

【每日一题】线段重叠

智慧城市中的数字孪生:数字孪生技术助力智慧城市提高公共服务水平

猿创征文|Hystrix的概念与简单使用

- 原文地址:https://blog.csdn.net/weixin_41445387/article/details/126225259