-

FPGA_Vivado软件初次使用流程_超详细

需要注意的是:我是用的版本是2018.3,不同版本的软件可能会存在差异

开发流程简介:打开软件—新建工程—设计输入—分析与综合—约束输入—设计实现—生成和下载比特流

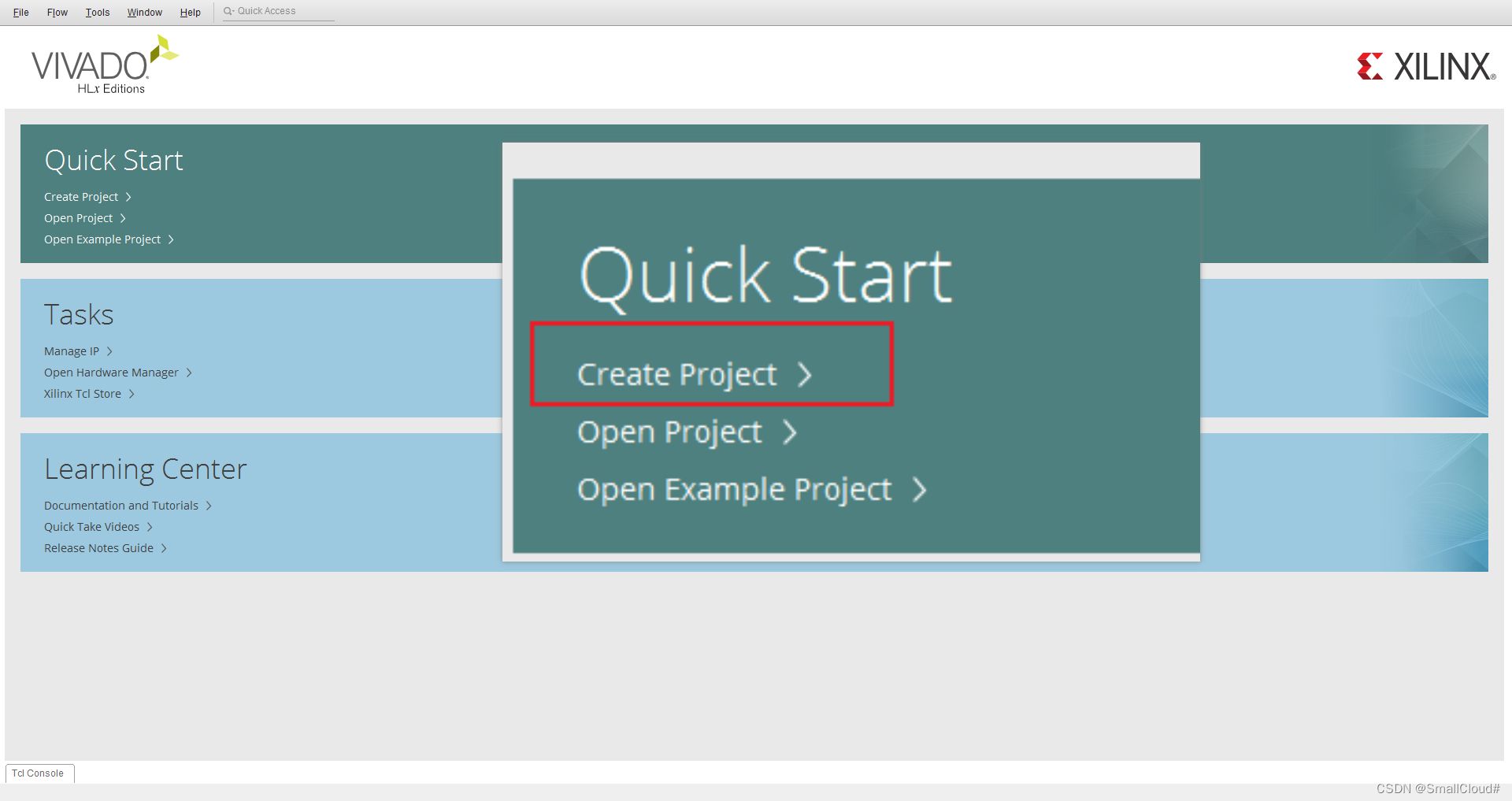

1、打开软件,点击Quick Start下的Create Project

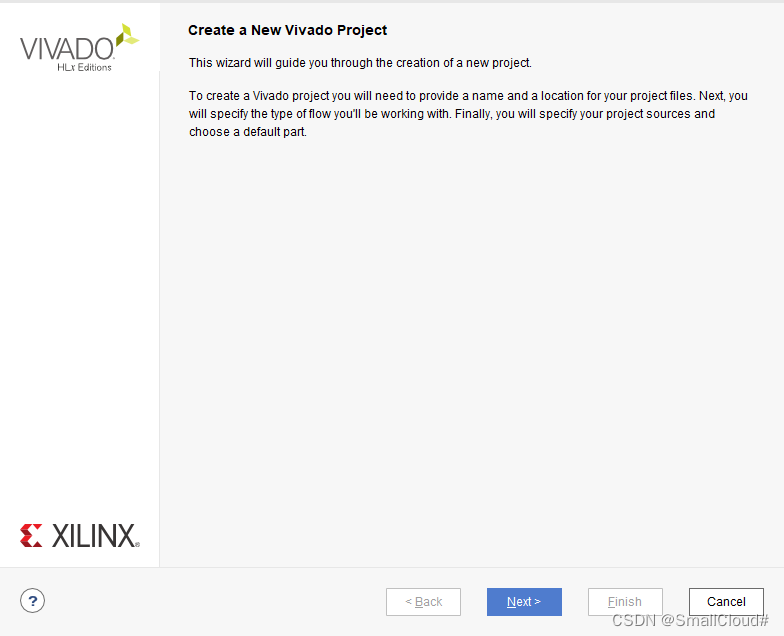

2、弹窗点击NEXT

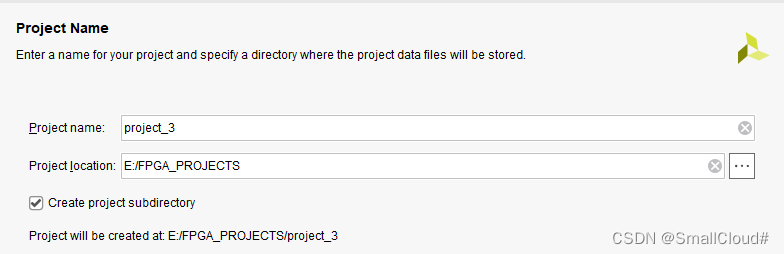

3、填写工程路径和工程名字后单击NEXT(注意路径不要带有中文)

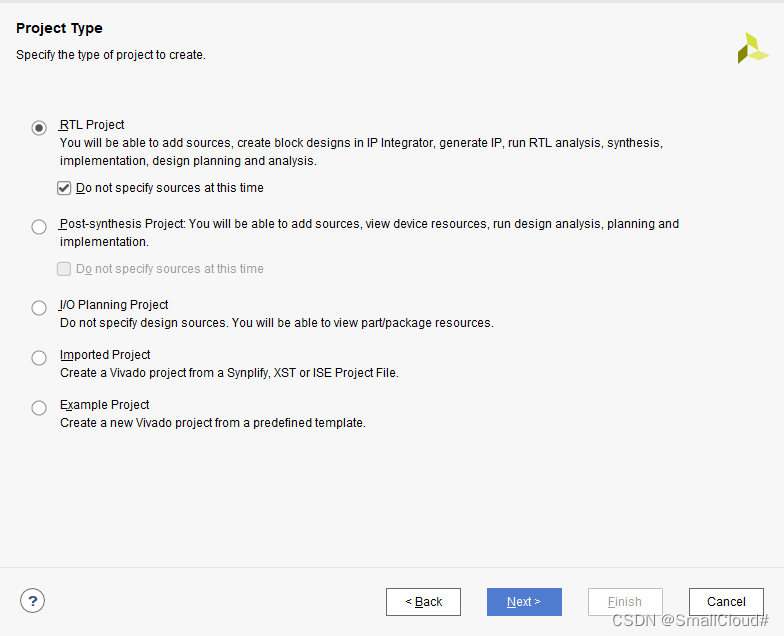

4、选择RTL project,勾选do not specify sources at this time表示不指定源文件,点击next

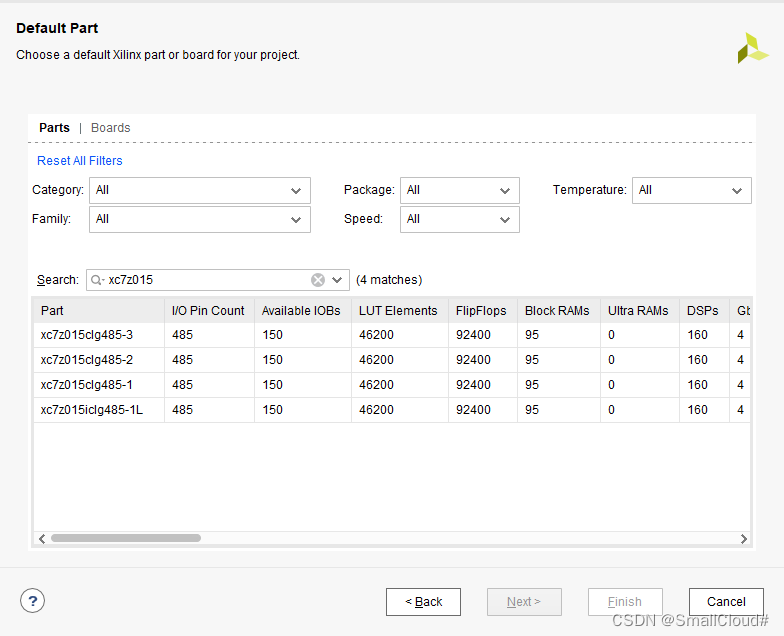

5、选择FPGA的型号后单击 next

可以通过上方的选项进行筛选,也可以直接输入型号进行搜索

6、单击Finish

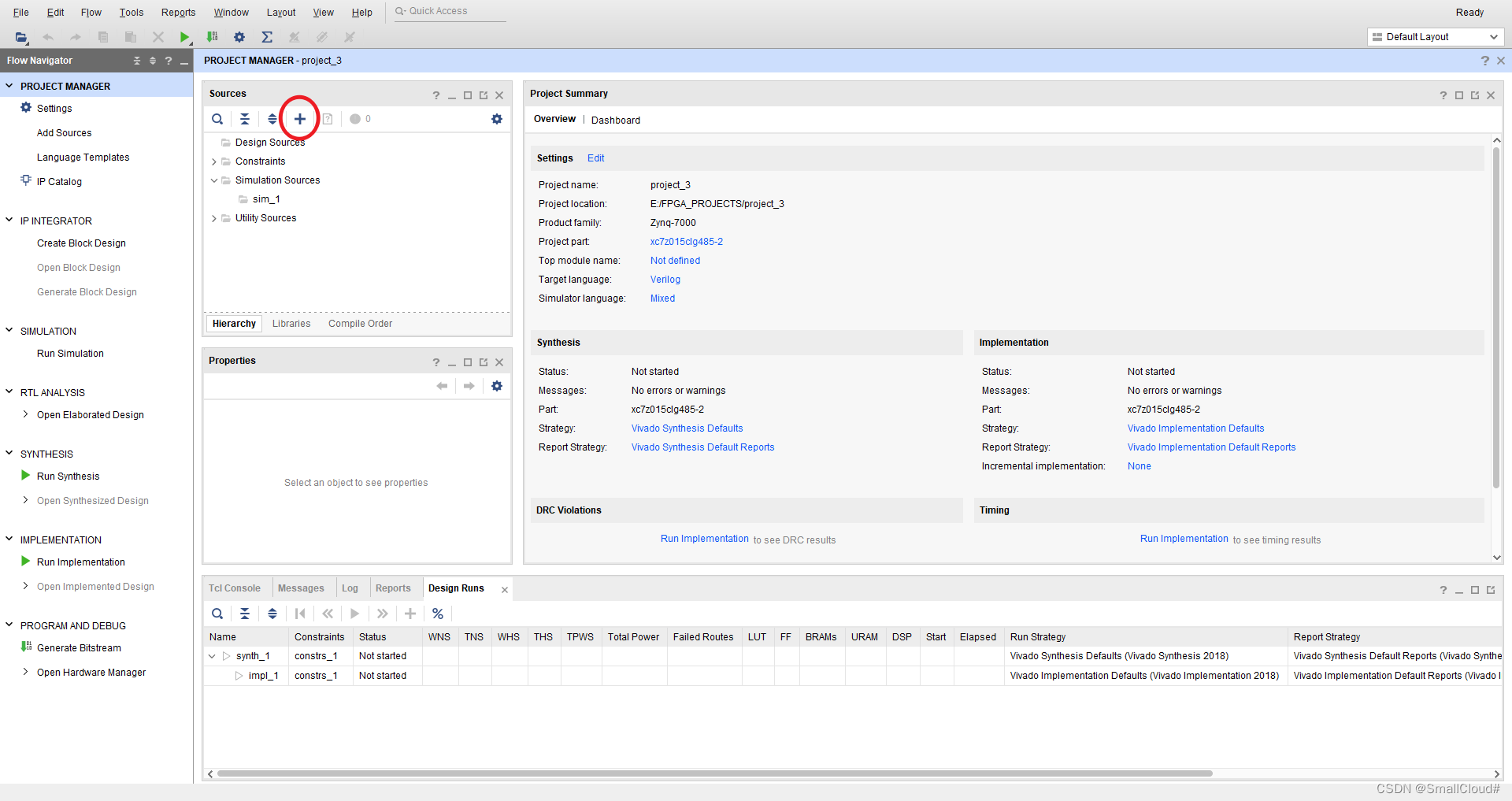

7、点击+添加新文件

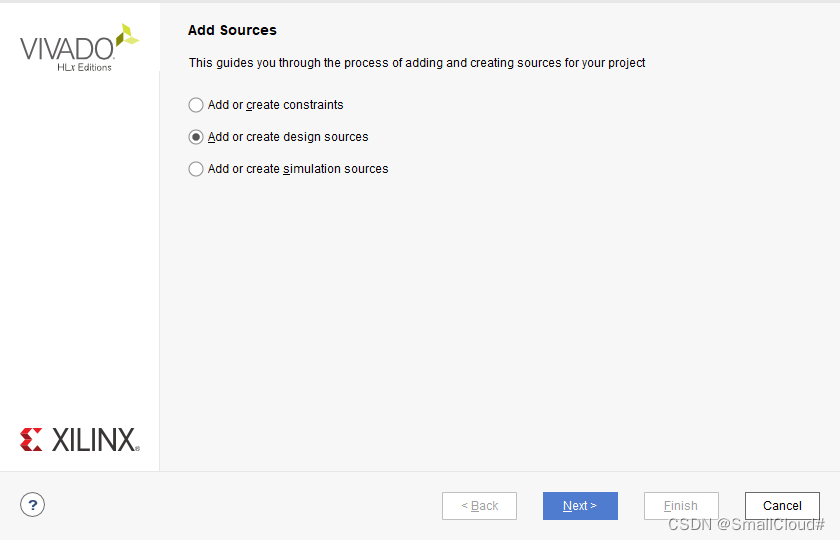

8、选择add or create design sources后单击NEXT

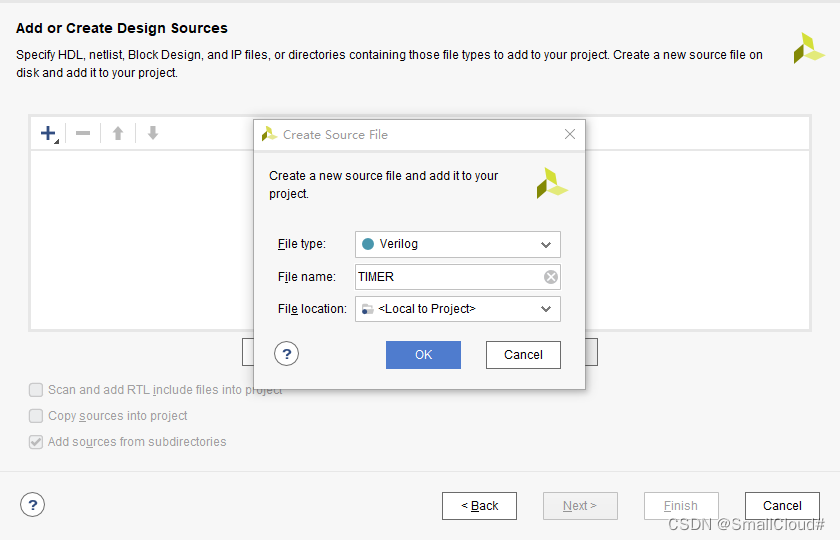

9、单击Create File,输入文件名XXX后点击OK

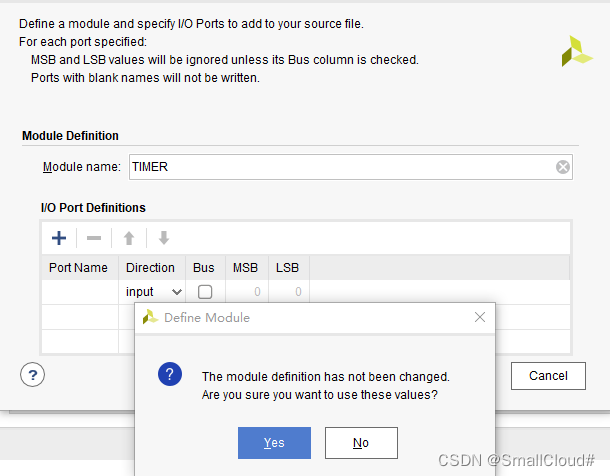

10、单击Finish —> 单击OK —>单击Yes

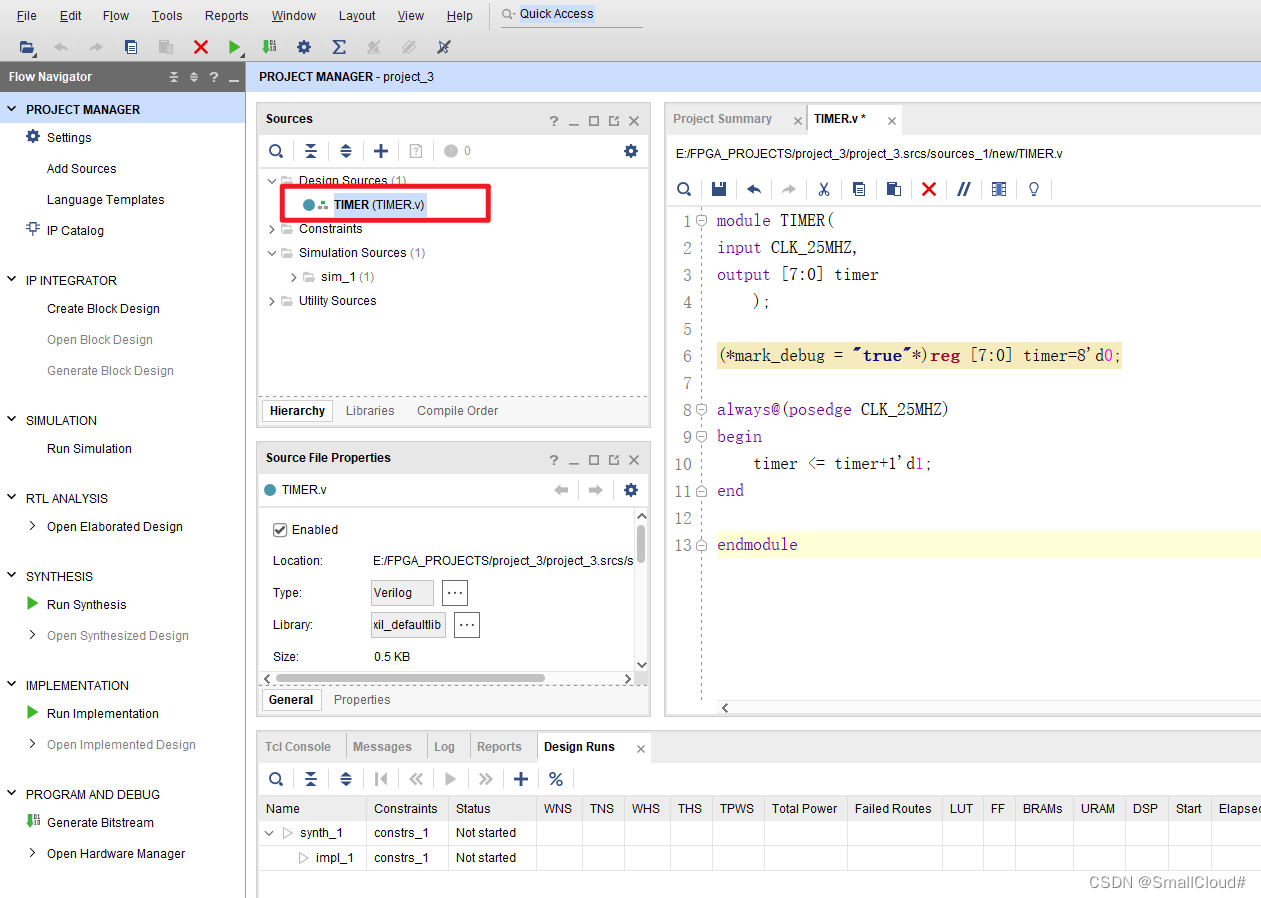

11、双击TIMER,输入代码保存

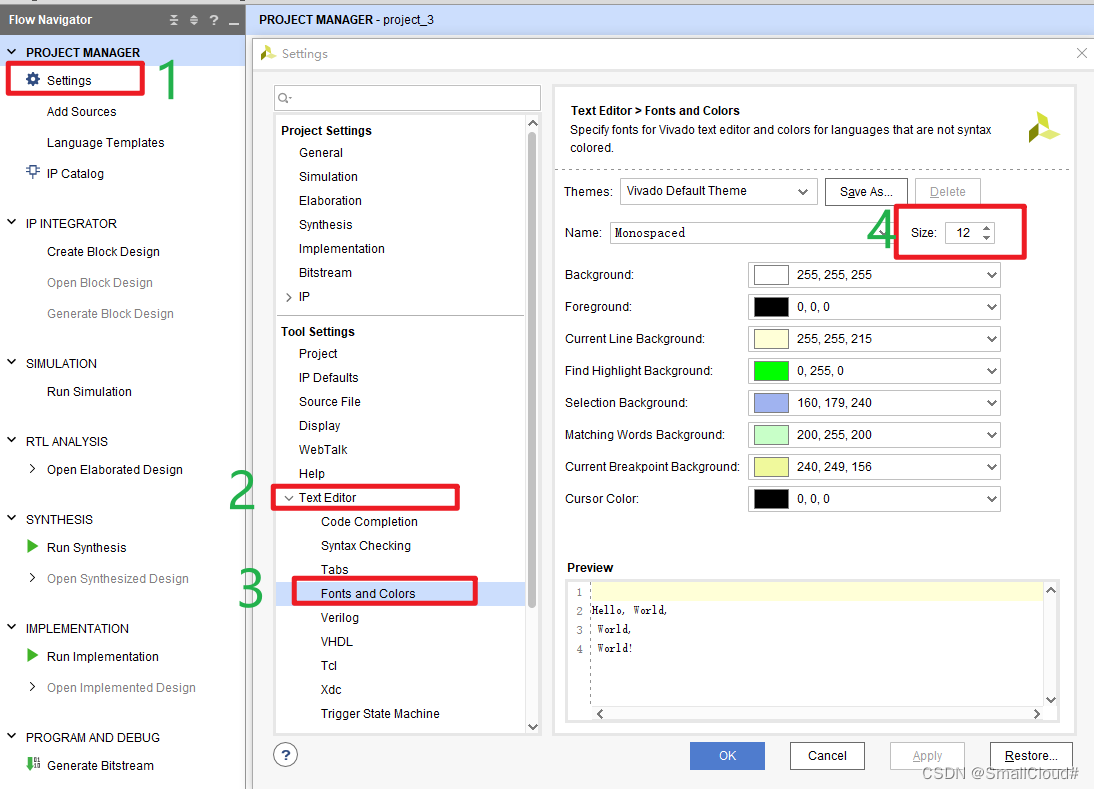

编辑器中字体太小的话可以通过设置修改字号:

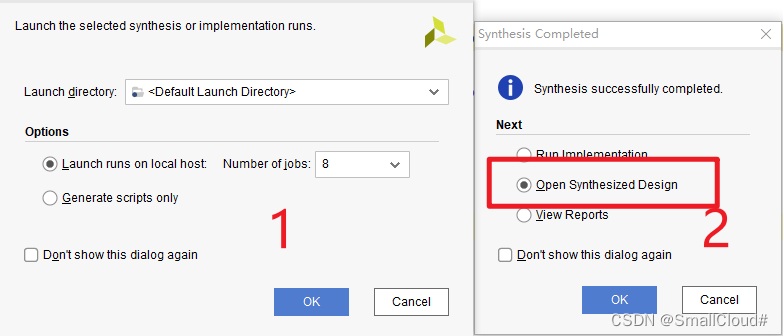

13、单击左侧的 Run Synthesis进行综合,单击OK后选择Open Synthesized Design,单击OK

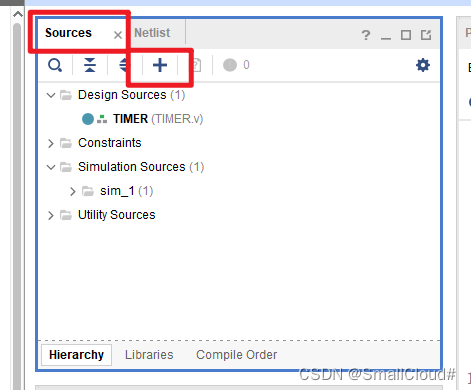

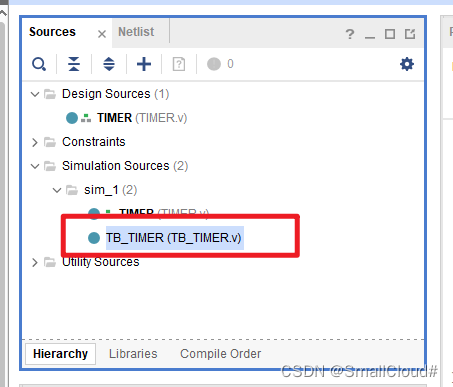

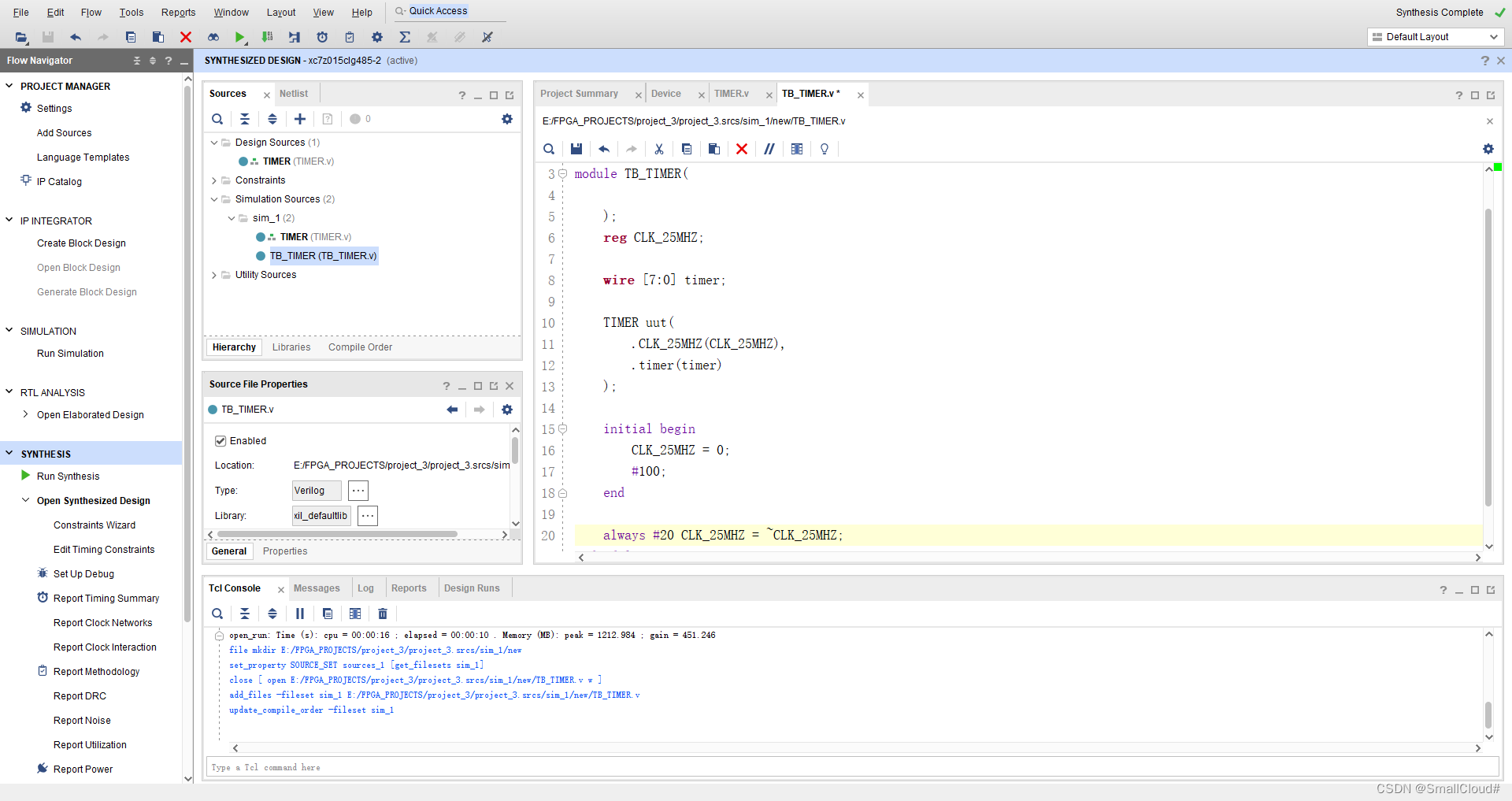

14、先单击Sources跳回源文件界面,然后单击+,添加仿真文件

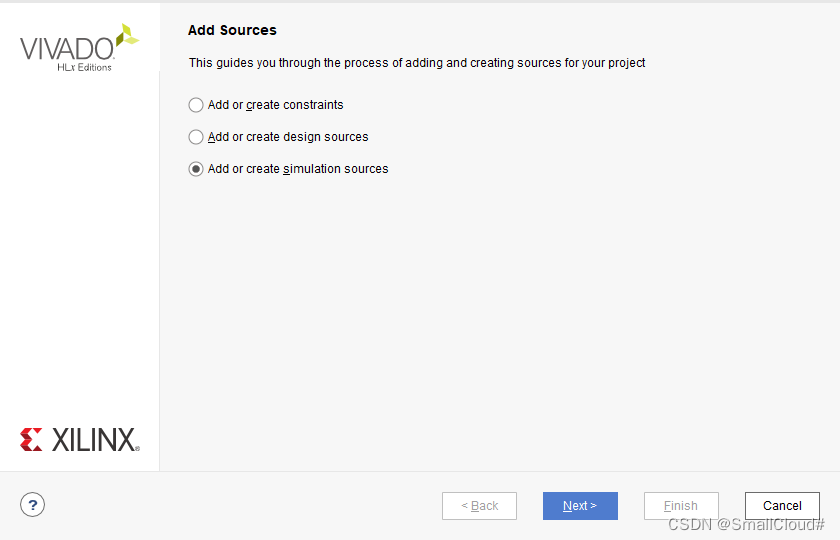

15、选择Add or create simulation sources后单击Next

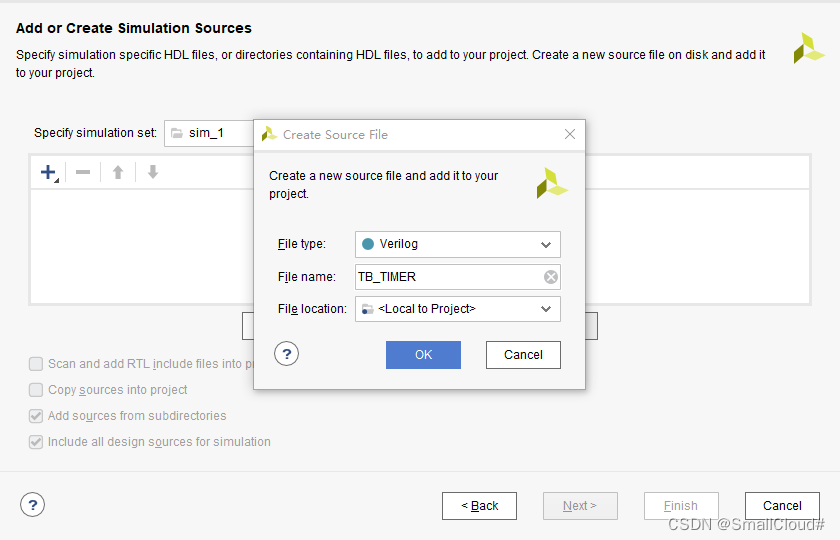

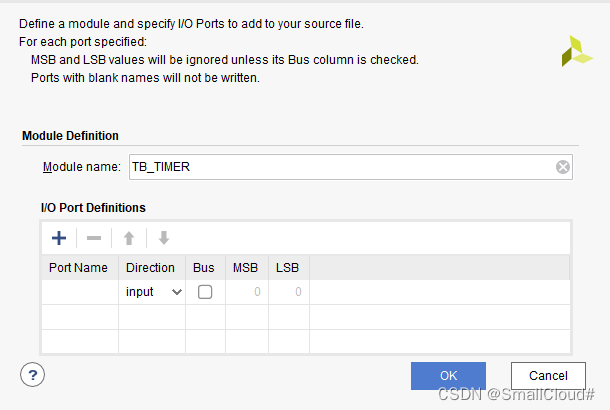

16、单击Create File后输入文件名,单击OK,单击Finish

单击OK,单击Yes

17、双击对应文件名打开文件

18、输入代码并保存(Ctrl+s)

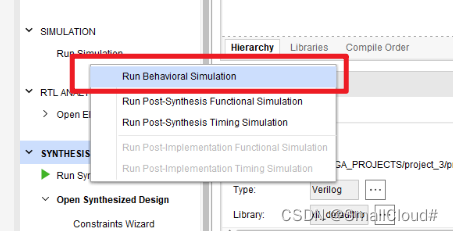

19、单击Run Simulation后选择Run behavioral Simulation,运行仿真

20、在调试窗口输入1ms后放大观察波形

可以看到每个时钟上升沿都会累加一,仿真正确21、关闭仿真界面,单击SYNTHESIS后在右上角选择I/O Planning

22、根据电路设计来约束引脚,完成后记得保存

23、单击OK,输入文件名后单击OK

24、单击左列的Setup Debug

25、弹出的窗口连续单击NEXT

26、保存刚刚监测信号的配置,单击OK

27、单击Generate Bitstream,创建比特流,进行综合、布局布线、生成bit文件

28、单击Yes,单击OK

29、弹窗选择View Reports,单击OK

30、单击Open Hardware Manager

为了调试和仿真,FPGA支持JTAG调试模式。JTAG(Joint Test Action Group,联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持 JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、 TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

- TCK–测试时钟输入

- TDI–测试数据输入,数据通过TDI输入JTAG口

- TDO–测试数据输出,数据通过TDO从JTAG口输出

- TMS–测试模式选择,TMS用来设置JTAG口处于某种特定的测试 模式

- 可选引脚TRST–测试复位,输入引脚,低电平有效

31、仿真器先连接FPGA板JTAG接口,然后连接电脑USB接口,FPGA上电

32、单击Open target,弹窗单击Auto Connect

33、单击Program device

34、单击Run trigger for this ILA core按钮触发

35、放大波形查看

36、关闭调试窗口

37、单击OK,FPGA下电,完成调试

-

相关阅读:

【python】python中字符串简单介绍及相关操作

项目运行没内容-----java.bug1

设计模式:什么是设计模式?①

4.提交表单数据

ZYNQ UltraScale MPSOC,使用PL端AXI_UART16550IP核,且在PS端控制下实现RS485通信-----轮询方式

2016 NIPS | Variational Graph Auto-Encoders

服务器向客户端推送消息之——WebSocket详细使用

视频理解【论文学习】

【苍穹外卖 | 项目日记】第二天

在VR全景中嵌入3D模型有哪些优势?

- 原文地址:https://blog.csdn.net/qq_45908742/article/details/125611535