-

SPI传输出现数据与时钟不匹配延后问题分析与解决

硬件环境

4G模块:FIBOCOM_AL940,基于MDM9628 CordX-A7 1.3 GHz单核,RAM 70M ROM 150M,包含两组spi接口,只能做主设备,最大支持50M时钟速率;

MCU单片机:RH850/F1K,包含两组spi接口,支持主从模式;从模式最大支持5M时钟速率;

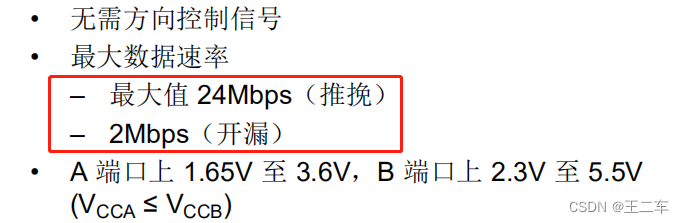

4G模块电源域1.8V,单片机3.3V电源域,中间使用TXS0104E和TXS0108E芯片转换电平;

4G模块做主模式,单片机做从设备,但由单片机发射数据到4G模块;

问题描述

在时钟速率2.4以下数据发送正常:0xaa 0x55

在3.2M以上就出现第二个字节数据与时钟不匹配,向后偏移了一个时钟bit位,最后一个bit高低位在时钟空闲时不会被改变:

通过直连数据线和时钟线,3.5M速率正常,但会大量丢失数据,单片机没有发送数据出来

时钟在4.8M时,时钟向后偏移一到三个随机的出现。

问题分析

1、怀疑电平转换芯片设置的模式不对导致最大数据速率问题,修改spi的4种模式无改善;

2、怀疑时钟和数据线的上下来电阻问题,修改尝试后无改善;

3、怀疑是4G模块数据采样导致的问题,断开数据线测量单片机端的数据管脚,无改善;

4、怀疑4G模块时钟芯片不标准导致,与IMX8的时钟进行对比,有细微差异,但波形符合手册要求;

5、单片机与IMX8连接是通信正常的,都是3.3V电平没有电平转换,通信的程序在4G模块通信就异常,单片机开发工程师表示程序一样没有改动,所以不是软件问题,结果只对比了spi代码,在对比单片机时钟代码发现了异常,倍频设置项有差异,4G模块默认使用EMCLK,IMX8使用PPLLOUT,这就导致了倍频的差异:

问题解决

单片机选择时钟源为PPLLOUT后,数据发送正常,5M速率下也正常,但后面测试还是有不同程度的丢包概率发生。

问题总结

涉及到硬件工程师,BSP工程师,单片机工程师,4G模块spi驱动开发工程师,单片机技术支持,最后发现是一个设置的问题,耗时几周才把这个简单的spi问题解决,确实汗颜啊。

-

相关阅读:

C++:array,模板特化 详解

RPA能和什么技术结合?

【Java21天挑战赛】多线程

浅析重复线性渐变repeating-linear-gradient如何使用

C Primer Plus(6) 中文版 第2章 C语言概述 2.1 简单的C程序示例

Python实现print输出至日志文件

【软件测试】一位优秀测试工程师具备哪些知识和经验?

自动化测试的生命周期是什么?

【Spring Boot】# 使用AOP实现接口鉴权访问、白名单限制、记录接口访问日志、限制接口请求次数

PlugLink:让数据分析与工作流无缝连接(附源码)

- 原文地址:https://blog.csdn.net/TSZ0000/article/details/125905639