-

TD联合Modelsim进行功能仿真

1 引言

最近在接触使用国产安路科技公司的FPGA进行相关的开发,TD(Tang Dynasty)作为一款安路FPGA开发工具与Quartus 使用大致相同,但仍旧有一定的不同。

2 基本配置流程

这里推荐以官方使用手册作为参考进行实践,首先需要完成TD软件内部的操作。

2.1 TD软件设置操作

1. Process ⇒ \Rightarrow ⇒ Properties ⇒ \Rightarrow ⇒ Optimize RTL :

rtl_sim_model : ON

2. Process ⇒ \Rightarrow ⇒ Properties ⇒ \Rightarrow ⇒ Optimize Gate :

gate_sim_model : ON

3. Process ⇒ \Rightarrow ⇒ Properties ⇒ \Rightarrow ⇒ Optimize Routing :

phy_sim_model : ON

4. Process ⇒ \Rightarrow ⇒ Properties ⇒ \Rightarrow ⇒ Timing Option :

sdf : ON

5.设置相关仿真参数

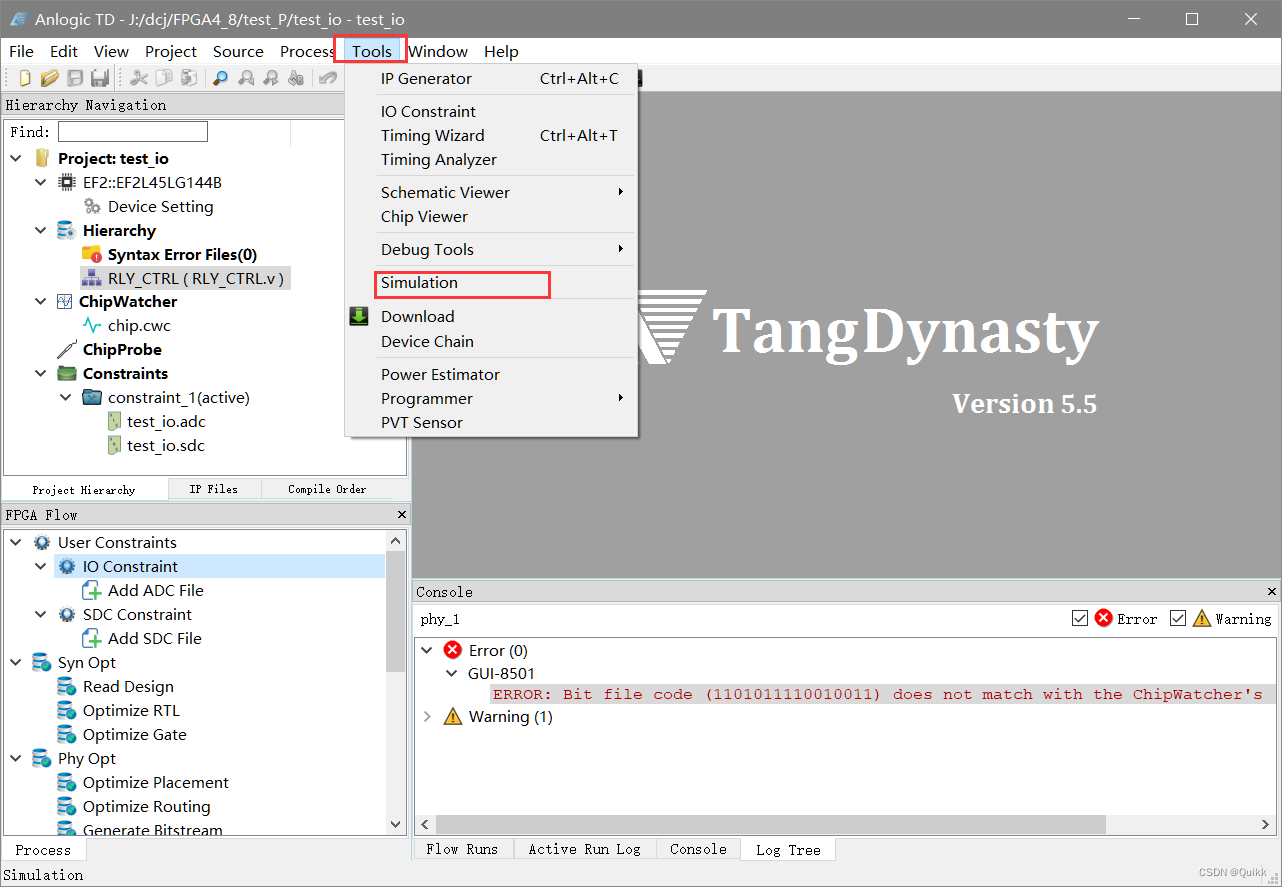

6.运行Simulation

7.选择相关测试文件(testbench文件)

这里有两种方式,第一种是添加已经存在的tb文件进行测试;第二种是新建一个新的测试文件。

8.完成上述步骤之后会生成两个文件:①testbench文件 ②脚本文件do文件。

完成这些步骤之后,TD软件这边的设置便已经完成,下面需要完成Modelsim软件方面的设置。

2.2 Modelsim软件方面设置

-

首先进入TD安装目录,在改目录下有一个文件夹为sim_release的文件,文件夹下是一些对应芯片的仿真文件,因为这里使用的芯片为EF2L45LG144B。所以仅复制EF2文件夹下的相关文件。(这里一定要注意根据芯片类型选择复制的文件夹)

-

在Modelsim安装根目录下新建一个文件夹(Anlogic),将刚才复制的EF2文件夹复制进新建的Anlogic >> src文件夹内。此时src文件夹内便存放着大量该芯片的仿真文件。

- 打开Modelsim,File ⇒ \Rightarrow ⇒ Change Directory ⇒ \Rightarrow ⇒ 修改当前目录为刚创建的Modelsim根目录下的Anlogic文件夹。

-

File ⇒ \Rightarrow ⇒ New ⇒ \Rightarrow ⇒ Library ⇒ \Rightarrow ⇒ 新建安路仿真库。库名字设置为EF2_ver。

5.Compile ⇒ \Rightarrow ⇒ Compile ⇒ \Rightarrow ⇒ 编译新库

6.回到TD软件,设置Lib,重新进行Simulation。

-

将TD工程目录下的tb文件和原始Verilog文件进行拷贝到modelsim根目录Anlogic文件夹下的新建文件夹内,作为工程文件。

8.在Modelsim中新建工程文件

9.为工程加入测试文件

10.加入文件后进行编译,编译之前一定要对tb文件进行初值的幅值与修改。即修改initial语句中的定义部分。

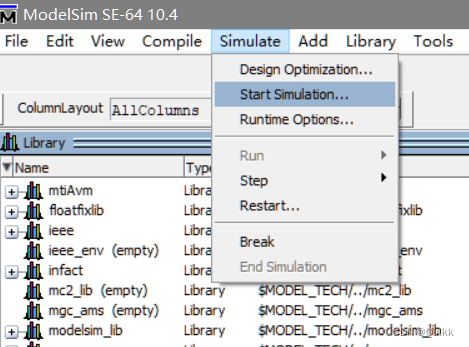

11.启动仿真,设置仿真文件,加入仿真库

12.仿真结果

-

-

相关阅读:

Python3,我用这种方式讲解python模块,80岁的奶奶都说能理解。建议收藏 ~ ~

YashanDB发布会圆满收官,V23.1三大新品引领国产数据库技术与应用突破!

分布式学习必看:十年架构大佬带你从零开始学习分布式服务框架!

antd-design-vue Table组件全局配置(分页器...)

什么是数字货币、数字金融 和区块链?

跨站请求伪造(CSRF)攻击与防御原理

Photoshop与Web技术完美融合,Web版Photoshop已正式登场

做个清醒的程序员之破解内卷漩涡

BeanUtils.copyProperties的使用场景

SpringBoot:CORS是什么?SpringBoot如何解决跨域问题?

- 原文地址:https://blog.csdn.net/qq_42151264/article/details/125527778