-

门级建模—课后习题

习题

-

利用双输入端的nand门,用Verilog编写自己的与或非门,并用激励模块验证这些门的功能。

-

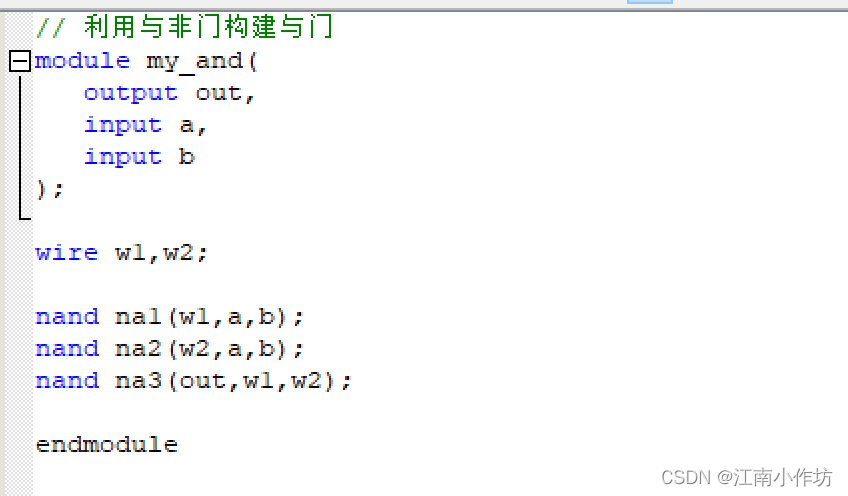

与门,verilog实现,用三个与非门

-

RTL视图

-

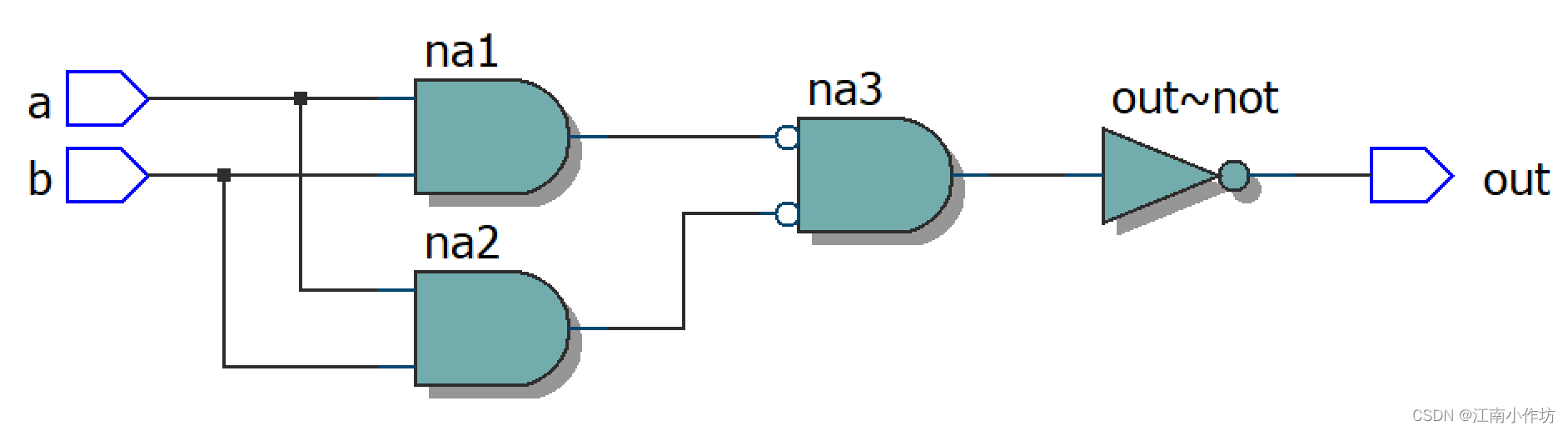

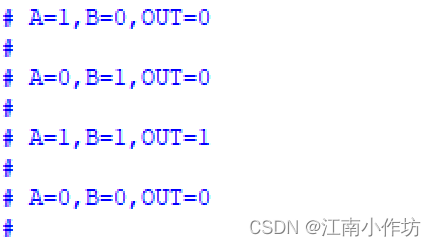

仿真实现

-

仿真结果满足与门逻辑。

-

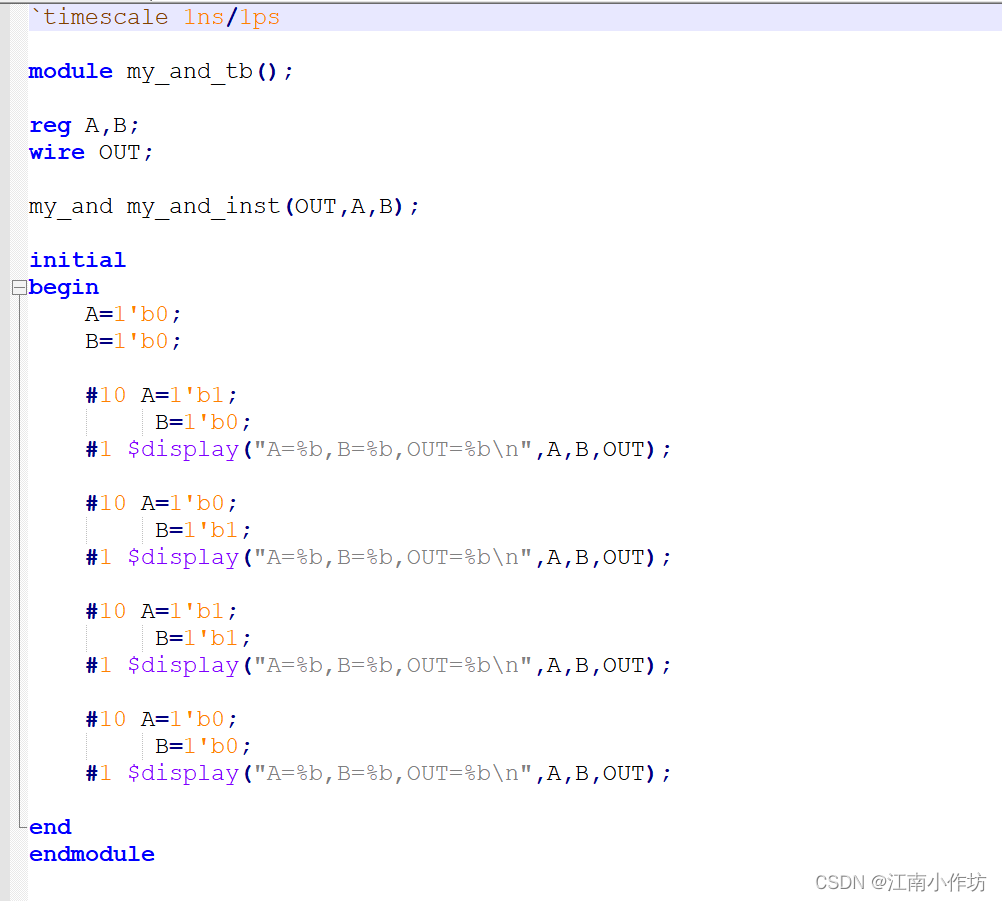

与门(第二种方式),Verilog实现,两个与非门

module my_and( output out, input a, input b ); wire w1; nand na1(w1,a,b); nand na2(out,w1,w1); endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

-

RTL视图

-

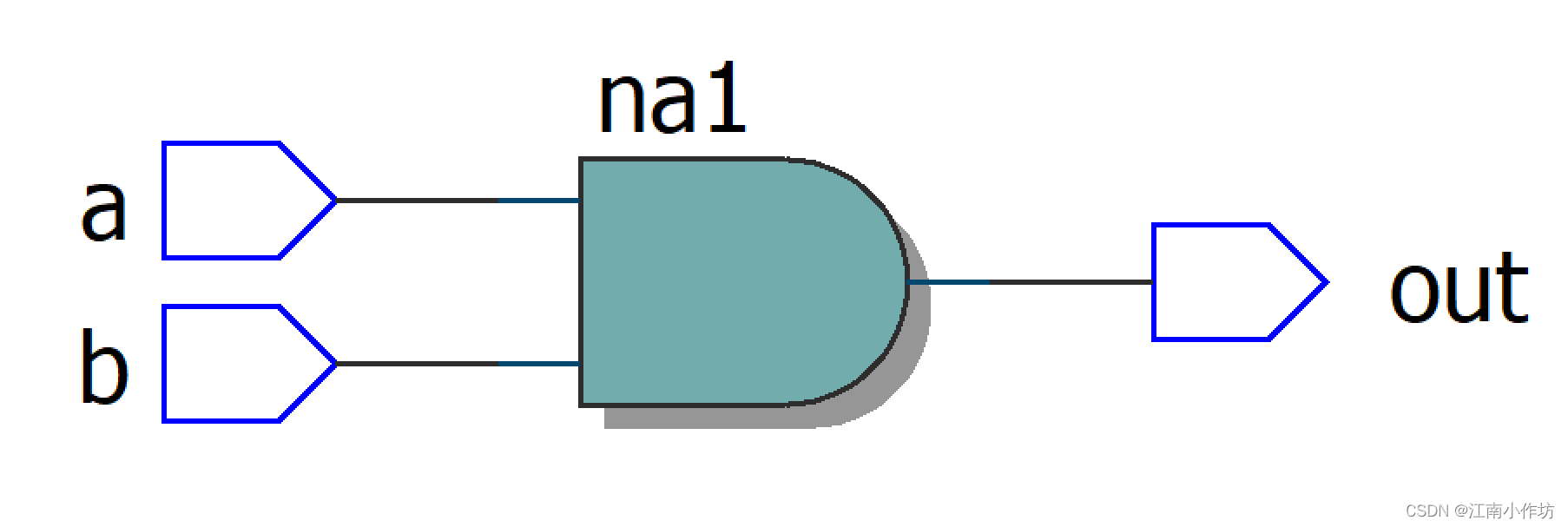

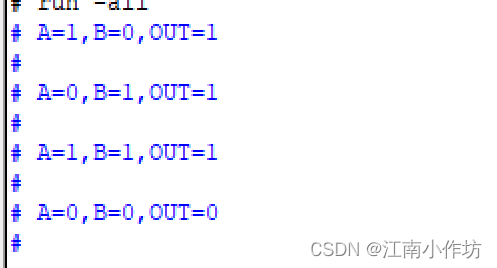

仿真结果

-

或门,verilog实现

//构建或门 module my_or( output out, input a, input b ); //输入短接 wire w1,w2; nand (w1,a,a); nand (w2,b,b); nand (out,w1,w2); endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

-

仿真验证

-

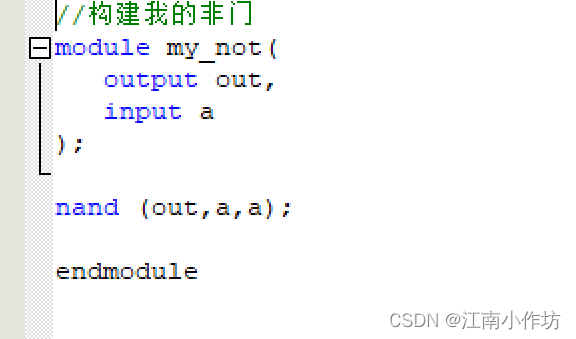

非门,就很简单啦,把与非门输入短接就行啦,就不一一验证了。本来不想写my_not的,结果第二题要用到,贴上其代码。

-

-

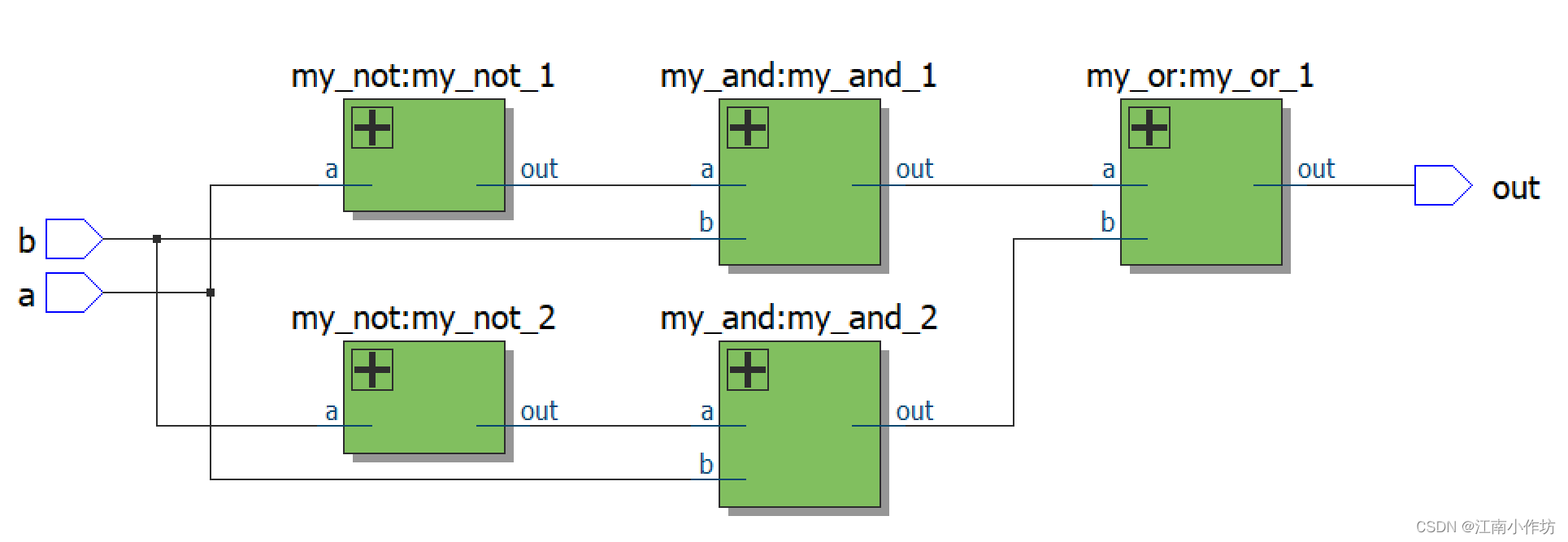

利用上题所定义的my_and,my_or,my_not,来构建一个异或门(xor),功能计算 z = x ˉ y + x y ˉ z=\bar{x}y+x\bar{y} z=xˉy+xyˉ,编写仿真信号对其测试。

-

verilog实现

//综合my_and,my_or,my_not module my_xor( output out, input a, input b ); //声明内部线网 wire w1,w2,w3,w4; my_not my_not_1(w1,a); my_not my_not_2(w2,b); my_and my_and_1(w3,w1,b); my_and my_and_2(w4,w2,a); my_or my_or_1(out,w3,w4); endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

-

RTL视图

-

仿真设计

// 仿真定义 module my_xor_tb(); reg x,y; wire z; my_xor my_xor_inst(z,x,y); initial begin x=1'b0; y=1'b1; #10 x=1'b0; y=1'b0; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b0; y=1'b1; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b1; y=1'b0; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); #10 x=1'b1; y=1'b1; #1 $display("x=%b,y=%b,z=%b\n",x,y,z); end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

-

仿真结果,满足异或门逻辑

-

-

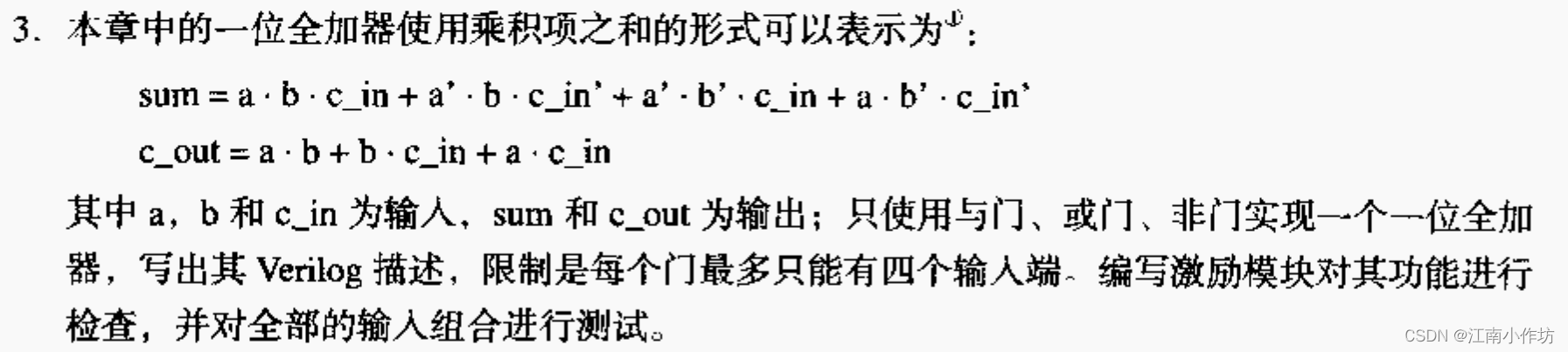

懒得打字拉,题目如下:

-

Verilog实现

module my_fulladder( output sum, output c_out, input a, input b, input c_in ); wire a_1, b_1, c_in_1; wire s1, s2, s3, s4; wire c1, c2, c3; // 先实现等式中的非门,且用上面定义的线网连接 not (a_1, a); not (b_1, b); not (c_in_1, c_in); // 实现等式中的sum and (s1,a,b,c_in); and (s2,a_1,b,c_in_1); and (s3,a_1,b_1,c_in); and (s4,a,b_1,c_in_1); or (sum,s1,s2,s3,s4); // 实现等式中的c_out and (c1,a,b); and (c2,b,c_in); and (c3,a,c_in); or (c_out,c1,c2,c3); endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

-

RTL视图

-

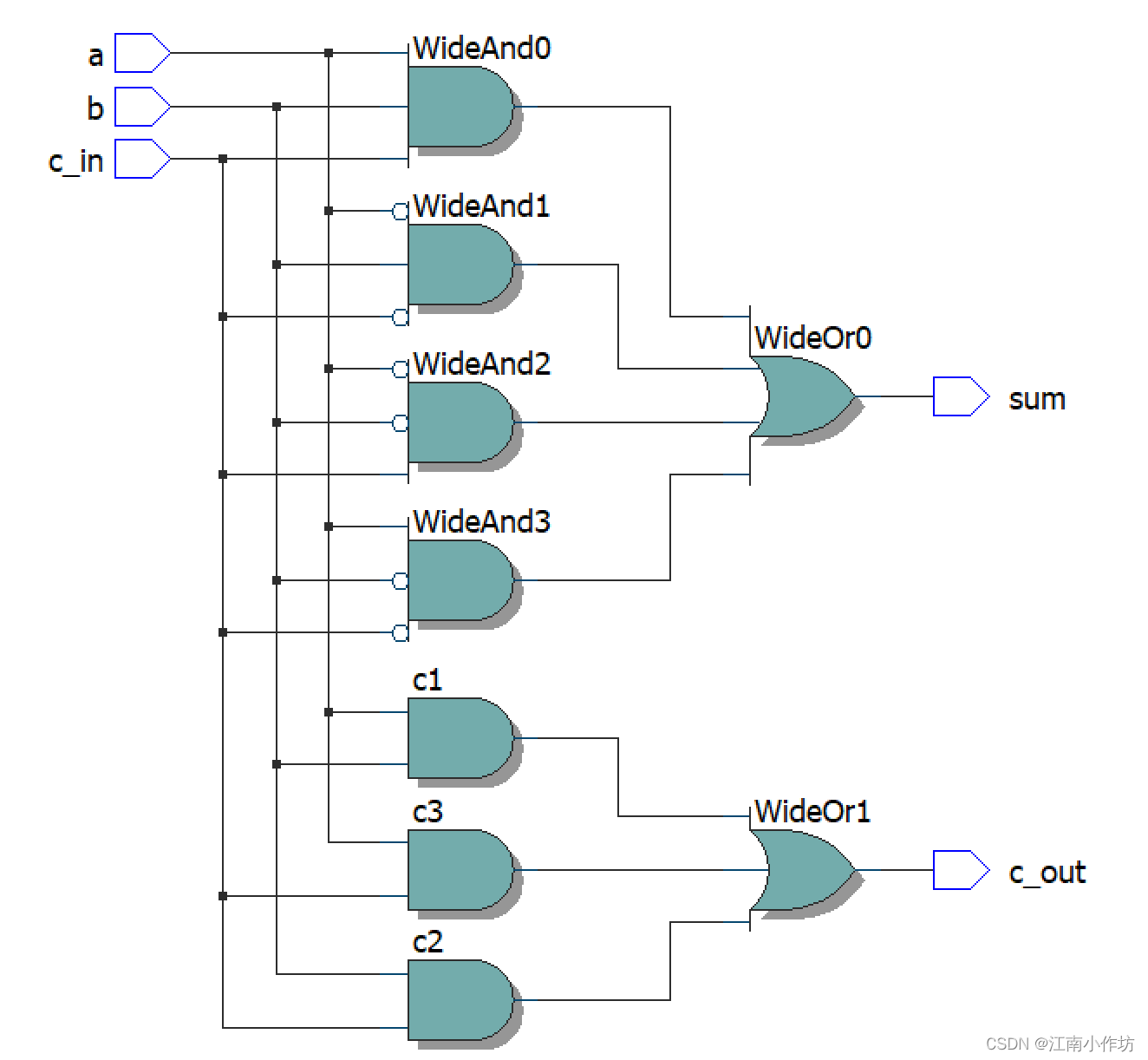

仿真实现

module my_fulladder_tb(); reg A,B,C_IN; wire C_OUT,SUM; my_fulladder my_fulladder_inst(SUM, C_OUT, A, B, C_IN); initial begin A = 1'b0; B = 1'b0; C_IN = 1'b0; #10 A = 1'b0; B = 1'b0; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b1; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b1; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b0; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b0; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b1; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b1; B = 1'b1; C_IN = 1'b1; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); #10 A = 1'b0; B = 1'b0; C_IN = 1'b0; #1 $display("A=%b,B=%b,C_IN=%b,SUM=%b,C_OUT=%b\n", A, B, C_IN, SUM, C_OUT); end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

-

仿真结果,满足设计要求

-

-

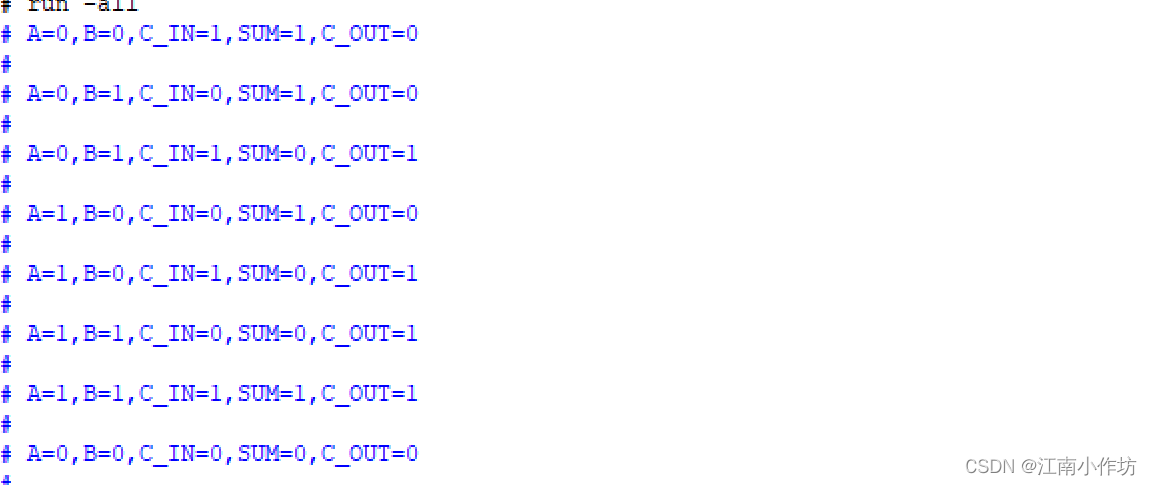

直接上图

-

上图

-

-

相关阅读:

SpringMVC学习笔记

Single View Metrology 单视图度量衡 复现

【洛谷 P5250】【深基17.例5】木材仓库 题解(集合+upper_bound)

纷享销客数字化营销能力(三):全渠道获客

Elasticsearch脑裂

Java并发Map的面试指南:线程安全数据结构的奥秘

【PCBA方案】电子握力测试仪方案she‘ji

Google Cloud dataflow streaming job简介

YOLOv5算法进阶改进(5)— 主干网络中引入SCConv | 即插即用的空间和通道维度重构卷积

RK3399 Android7.1修改安兔兔等第三方软件读到的内核版本信息

- 原文地址:https://blog.csdn.net/Cherish1ove/article/details/125493224